QPSK载波同步算法FPGA实现与性能分析

需积分: 36 189 浏览量

更新于2024-09-12

2

收藏 529KB PDF 举报

"QPSK载波同步算法的FPGA实现及锁相环参数设计"

在无线通信系统中,载波同步是至关重要的一个环节,它确保接收到的信号能够正确解调。QPSK(Quadrature Phase Shift Keying,正交相移键控)是一种常见的数字调制方式,通过改变载波信号的相位来传输信息。QPSK载波同步算法主要关注如何在接收端恢复发送端的载波频率和相位,从而精确地解调信号。

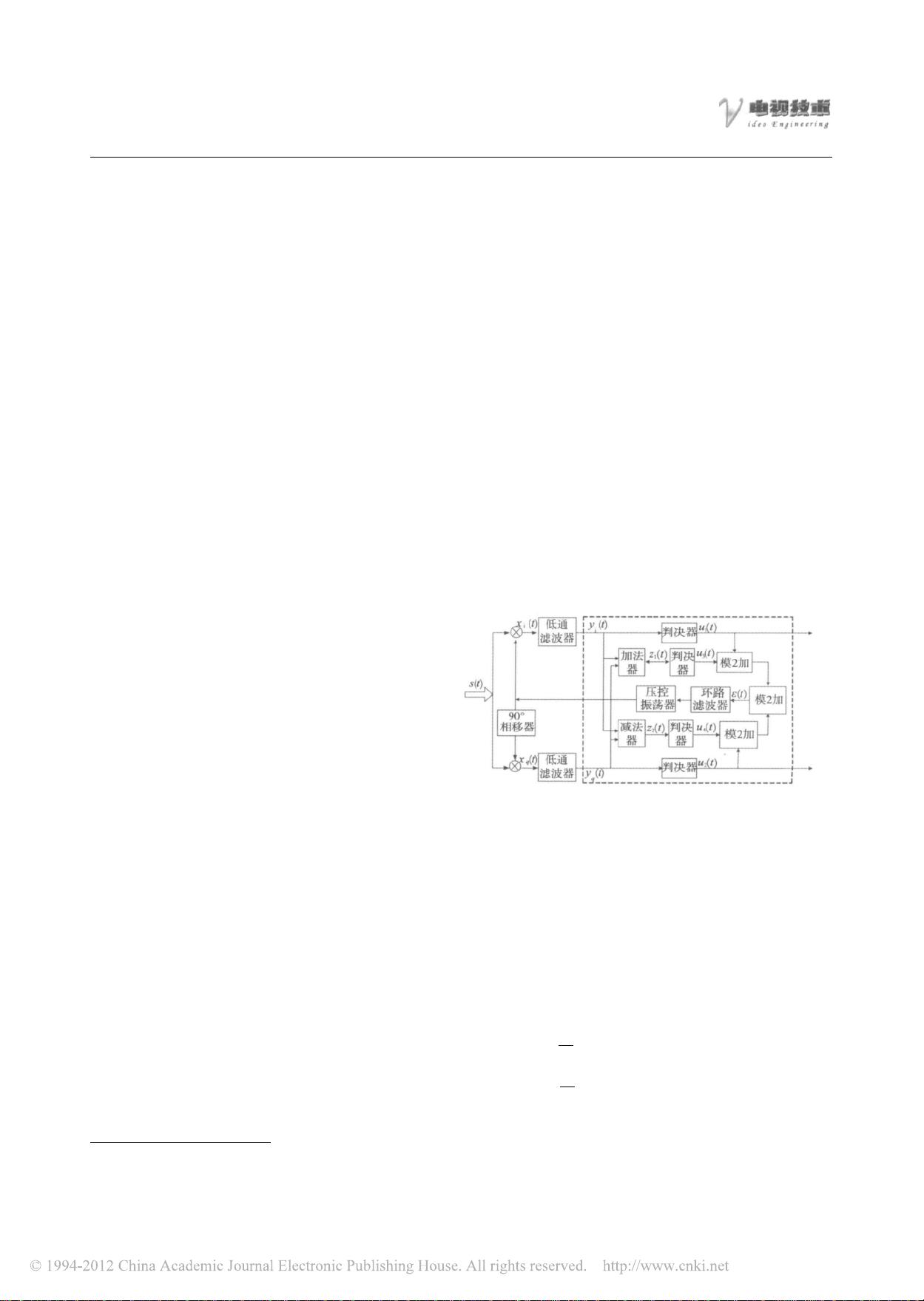

本文由赵秋明、孙志磊和欧阳宁共同研究并发表于《电视技术》2012年第36卷第11期,探讨了基于工程应用的四相松尾环(Matsuoka Loop)实现QPSK载波恢复的算法,并分析了噪声对算法性能的影响。松尾环是一种常用的载波同步环路结构,适用于QPSK等MPSK(Multiple Phase Shift Keying,多相移键控)调制方式。

在FPGA(Field-Programmable Gate Array)上实现QPSK载波同步,首先需要理解锁相环(Phase-Locked Loop,PLL)的工作原理。锁相环是一种闭环控制系统,其核心组成部分包括鉴相器、环路滤波器和压控振荡器。鉴相器比较输入的参考信号(通常是已知的本地载波)和经过解调后的接收信号的相位差,环路滤波器处理鉴相器的输出,滤除高频噪声并提供控制电压给压控振荡器,使得振荡器的频率逐渐接近输入信号的频率。

松尾环是锁相环的一种变体,特别适合在低信噪比(SNR)环境下工作。文章中提到,实验结果表明,即使在小信噪比的情况下,采用松尾环也能实现良好的载波同步效果。此外,由于其结构特性,这种算法可以方便地扩展到更复杂的MPSK调制系统中。

SystemGenerator是Xilinx公司的工具,用于在FPGA设计中实现数学模型和算法。在本文中,作者利用SystemGenerator设计并实现了松尾环和环路滤波器,这一方法大大简化了硬件实现过程,并提供了可配置的参数,以适应不同的系统需求。

关键词:正交相移键控、环路滤波器、载波同步、SystemGenerator、FPGA。这些关键词反映了文章的主要研究内容和技术焦点,即QPSK调制下的载波同步算法设计,特别是利用FPGA硬件平台进行实现,并结合SystemGenerator工具优化参数设计。

QPSK载波同步算法的FPGA实现涉及了通信理论、数字信号处理以及嵌入式系统设计等多个领域。通过研究和实践,可以实现高效、鲁棒的载波同步系统,提高通信系统的整体性能。

2023-07-27 上传

2022-03-25 上传

2021-07-13 上传

2021-07-13 上传

2022-09-20 上传

2021-07-13 上传

2023-03-30 上传

2022-06-23 上传

xq5205233

- 粉丝: 1

- 资源: 6

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南