FPGA开发详解:ISE10.1使用步骤与技巧

需积分: 10 91 浏览量

更新于2024-10-12

收藏 1022KB DOC 举报

"这篇教程详细介绍了如何使用FPGA开发软件ISE进行项目开发,包括从创建工程、编写HDL代码、进行行为仿真到生成bit流文件并下载到硬件板上进行调试的全过程。教程以ISE 10.1版本为例,但同时也提到了与9.1版本的不同之处。"

在FPGA开发中,Xilinx ISE是一款重要的集成开发环境,它支持VHDL和Verilog等硬件描述语言。以下是对该教程中涉及知识点的详细说明:

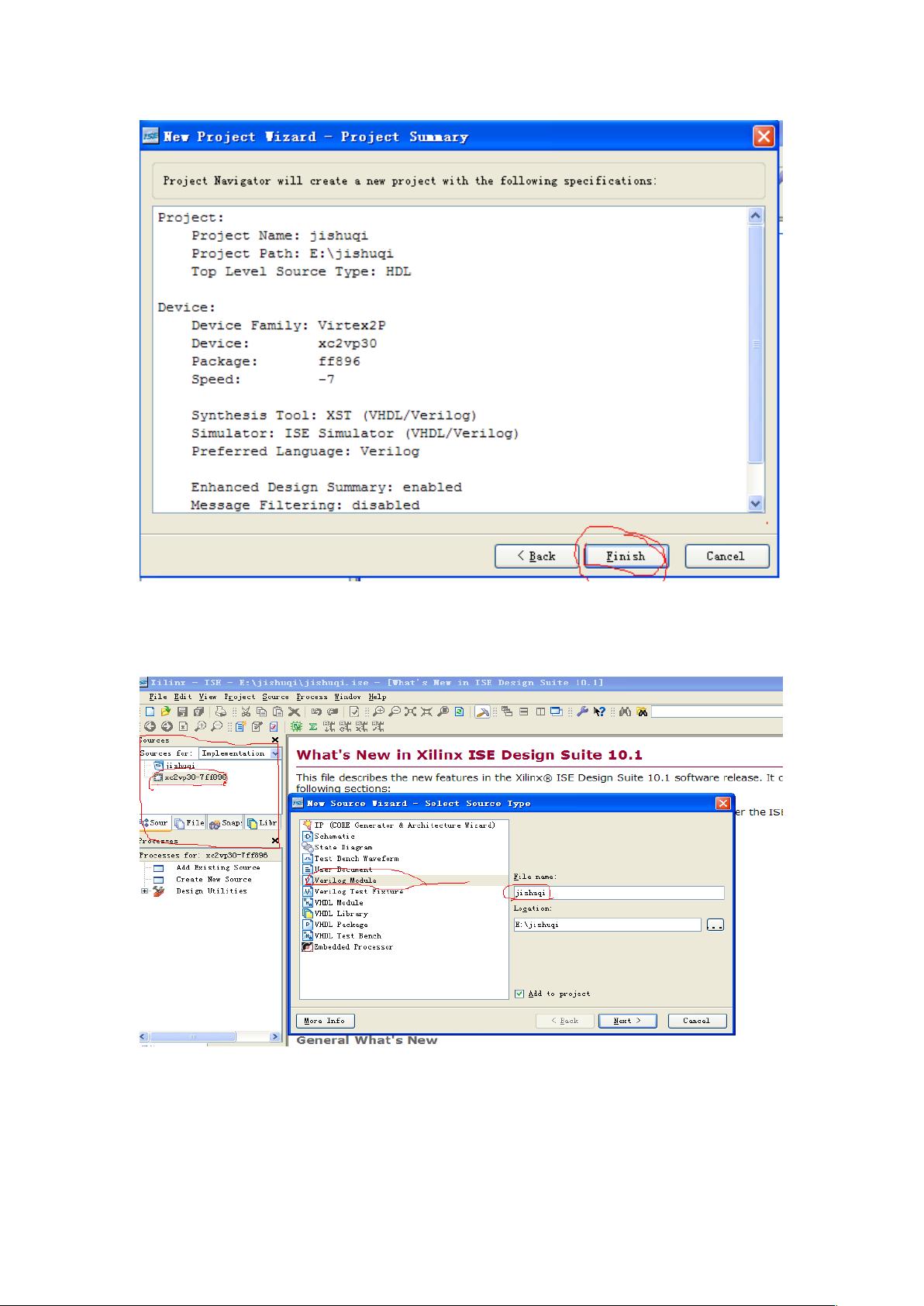

1. **创建工程**

- 工程命名:在“File”菜单中选择“New Project”,并指定工程名称和选择资源类型为HDL。

- 器件选择:在后续步骤中,需要选择合适的FPGA家族、器件型号、封装和速度等级,以匹配实际使用的开发板。

2. **编写HDL代码**

- 在“Sources”区域右键新建源文件,选择相应的语言(VHDL或Verilog)。

- 代码编写:教程中展示了编写一个简单的十进制计数器的例子,包括输入输出定义、状态变量声明和状态更新逻辑。

3. **行为(功能)仿真**

- 添加仿真源:通过在“Sources”区域右键添加新的仿真源,选择图形仿真文件(通常为VHDL或Verilog Testbench)。

- 时钟设置:设置仿真时钟的上升沿、频率、电平持续时间和仿真时间,以便观察信号变化。

4. **综合(Synthesis)**

- 在完成功能仿真并确认代码无误后,需要进行综合步骤,将高级语言描述转化为硬件逻辑门级表示。

5. **管脚约束(Constraints)**

- 管脚约束定义了设计中的信号如何连接到FPGA的实际引脚,这一步骤确保了设计与硬件的匹配。

6. **实现(Implementation)**

- 实现阶段将综合后的门级网表转化为具体电路布局和布线,优化性能和资源使用。

7. **时序仿真(Timing Simulation)**

- 检查设计在实际运行速度下的性能,确保满足时序要求。

8. **生成bit流文件(Bitstream Generation)**

- 通过以上步骤,最终生成的bit流文件包含了FPGA配置的所有信息。

9. **下载与调试**

- bit流文件通过JTAG或SPI接口下载到FPGA中,然后在硬件板上进行实际操作和调试。

教程特别指出,不同版本的ISE可能在界面或选项上有细微差别,如ISE 10.1与9.1的差异,但基本流程和概念保持一致。对于初学者来说,理解并掌握这些步骤是成功开发FPGA项目的关键。通过这样的教程,学习者可以逐步熟悉整个FPGA设计流程,提升自己的实践能力。

2014-07-12 上传

点击了解资源详情

2020-08-13 上传

2010-06-29 上传

2010-04-06 上传

2023-04-05 上传

2021-10-03 上传

2022-02-08 上传

2021-09-20 上传

ccxncu2010

- 粉丝: 2

- 资源: 44

最新资源

- 单片机串口通信仿真与代码实现详解

- LVGL GUI-Guider工具:设计并仿真LVGL界面

- Unity3D魔幻风格游戏UI界面与按钮图标素材详解

- MFC VC++实现串口温度数据显示源代码分析

- JEE培训项目:jee-todolist深度解析

- 74LS138译码器在单片机应用中的实现方法

- Android平台的动物象棋游戏应用开发

- C++系统测试项目:毕业设计与课程实践指南

- WZYAVPlayer:一个适用于iOS的视频播放控件

- ASP实现校园学生信息在线管理系统设计与实践

- 使用node-webkit和AngularJS打造跨平台桌面应用

- C#实现递归绘制圆形的探索

- C++语言项目开发:烟花效果动画实现

- 高效子网掩码计算器:网络工具中的必备应用

- 用Django构建个人博客网站的学习之旅

- SpringBoot微服务搭建与Spring Cloud实践