Integer Linear Programming Based Fault-Tolerant

Topology Synthesis for Application-Specific NoC

Zhigang Li, Jinglei Huang, Qi Xu and Song Chen

∗

Department of Electronic Sci. & Tech., University of Science and Technology of China, Hefei 230027, China

∗

Email: songch@ustc.edu.cn

Abstract—In nano era, fault tolerance has become a significant

challenge for IC designers. Even a single link failure on NoC

can halt communication between application modules, which

makes the entire chip lose efficacy. In this paper, considering link

failures, we propose an integer linear programming (ILP) based

method to generate K fault-tolerance topologies for application

specific NoCs (ASNoC). Compared with the FTTG method,

which can generate only one-link failure tolerance topologies,

the proposed mehtod show better energy efficiency and average

hops, and can scale upward to generate K (K > 1) link fault-

tolerance topologies.

I. INTRODUCTION

As an increasing number of processing elements (PEs) has

been integrated on a single chip, a variety of interconnection

schemes have been proposed, including crossbars, rings, buses,

and Network-on-Chip (NoC) [1]. The packet switching based

NoC is considered a promising solution to the interconnection

challenges of future SoC designs [2]. It is scalable and

has been widely utilized to decouple communication from

computation, thus improving performance.

However, the fast scaling in technology has caused rapid

increasing of the probability of facing faults in different NoC

components [3] while the reliability of a NoC is critical to

guarantee the reliability of communication. Even a single link

failure on NoC can halt communication between application

modules, which makes the entire chip lose efficacy.

NoC architecture consists of regular or irregular topolo-

gies. Compared to regular topologies, irregular topologies

are fitter for designing application-specific NoCs because of

low energy consumption, low area overhead, etc. [4]. There

are many works addressing the synthesis of the application-

specific NoC topologies [5]–[8]. However, these works seldom

consider fault tolerance in the NoC topologies. Especially,

the application specific NoCs have low path diversity and

could not work normally if any hardware faults occur such as

routers or links. In [9], a fault tolerant NoC architecture was

proposed with cores linked to two switches instead of one and

a dynamically reconfigured routing algorithm is used to escape

faulty switches. K.-C. Chang et al. [10] proposed a fault-

tolerant topology generation (FTTG) method for application-

specific NoC, which focuses on permanent link and router

port failures. The authors tried to add a minimum number of

extra routers and links to ensure that each router and link must

be on a cycle, which provides at least two alternative routing

paths to achieve fault-tolerance capability. The NoC topologies

are generated in two phases. In the first phase, the links

between the routers (router topology) are constructed and, in

the second phase, the links from cores to routers are built (core

mapping). However, the router topology and the core mapping

strongly depend on each other and, consequently, it is difficult

for FTTG method to effectively explore the design space

of the network topologies. Additionally, the FTTG can only

generate one-failure tolerant topologies and cannot be applied

to generating multiple-fault tolerant network topologies.

Motivated by the above argument, we propose an ILP based

method for generating multiple link-faults tolerant application-

specific topology. To generate K link-faults tolerant topologies,

we build an ILP model to simultaneously solve the router

topology generation and core mapping problem by finding

K + 1 alternative link-disjoint communication paths for each

communication flow. If there is a link failure, we can choose

another alternative path to replace the path including the link

failure. Because of K +1 alternative communication paths, the

generated topology can tolerate K link faults.

The remainder of this paper is organized as follows. Section

II formulates the K-fault-tolerant application-specific NoC

topology generation problem. In Section III, we describes the

overview of the proposed framework in III-A and present

our K-fault-tolerant topology generation methodology in III-C.

The experimental results are provided in Section IV, followed

by conclusions in Section V.

II. PRELIMINARIES &PROBL E M FORMULATION

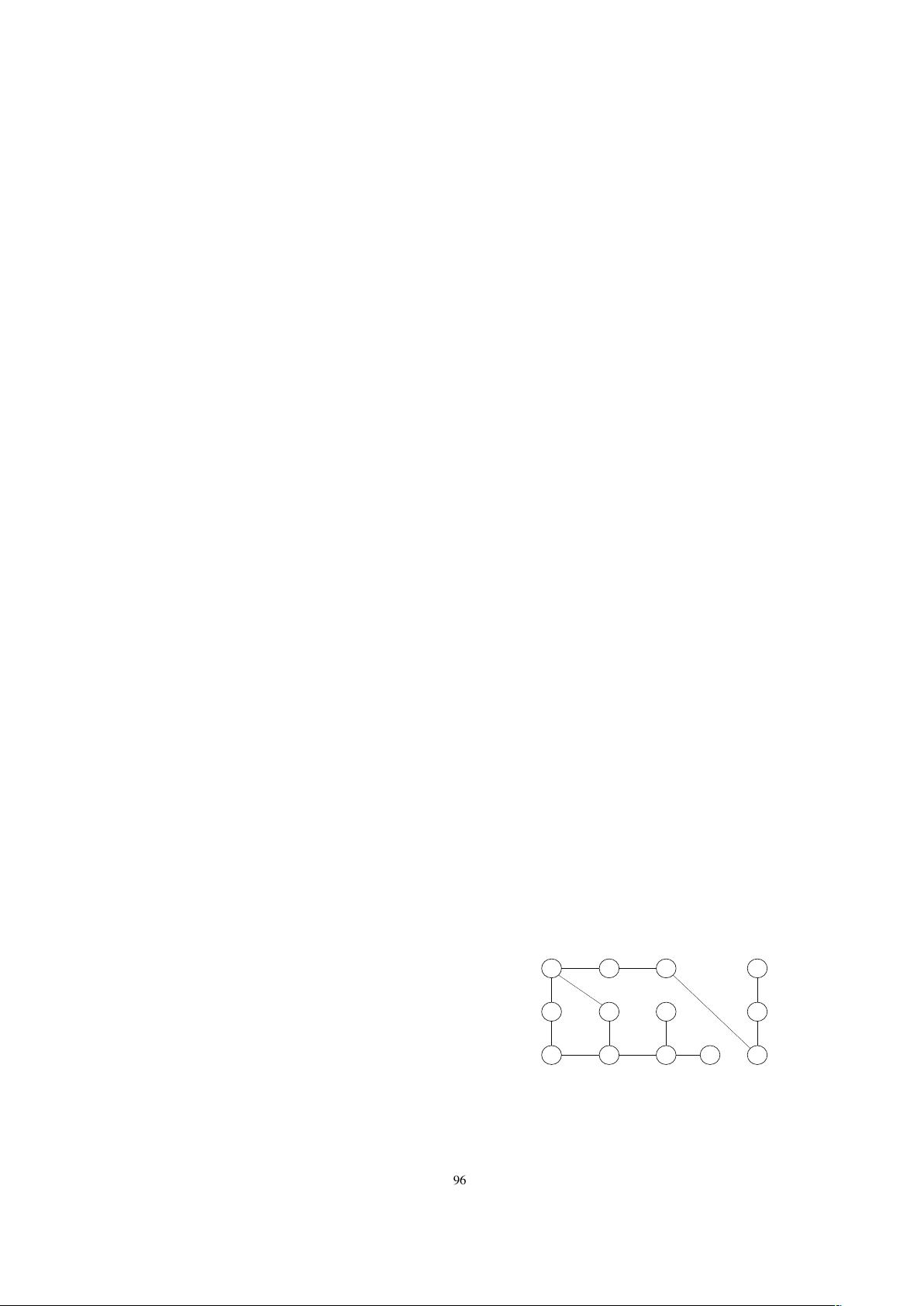

Definition 1: (Core Communication Graph G

cc

): an undi-

rected graph G

cc

=(V

cc

,E

cc

) is defined, in which each n-

ode c

i

∈ V

cc

represents a core c

i

and each undirected edge

e

i, j

=(c

i

,c

j

) ∈ E

cc

represents the communication between the

cores c

i

and c

j

. Besides, the communication requirement for

each edge e

i, j

∈ E

cc

is given by w

i, j

. In Fig.1, we give the G

cc

of the MP3 encoder from [11].