STM32F407ZE:高性能Cortex-M4 MCU数据手册

需积分: 9 155 浏览量

更新于2024-07-14

收藏 5.94MB PDF 举报

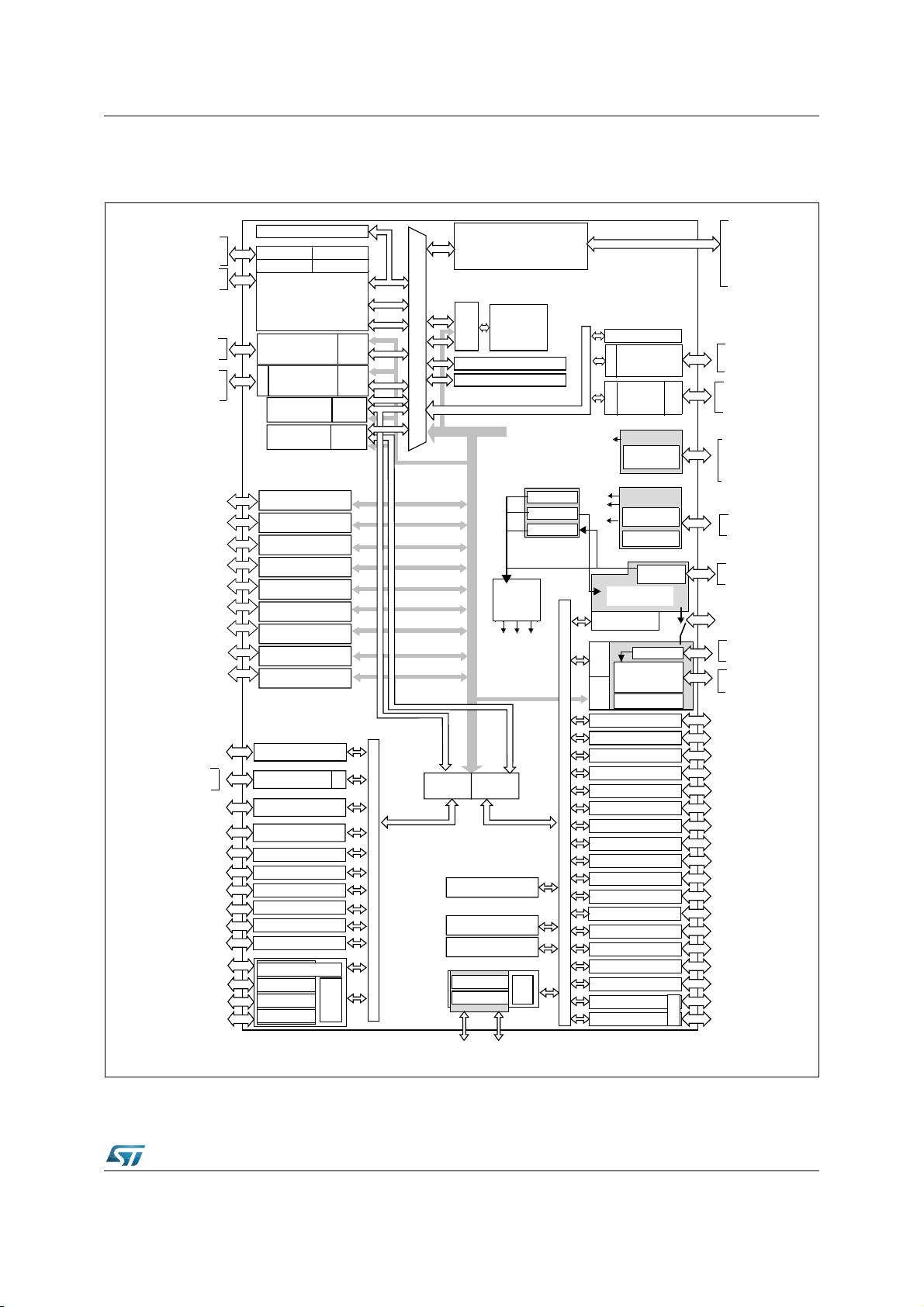

"STM32F407ZE是一款基于ARM Cortex-M4内核的32位微控制器,配备浮点单元(FPU),最高可达到168MHz的工作频率,提供高达1MB的闪存和192+4KB的SRAM,包括64KB的CCM核心耦合内存数据RAM。此外,它还具有512字节的OTP内存,支持多种类型的外部静态存储器,如CompactFlash、SRAM、PSRAM、NOR和NAND。该芯片还集成了LCD并行接口,支持8080和6800模式。STM32F407ZE在时钟和电源管理方面表现出色,可在1.8V至3.6V的电压范围内工作,并具备POR、PDR、PVD和BOR等电源保护功能。它还配备了各种振荡器,包括4至26MHz的晶体振荡器和内部16MHz、1%精度的RC振荡器。此外,还有32kHz的RTC校准振荡器和内部32kHz RC振荡器,确保低功耗操作。STM32F407ZE还包括睡眠等多种低功耗模式。"

STM32F407系列微控制器是意法半导体(STMicroelectronics)的一款高性能产品,专为需要高效计算能力和实时性能的应用而设计。其Cortex-M4内核集成的FPU允许快速执行浮点运算,这对于处理数学密集型任务,如数字信号处理,是至关重要的。ART Accelerator使得从闪存执行指令时可以实现零等待状态,极大地提高了程序执行效率。

内存配置上,STM32F407ZE提供了充足的存储空间,适用于复杂项目的需求。大容量的闪存允许存储大量代码和数据,而SRAM则为运行中的程序提供高速缓存。CCM核心耦合内存特别适用于对速度要求极高的应用,因为它直接连接到处理器,减少了访问延迟。

在接口方面,STM32F407ZE支持多种通信接口,包括USB OTG高速/全速、以太网和多达15种通信接口,这使其能够连接各种外设和传感器。LCD并行接口对于开发带有图形用户界面的嵌入式系统非常有用,8080和6800模式的兼容性增加了设计的灵活性。

电源管理和低功耗特性是STM32F407ZE的另一大亮点。在1.8V至3.6V的宽电压范围内工作,可以适应不同应用场景。POR、PDR、PVD和BOR等电源保护功能确保了设备在异常情况下的稳定性和安全性。此外,多个振荡器选项为时序控制提供了灵活性,同时32kHz的RTC振荡器和低功耗模式使得STM32F407ZE在电池供电的系统中表现出优秀的能效。

STM32F407ZE是一款功能强大的微控制器,适用于需要高性能、低功耗和广泛接口选项的嵌入式系统设计。无论是工业自动化、医疗设备、消费电子还是物联网应用,STM32F407ZE都能提供出色的解决方案。

126 浏览量

849 浏览量

2022-09-05 上传

147 浏览量

2021-06-30 上传

5723 浏览量

181 浏览量

829 浏览量

929 浏览量

zhoumiao_buaa

- 粉丝: 0

最新资源

- C++与XML深度整合:解析与应用实践

- Velocity模板引擎:Java开发中的高效工具

- 整合Hibernate与Spring构建企业级持久层

- C#入门指南:从语言概述到面向对象编程

- 提升C#编程效率:遵循的基本书写规范与命名策略

- C#经典教程:从入门到面向对象

- 数据库设计精华60条:专业人士的经验分享

- LabVIEW初学者指南:快速入门与故障排除

- RS232串口通信编程详解与实践

- PS2鼠标键盘协议详解:接口与技术细节

- SQLServer数据库开发:创建与管理全面指南

- ASP.NET常用函数详解与应用

- EJB设计模式:提升企业应用开发效率的秘密武器

- C#入门教程:从基础到面向对象编程

- J2ME入门教程:MIDlet开发指南

- Matlab命令全集:高效科研工具