DDR4设计指南:信号完整性和终止策略

需积分: 10 186 浏览量

更新于2024-07-17

收藏 2.04MB PDF 举报

"DDR4-Design10122014.pdf是关于DDR4内存设计的指南,涵盖了信号完整性的关键因素,如迹线长度匹配、阻抗控制,以及如何处理板级延迟、串扰、参考电压噪声等问题。文档强调了在构建高效能存储系统时进行信号完整性分析的重要性,并提供了相关的设计建议和技术细节。"

DDR4内存设计是现代高性能计算系统中的关键部分,其设计复杂性主要体现在信号完整性的维护上。DDR4内存条的布局和终止技术对于确保数据传输的准确性和系统的稳定性至关重要。以下是一些DDR4设计的主要知识点:

1. **信号完整性分析**:这是设计高速内存系统时的基础,需要考虑的因素包括板级延迟(boardskews)、交织引起的信号衰减(ISI, Inter-Symbol Interference)、邻近通道串扰(crosstalk)、参考电压(Vref)噪声、路径长度匹配、输入电容(Cin)和返回路径电阻(RTT)的不匹配等。为了确保设计的成功,设计师应采用行业标准实践和假设。

2. **迹线长度匹配**:保持信号路径的长度一致,可以减少信号到达时间的差异,从而降低时序错误的可能性。这对于DDR4内存系统中高速信号的正确同步至关重要。

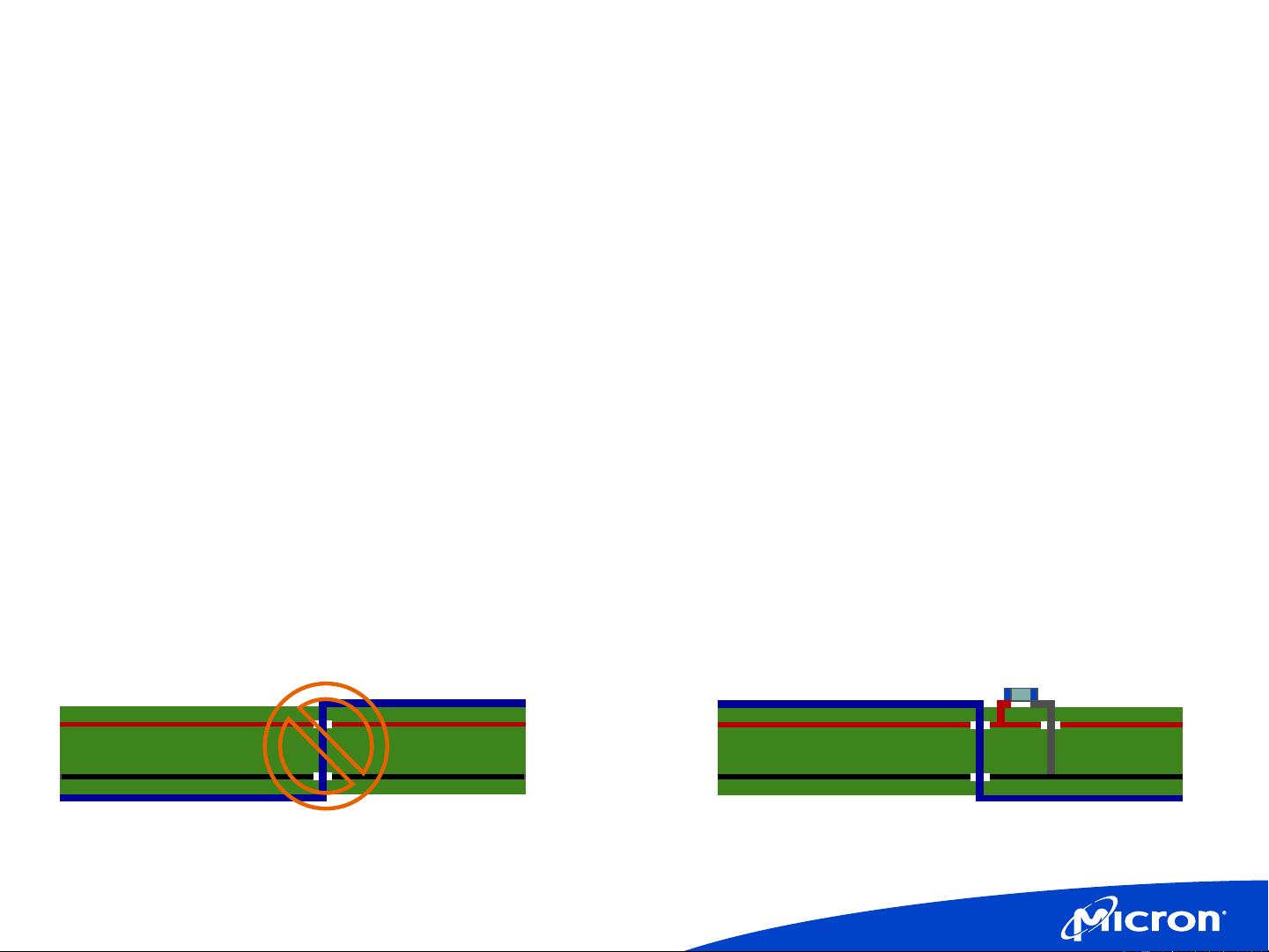

3. **阻抗控制**:确保线路的特性阻抗与连接器和组件的阻抗匹配,可以防止反射,提高信号质量。在DDR4设计中,需要特别注意消除返回路径不连续(Return Path Discontinuities, RPDs),这可以通过优化布线和选择合适的走线策略来实现。

4. **减少自激振荡(SSO, Self-Sustained Oscillation)影响**:SSO是由于信号通过不同路径返回源而导致的振荡现象,它会干扰信号传输。设计师应采取措施减小这种影响,比如优化信号路径和返回路径。

5. **模型模拟**:利用仿真工具和模型对设计进行预测试,以预测和解决潜在的问题,这是验证设计可行性的重要步骤。通过模拟,设计师可以预先设定时序预算,确保设计在实际应用中的表现。

6. **证明概念的时序预算**:在实际制造前,建立一个证明概念的时序预算,可以帮助识别潜在问题并提前进行调整,以满足DDR4内存的严格时序要求。

DDR4内存设计需要综合考虑多个方面,从信号完整性分析到实际的物理布局,每个环节都影响着最终系统的性能和可靠性。设计师必须遵循最佳实践,使用先进的建模和仿真工具,以确保DDR4内存模块在高速运行时的稳定性和数据传输的准确性。这份文档提供的指导原则和建议对于任何从事DDR4内存系统设计的专业人士来说都是宝贵的参考资料。

964 浏览量

868 浏览量

636 浏览量

179 浏览量

128 浏览量

2023-12-28 上传

120 浏览量

2022-02-24 上传