Altera Quartus II 9.2 中文手册:深入解析

需积分: 10 121 浏览量

更新于2024-08-02

收藏 3.86MB PDF 举报

"Quartus2中文介绍"

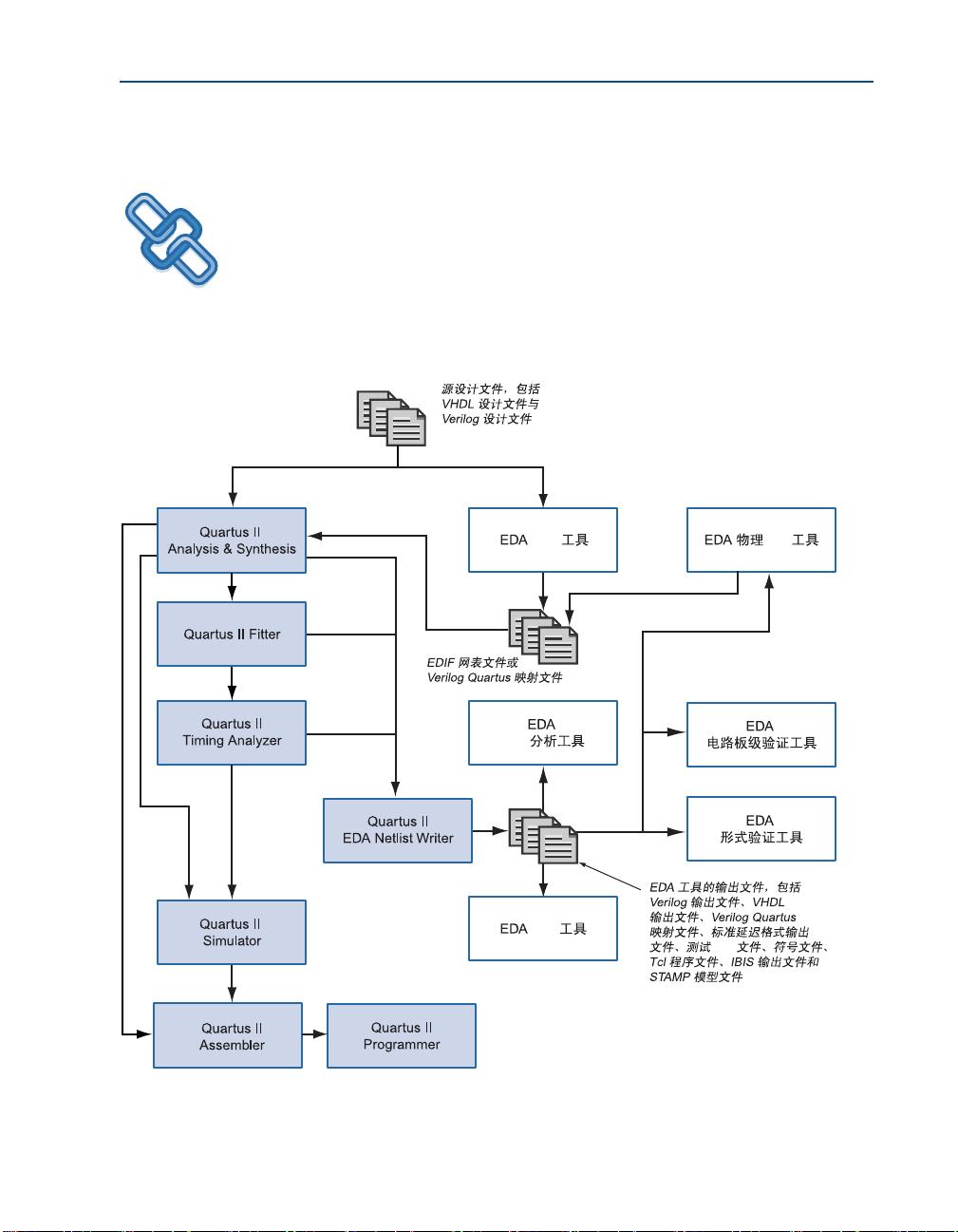

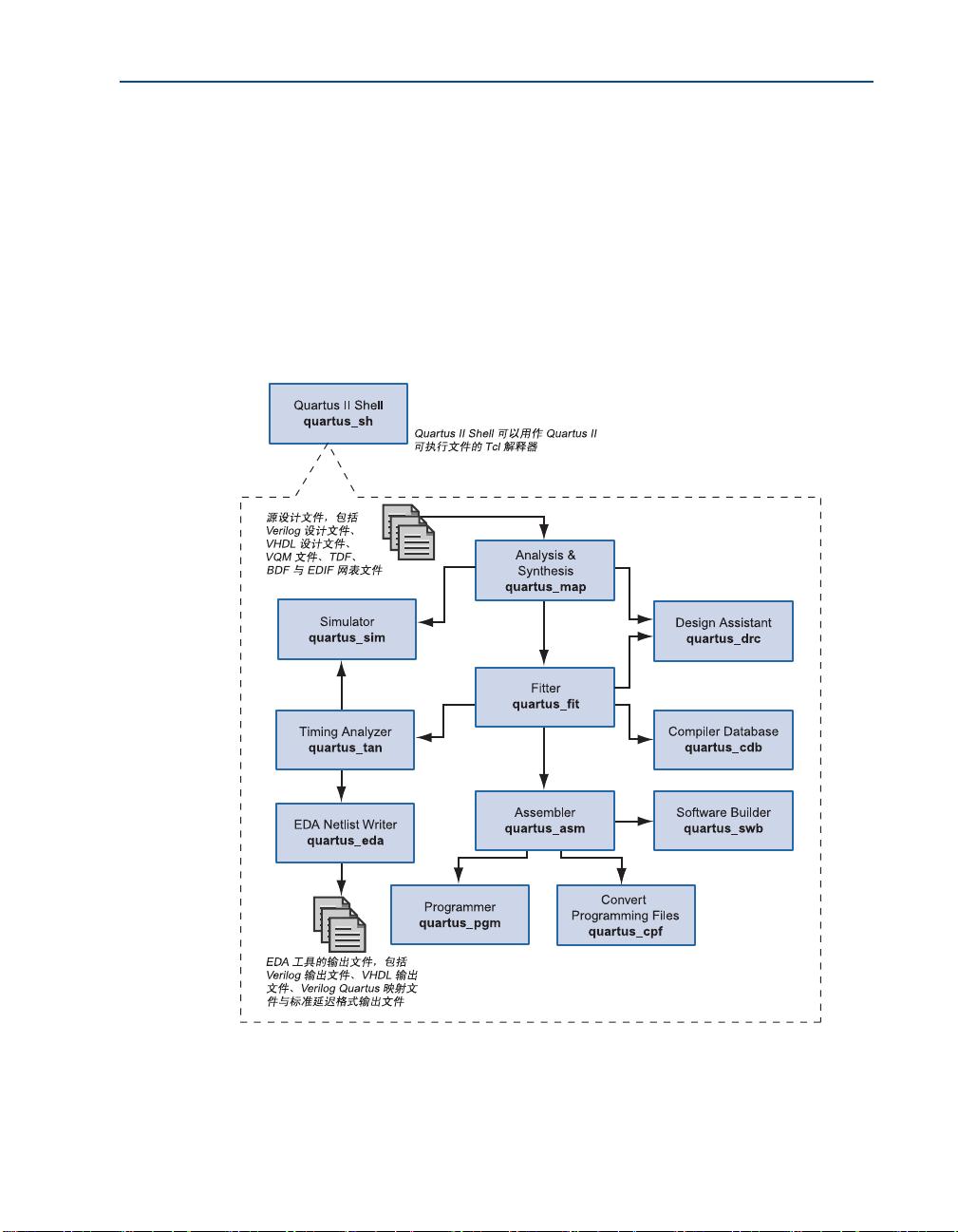

Quartus II是Altera公司推出的一款强大的 FPGA(Field-Programmable Gate Array)设计软件工具,它主要用于数字逻辑电路的设计、仿真、综合、布局布线以及编程下载。Quartus II 提供了一个集成化的开发环境,使得用户能够高效地完成从高层次的硬件描述语言(如 VHDL 或 Verilog)到实际 FPGA 芯片配置的全过程。

Quartus II 9.2 版本的中文手册是为了帮助中国用户更好地理解和使用该软件,克服语言障碍,提高设计效率。手册内容可能包括软件的安装、界面介绍、设计流程、编译设置、时序分析、IP核的集成、硬件调试工具如 SignalTap Logic Analyzer 的使用等方面。

在设计流程方面,Quartus II 提供了以下主要步骤:

1. **项目创建**:用户可以新建项目,并选择目标 FPGA 器件,同时导入 VHDL 或 Verilog 源代码。

2. **设计输入**:用户可以在源代码编辑器中编写 HDL 代码,描述电路逻辑。

3. **编译与综合**:Quartus II 将 HDL 代码转换成逻辑门级网表,这个过程中会进行语法检查、逻辑优化等操作。

4. **时序分析**:软件会对设计进行时序分析,确保满足时钟周期要求。

5. **布局布线**:自动布局布线工具将逻辑门分配到 FPGA 的物理位置,连接它们的路径。

6. **仿真**:在硬件实施前,通过波形仿真验证设计功能的正确性。

7. **编程下载**:最后,将优化后的配置文件下载到 FPGA 芯片中进行实际运行。

Quartus II 还包含了多种高级特性,例如:

- **IP核集成**:支持各种预先验证的知识产权核,如数字信号处理器 (DSP)、内存控制器等。

- **嵌入式处理器系统**:如 Nios II,允许用户在 FPGA 内部集成软核处理器。

- **硬件描述语言混合编程**:支持在同一项目中使用多种 HDL 语言。

- **集成开发环境**:提供统一的界面,包括工程管理、波形查看器、报告生成等工具。

此外,Altera 公司的商标和产品名称如 ByteBlaster 和 SignalTap,分别代表了JTAG编程适配器和一种内置逻辑分析器,这些都是 FPGA 开发中常用到的硬件工具。

请注意,Altera 已经被Intel公司收购,现在的 Quartus II 可能已经更新至更高版本,但基本功能和工作流程仍然保持一致。用户在使用过程中应确保获取最新的软件版本和相关文档,以充分利用其提供的新特性和性能改进。同时,Altera 对其产品的质量和性能提供保证,但不负责第三方专利或版权侵权问题,除非有特定书面协议。

294 浏览量

514 浏览量

517 浏览量

103 浏览量

235 浏览量

152 浏览量

2008-12-12 上传

chinawangyabin

- 粉丝: 0

- 资源: 1

最新资源

- Yolov5+Deepsort所需模型

- 【ssm项目源码】商户管理系统.zip

- vs2017+svn工具.rar

- ssm(spring+springMVC+mybatis)权限管理系统完整源码

- ProcessManager

- cabdriver:出租车的小帮手

- 教程:使用 MATLAB 进行并行和 GPU 计算(第 7 个,共 9 个):spmd:parfor 之外的并行代码:使用 MATLAB 进行并行和 GPU 计算的教程(第 7 个,共 9 个)-matlab开发

- MultiScreenDemo.7z

- 服装

- java面向对象 swing学生管理系统(完成)+报告.zip

- Akiyama:使用Aruppi API的动漫网站和移动应用程序

- oas2joi:根据开放API规范创建Joi模式

- festival:节日演讲综合系统

- QtModbus.rar

- springbootDemo.rar

- Markdown使用教程