Verilog实现数字钟:分层设计与FPGA实现

需积分: 0 144 浏览量

更新于2024-08-04

收藏 782KB DOCX 举报

"这篇实验报告主要介绍了如何使用Verilog HDL设计一个数字钟,包括顶层模块、七段译码器、动态扫描、分频器以及不同类型的计数器。实验目的是熟悉Verilog分层设计、功能模块的重复调用以及数字电子钟的实现原理,并实现额外的功能如闹钟、整点报时和时制切换。"

实验中涉及的知识点详解:

1. **Verilog HDL**: Verilog 是一种硬件描述语言,常用于数字系统的设计和验证,它可以用来描述数字系统的结构和行为。

2. **分层设计**: 分层设计是软件工程和硬件设计中的常用方法,将复杂的设计分解成多个独立的模块,每个模块负责特定的功能,便于管理和调试。

3. **顶层模块**: 在数字系统设计中,顶层模块是整个设计的入口,它将所有子模块连接起来,形成完整的系统。在这个实验中,顶层模块整合了七段译码器、计数器等部件,以实现数字钟的完整功能。

4. **七段译码器**: 七段译码器是一种电路,它能够将二进制数转换为七段显示管所需的驱动信号,使得数码管能够显示出相应的数字。在这个实验中,七段译码器接收四位二进制数码,驱动共阳极显示器来显示时间。

5. **动态扫描**: 动态扫描技术是数码管显示的一种优化方法,通过快速轮流点亮数码管的不同部分,利用人眼的视觉暂留效应,使得所有数码管看似同时亮起,减少硬件资源的使用。

6. **分频器**: 分频器是数字电路中的一种重要组件,它的任务是将高频率的时钟信号转换为较低频率的信号。实验中设计了一个模数为25×106的计数器,用于产生1Hz的秒脉冲,占空比为50%,作为数字钟的计时基准。

7. **计数器设计**:

- **模24计数器**:用于存储小时的个位和十位,当达到24(1001)时,个位重置,十位加1,确保小时在0-23之间循环。

- **模10计数器**:用于存储分钟和秒的个位,当达到10(1001)时,个位重置,同时触发模6计数器。

- **模6计数器**:用于存储分钟和秒的十位,当达到6(0101)时,重置并触发模24计数器。

8. **拓展功能**:

- **闹钟**:允许设置特定时间点进行提醒。

- **整点报时**:每到整点时,系统自动发出报时信号。

- **时制切换**:在12小时制和24小时制之间切换。

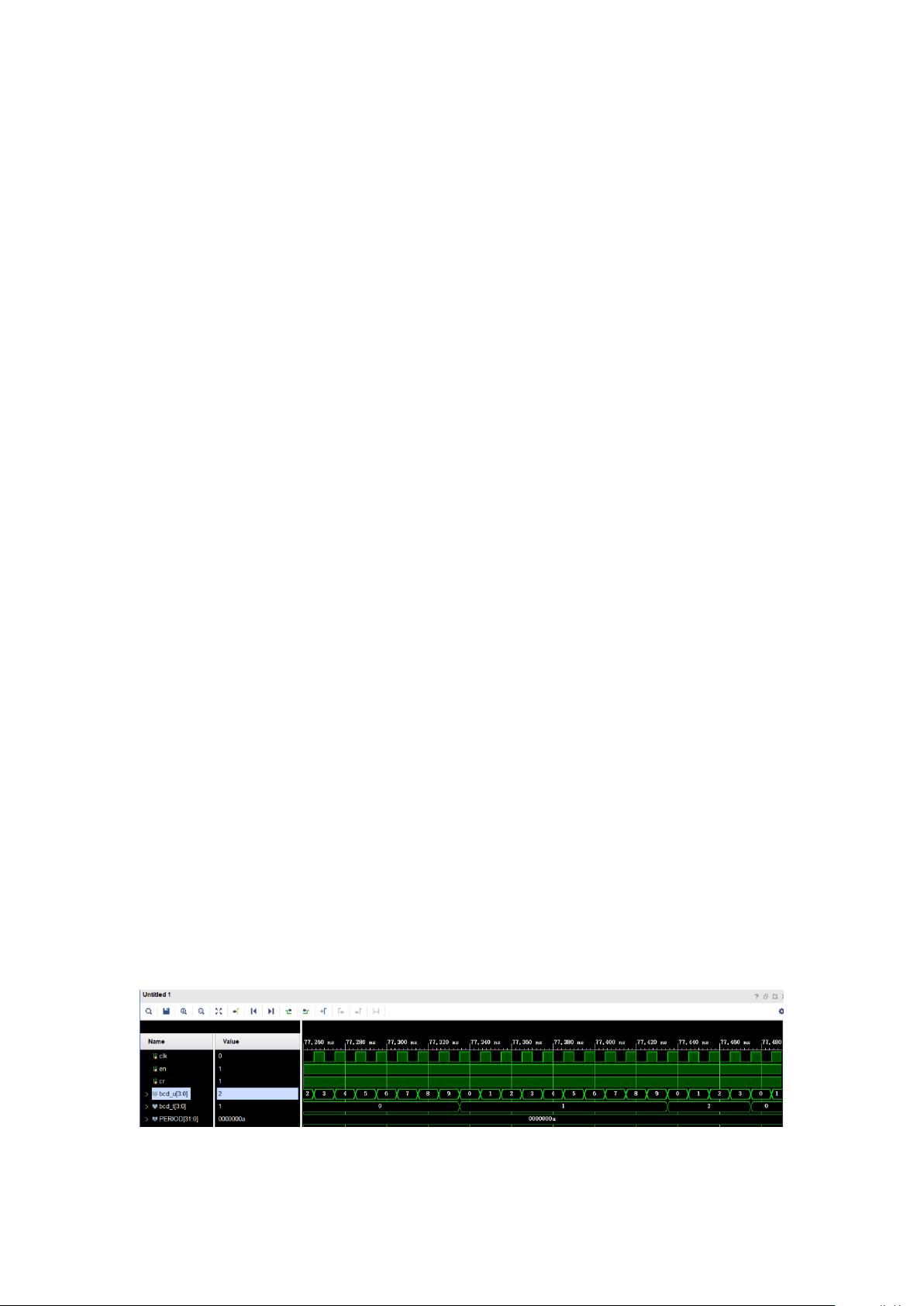

9. **仿真分析**:在设计过程中,使用Verilog HDL编写代码后,会进行仿真验证,查看设计是否符合预期,如24小时波形图、1分钟波形图、12进制/24进制仿真等,确保设计无误。

通过这个实验,学习者不仅可以掌握Verilog HDL的基本语法和设计技巧,还能理解数字时钟的工作原理,以及如何在FPGA平台上实现这些设计。同时,通过添加扩展功能,可以锻炼问题解决能力和创新能力。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-08 上传

329 浏览量

2018-05-19 上传

2018-06-26 上传

优游的鱼

- 粉丝: 984

- 资源: 316

最新资源

- BeatTheBotChallenge:来挑战这个玩摩托赛车电话游戏的机器人,看看它是如何制造的,并帮助改进它!

- GetHtmlTool:Qt初步获取网页原始码

- StudentClass,java怎么看源码,javap2p网贷源码下载

- 宠物播种机

- zeromq-4.2.0.tar.zip

- nginx-http-concat:WordPress插件可将单个脚本文件CSS和Javascript连接成一个资源请求

- 高级JSON表单规范第2章:输入小部件

- angularjs-studies

- city-generator:C ++ City Generator

- SocketProject:SocketProject

- crawl_html:python网络爬虫-爬网页原始码

- 手写 Volley 网络访问框架

- living-with-django:关于容忍最臃肿的python web框架的博客

- RestaurantsAppWithCollectionViews

- SkeSubDomain:利用递归归,通过匹配网页源码里的子域内容收集所有的子域信息,可收集四级五级等多级子域名

- portfolio:我的投资组合网站,其中包含我的所有工作