Cadence Encounter Conformal Low Power:优化低功耗设计与验证

"Cadence CLP 介绍.pdf"

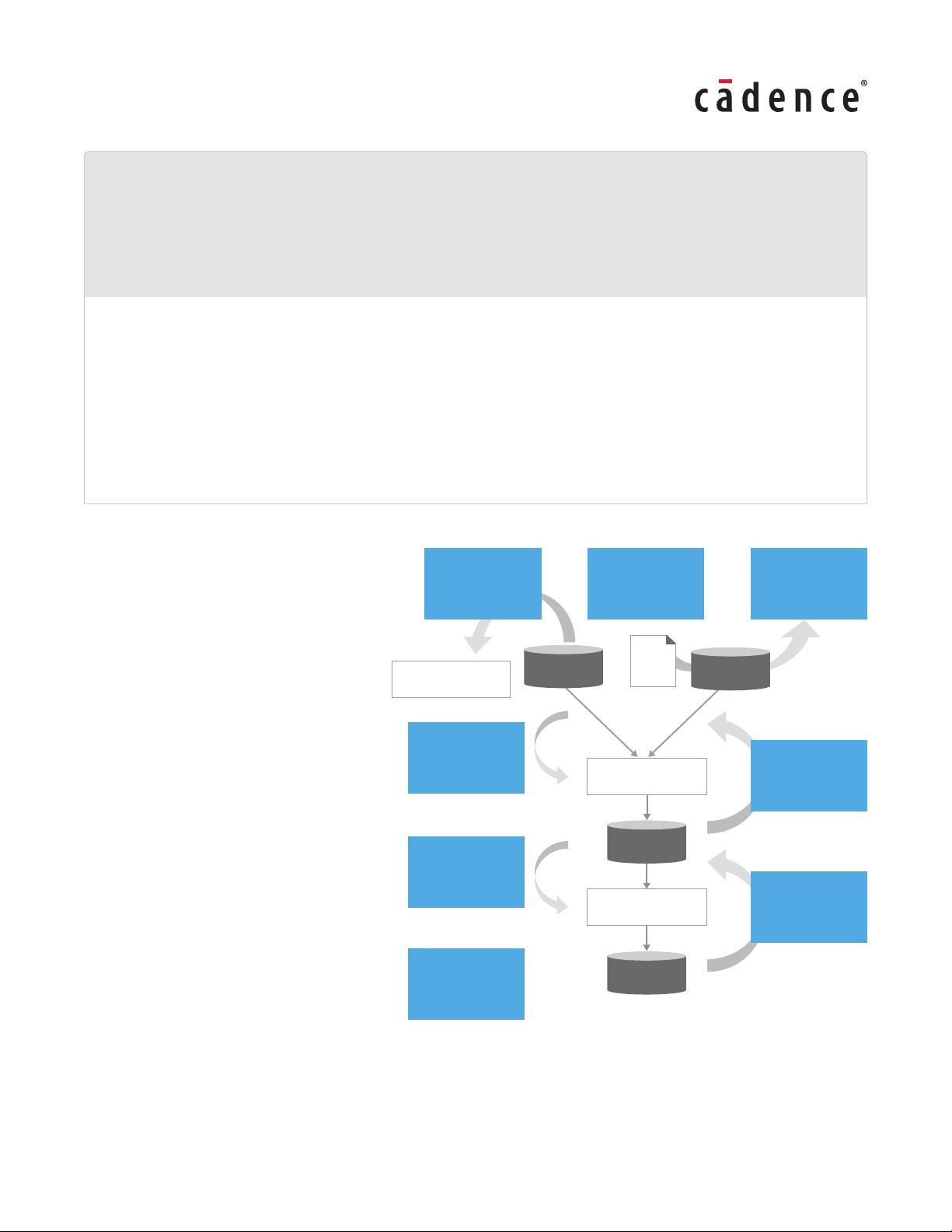

Cadence Encounter Conformal Low Power 是一款针对集成电路设计中的低功耗优化和验证的专业工具。在当前的半导体行业中,降低功耗是设计高性能芯片的关键因素,因为这不仅可以减少能源消耗,还能降低封装成本。 Encounter Conformal Low Power 技术提供了一整套全面且经过生产验证的解决方案,以应对设计周期时间的缩短和硅片重试的最小化挑战。

该工具集主要包含以下几个关键功能:

1. **等价性检查**:确保经过优化的设计在功能上与原始设计保持一致,这是在进行低功耗优化后验证设计正确性的基础。

2. **时序约束管理**:管理和调整设计中的时序约束,以适应低功耗设计中电压和频率的变化。

3. **时钟域跨越同步检查**:检查在不同时钟域之间数据传输的正确性,防止由于低功耗设计中的时钟关断和动态电压频率缩放(DVFS)引发的错误。

4. **功能工程变更订单(ECO)分析和生成**:当设计需要修改时,快速有效地生成和应用ECO,以减少对整个设计流程的影响。

5. **低功耗设计优化和验证**:Cadence Encounter Conformal Low Power 提供了专门针对泄漏和动态功耗的优化方法,包括静态和动态电压频率缩放、电源门控和状态保留等先进的低功耗技术。

6. **门级仿真替代**:通过避免复杂的门级仿真,大幅减少了验证时间和资源消耗,尤其对于包含数百万门的大型设计,这是一个巨大的优势。

7. **电源意图的创建、验证和集成**:允许工程师在设计上下文中创建、验证电源管理策略,并将这些策略无缝集成到设计流程中,确保低功耗设计目标的实现。

在低功耗设计中,Cadence Encounter Conformal Low Power 提供的工具和方法可以应对复杂性和额外的验证挑战,帮助工程师更有效地实现功耗降低的目标,同时保证设计的正确性和可靠性。这一解决方案在提高设计效率的同时,也推动了半导体行业的技术创新和发展。

276 浏览量

1049 浏览量

2021-10-07 上传

1653 浏览量

superyan0

- 粉丝: 95

- 资源: 23

最新资源

- easypanel虚拟主机控制面板 v1.3.2

- Coursera

- wind-js-server:用于将Grib2风向预报数据公开为JSON的服务

- 生命源头论坛 LifeYT-BBS V2.1

- TUTK_IOTC_Platform_14W42P2.zip TUTK IOTC官方sdk

- WeatherJournalApp

- 电商小程序源码项目实战

- 美女婚纱照片模板下载

- GB 50231-1998 机械设备安装工程施工及验收通用规范.rar

- MPT-开源

- facebook-archive:使用Facebook的存档数据可以享受一些乐趣

- 阿普奇工业显示器PANEL2000.zip

- action_react

- Torus-开源

- 应用js

- WPF将控件中的文字旋转.zip