设计与执行RISC-V RV32I CPU:单周期实现

需积分: 0 70 浏览量

更新于2024-08-05

收藏 1.57MB PDF 举报

"本次实验是通信工程专业学生吴雨松在2019年9月3日完成的夏季小学期实验,实验主题是设计并执行一个基于RISC-V架构的单周期CPU,能够处理基本整数指令集RV32I中的Load/Store指令和控制转移指令。实验中,吴雨松使用了VHDL或Verilog语言进行硬件描述,并通过Quartus 9.0软件进行了功能仿真。实验的CPU设计中,Load/Store指令执行需要两个周期,而其他指令仅需一个周期。实验在配备i5-6300HQ CPU、8GB内存和Windows 10 1903操作系统的环境下进行。

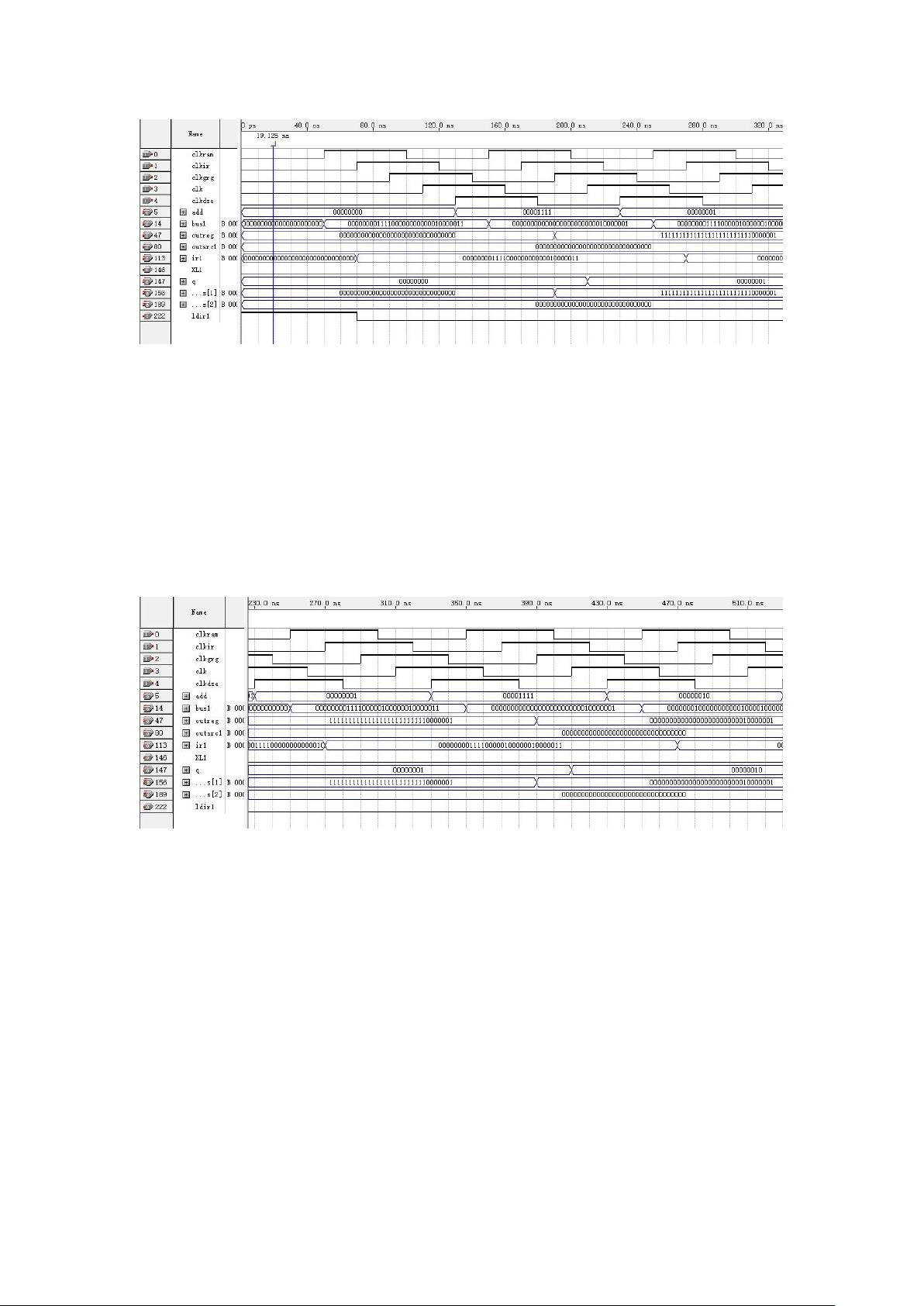

在测试环节,吴雨松对几种Load/Store指令进行了验证,包括lb(加载带符号字节)、lbu(加载无符号字节)和lh(加载半字)。对于lb指令,测试指令为00000000111100000000000010000011,该指令从内存地址mem[15]加载数据,经过有符号扩展后存入寄存器reg[1]。由于初始mem[15]的数据为00000000000000000000000010000001,经过有符号扩展,结果与仿真相符,即11111111111111111111111110000001。lbu指令的测试指令为00000000111100000100000010000011,它将mem[15]的无符号字节数据加载到reg[1],由于无符号扩展是向左填充零,因此结果与初始数据相同,即00000000000000000000000010000001。而对于lh指令,它加载的是半字数据,但由于这部分内容未给出完整信息,所以无法提供具体的分析。

此外,实验还包括了控制转移指令如beq(分支如果相等)、bne(分支如果不等)、blt(分支如果小于)、bltu(分支如果小于无符号)、bge(分支如果大于或等于)、bgeu(分支如果大于或等于无符号)、jal(跳转并链接)和jalr(跳转并链接寄存器)、auipc(算术立即加载到PC)等。这些指令对于构建一个能够执行基本控制流程的CPU至关重要。

实验的主要目标是理解和实现RISC-V架构中的基础指令集,这有助于学习者深入理解计算机系统的工作原理,以及硬件描述语言在构建数字逻辑系统中的应用。通过这样的实践,学生能够掌握处理器设计的基础知识,并具备实际的硬件设计能力。"

2017-12-07 上传

2021-10-07 上传

2024-02-01 上传

2018-11-11 上传

2021-10-02 上传

2018-10-10 上传

2021-08-31 上传

会飞的黄油

- 粉丝: 33

- 资源: 303

最新资源

- Cortex-M3权威指南

- GlassFish+快速入门指南

- Ubuntu标准教程

- 字典排序-算法分析(第三版)1.2

- 数字统计——算法分析(第三版)1.1

- altium designer 提高教程

- Java Swing (O'Reilly).pdf

- CPU时间片轮转调度算法

- HP OpenView应用监控解决方案

- IIC协议说明文档——目前网上所能找到的最完整的IIC协议说明规范!

- MSP430仿真器使用说明

- ibatis中文开发文档(pdf格式)

- Matlab图形图像处理函数

- 使用Team Foundation中的源代码控制

- 用JavaScript改进WEB课件中的用户界面设计

- DevTreeList控件使用经典