Avalon接口规范更新:适用于Intel Quartus Prime设计套件17.1

需积分: 7 86 浏览量

更新于2024-07-18

收藏 483KB PDF 举报

"Avalon接口规格更新,适用于Intel Quartus Prime设计套件17.1版"

本文档详细介绍了Avalon接口的规范,该规范是Altera(现已被Intel收购)为Intel Quartus Prime设计套件17.1版本更新的。Avalon接口是一种用于片上系统(SoC)的互连架构,它提供了高效的通信机制,特别是在FPGA(现场可编程门阵列)和ASIC(应用专用集成电路)设计中。

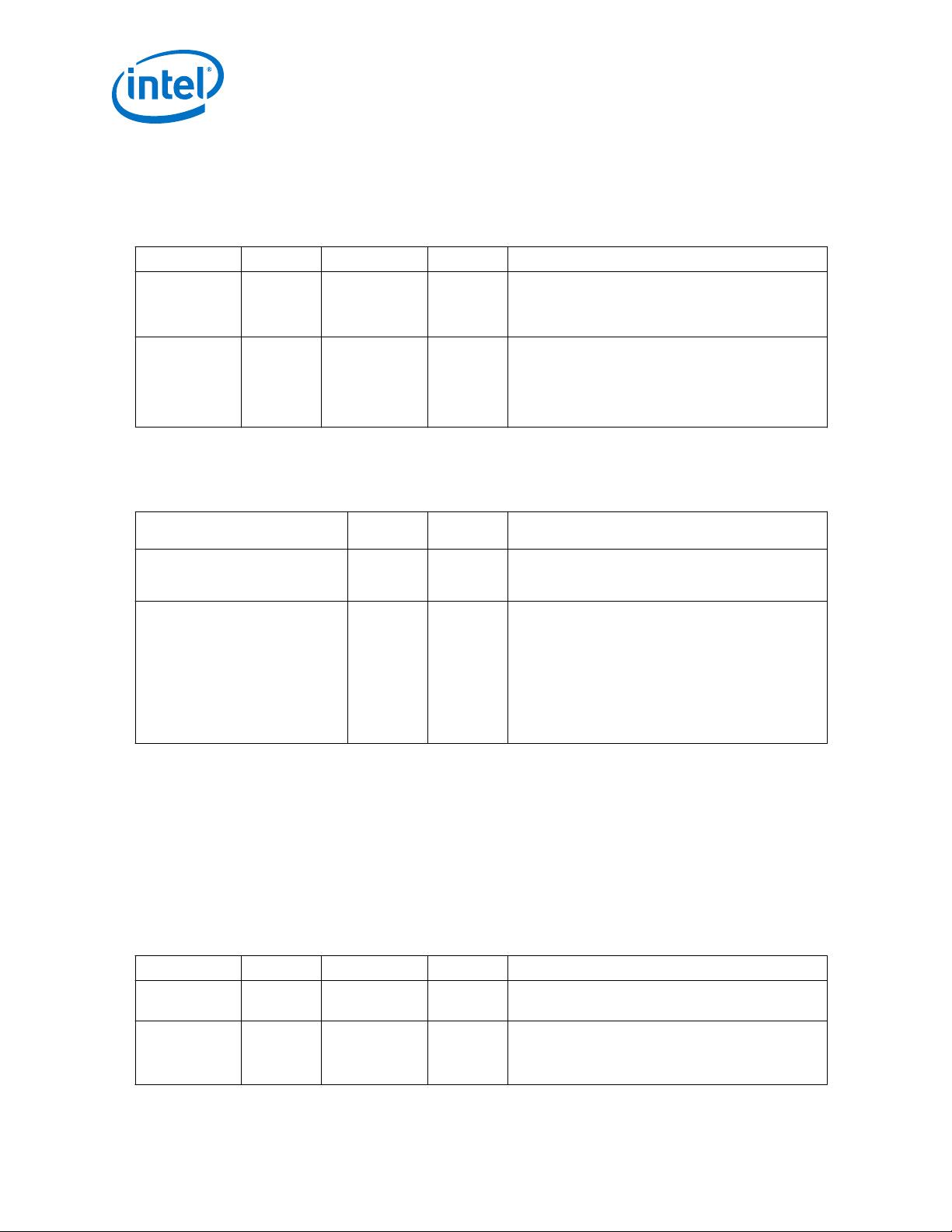

1. Avalon接口特点与参数

- Avalon接口具有一系列定义好的属性和参数,这些参数定义了接口的行为、数据宽度、地址空间和其他关键特性。例如,信号角色、数据宽度、地址大小等都是接口设计的关键参数。

- 信号角色:每个信号在接口中的功能,如读数据、写使能、地址线等,都有明确的角色定义,确保了数据传输的正确性。

2. Avalon时钟和复位接口

- Avalon接口中包含了时钟和复位信号,确保系统的同步操作。时钟源和时钟接收器都有特定的信号角色和属性。

- 时钟接收器(Clock Sink):接收外部时钟信号,其信号角色包括时钟输入,以及相关的时钟使能和停止信号。

- 复位接收器(Reset Sink):处理系统复位信号,包括复位请求和复位确认。

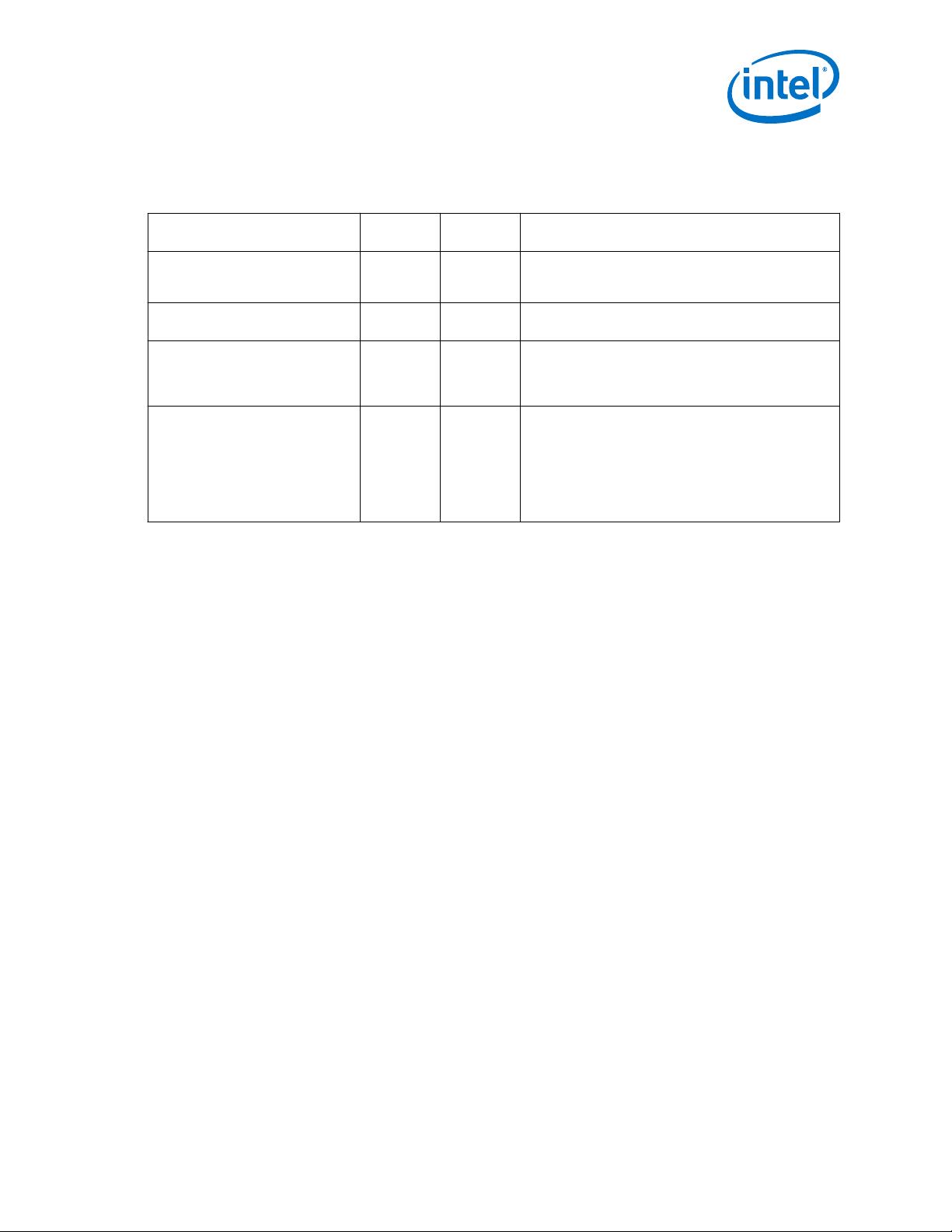

3. Avalon内存映射接口

- 内存映射接口允许访问存储器和寄存器,它是Avalon接口的核心部分,用于实现高效的数据读写操作。

- 信号角色:包括读数据、写数据、读使能、写使能、地址线等,它们共同协作完成数据的存取。

- 接口属性:如数据宽度、地址线数量、等待状态控制等,这些属性决定了接口的性能和兼容性。

- 接口时序:定义了信号间的相对时序,确保正确执行读写操作。

- 数据传输:

- 常规读写:描述了基本的单次读写操作。

- 等待请求允许:允许在传输过程中插入等待周期,适应不同速度的组件。

- 固定等待状态:对于固定延迟的系统,可以预设等待状态来调整时序。

- 管道传输:通过预取数据来提高带宽,实现连续的无中断数据流。

- 批量传输:允许连续的多数据项传输,提高效率。

这些规范为设计者提供了详细的指导,以构建高效、可靠的SoC系统。Avalon接口的灵活性和适应性使其成为各种复杂设计的理想选择,无论是简单的数据传输还是高性能的内存访问,都能通过适当的配置来满足需求。在使用Intel Quartus Prime设计套件17.1进行设计时,了解并掌握这些Avalon接口的规范至关重要,能够帮助开发者优化系统性能,减少设计错误,并加速产品开发进程。

2022-09-23 上传

2022-09-21 上传

154 浏览量

2021-08-12 上传

点击了解资源详情

点击了解资源详情

2025-03-06 上传

2025-03-06 上传

2025-03-06 上传

cynth

- 粉丝: 0

最新资源

- Openaea:Unity下开源fanmad-aea游戏开发

- Eclipse中实用的Maven3插件指南

- 批量查询软件发布:轻松掌握搜索引擎下拉关键词

- 《C#技术内幕》源代码解析与学习指南

- Carmon广义切比雪夫滤波器综合与耦合矩阵分析

- C++在MFC框架下实时采集Kinect深度及彩色图像

- 代码研究员的Markdown阅读笔记解析

- 基于TCP/UDP的数据采集与端口监听系统

- 探索CDirDialog:高效的文件路径选择对话框

- PIC24单片机开发全攻略:原理与编程指南

- 实现文字焦点切换特效与滤镜滚动效果的JavaScript代码

- Flask API入门教程:快速设置与运行

- Matlab实现的说话人识别和确认系统

- 全面操作OpenFlight格式的API安装指南

- 基于C++的书店管理系统课程设计与源码解析

- Apache Tomcat 7.0.42版本压缩包发布