Verilog HDL实现状态机:流水灯与编码方式探索

版权申诉

86 浏览量

更新于2024-09-08

收藏 219KB DOCX 举报

"实验二:状态机 - 探索有限状态机(FSM)、Verilog HDL编程以及Gray编码和One-hot编码在流水灯设计中的应用"

本实验主要目标是让学生对有限状态机(FSM)有初步理解,并加强在VIVADO环境下使用Verilog HDL进行数字逻辑设计的基础。实验内容包括三个主要部分:

1. **流水灯设计**:通过状态机实现流水灯效果。流水灯是一种常见的数字电路演示,它使用一组LED按照特定顺序依次点亮和熄灭,以此展示时序控制的概念。在本实验中,学生需要编写Verilog代码来控制LED的亮灭顺序。

2. **状态机编码方式**:学习并理解两种不同的状态机编码方式——Gray编码和One-hot编码。Gray编码是一种无权差编码,相邻两个状态之间只有一位不同,这在状态机中可以减少由于编码转换产生的错误。而One-hot编码则是一种每个状态都由一个唯一的“1”和多个“0”表示的编码方式,适用于状态数量较大的情况。

3. **状态机结构**:了解将触发器部分和组合逻辑部分结合与分开的两种状态机结构。在同步状态机中,组合逻辑和触发器通常一起工作,而在异步状态机中,它们可能被分离以处理时钟域跨越的问题。

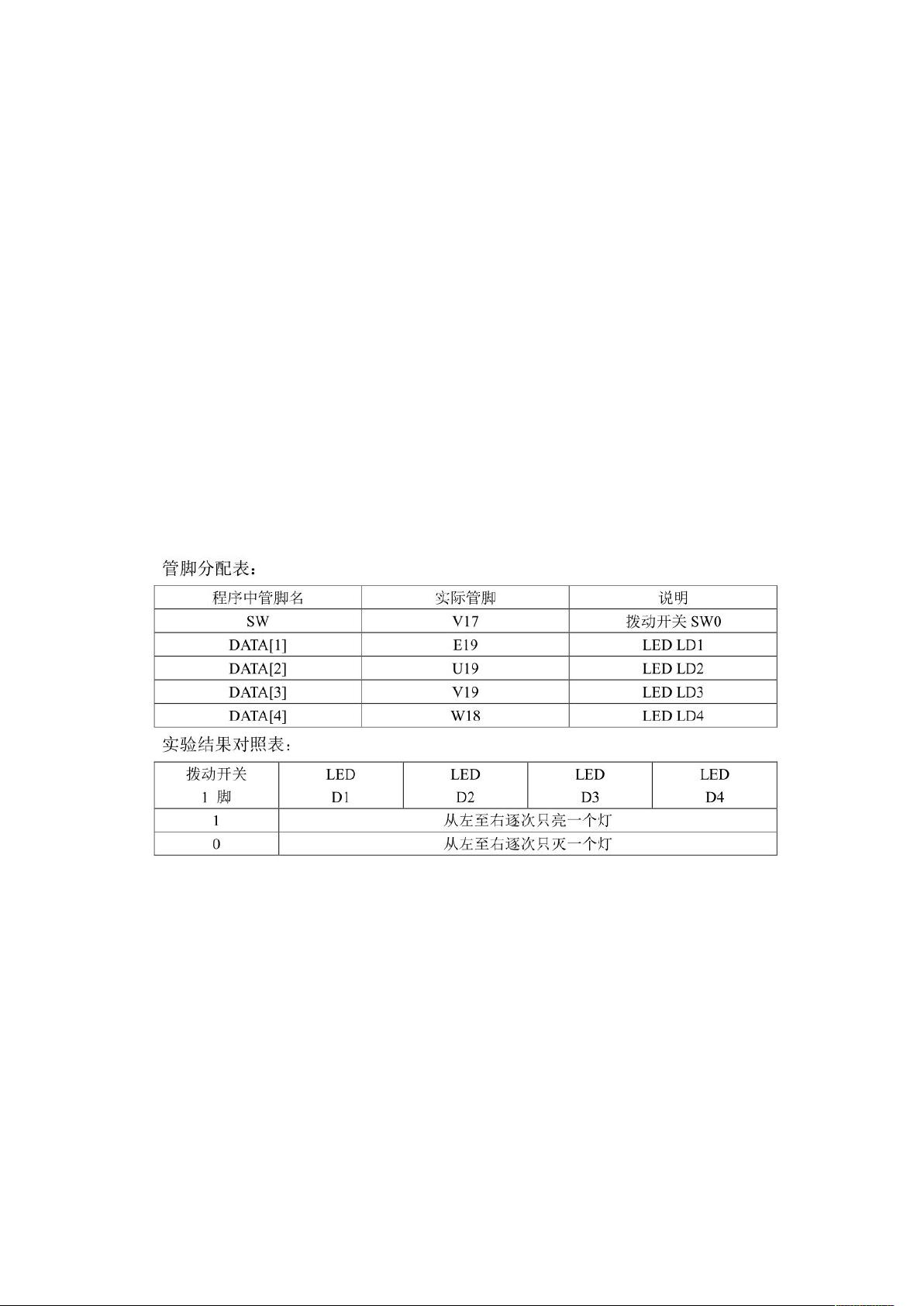

实验要求学生不仅要完成符合要求的流水灯设计,还能通过拨码开关选择显示Gray编码或One-hot编码的流水灯模式。实验代码示例展示了如何在Verilog中定义状态机,包括状态变量(state)、计数器(n)和输出数据(data)。在每次时钟上升沿,状态会根据预设的转移条件更新,同时LED的亮度也会相应改变。

激励代码部分提到,可以通过改变CLK信号和设置SW开关的状态来测试状态机的行为。例如,设置SW为1可激活流水灯,而设置为0则会熄灭LED。

这个实验有助于学生深入理解状态机的设计原理,熟悉Verilog HDL语言,以及掌握不同编码方式和状态机结构的特性。通过实际操作,学生能够增强数字逻辑设计的实践能力,并为后续更复杂的数字系统设计打下坚实基础。

2022-12-22 上传

231 浏览量

2025-01-08 上传

2025-01-08 上传

2025-01-08 上传

2025-01-08 上传

GDFGADFG

- 粉丝: 0

- 资源: 2

最新资源

- 记忆翻牌小游戏

- PC微信加密图片解密源码C#

- product-register

- ManagmentPlugin:用于管理Mindustery服务器的插件

- 图像去噪,中值,均值,双边,高斯,FFC-MSPCNN

- 行业文档-设计装置-隧道施工二衬环向钢筋步进排布装置.zip

- C# OpenCvSharp 去除字母后面的杂线 源码

- MyReactProject

- datafrog-旨在嵌入其他Rust程序的轻量级Datalog引擎-Rust开发

- U大师U盘启动盘制作工具 v1.2.0 超微版

- SassPipeline

- WordPress v5.2 RC2

- 每晚amadeus-Rust中的和谐分布式数据处理和分析。 实木复合地板postgres aws s3 cloudfront elb json csv日志hadoop hdfs箭头常见爬网-Rust开发

- 龙格库塔解微分方程,龙格库塔解微分方程组,matlab

- com.atomist:我的新项目

- Javascript_001