Verilog HDL实现4×4键盘扫描电路设计与仿真

需积分: 37 93 浏览量

更新于2024-09-03

6

收藏 4.22MB DOC 举报

"4×4键盘扫描电路设计文档包含了使用VHDL语言编程的4×4键盘扫描电路设计,该设计基于Quartus II软件。文档内含详细的VHDL程序代码,以及仿真波形图。设计任务是在时钟控制下通过循环扫描键盘,根据列扫描信号和键盘响应确定按键位置,并将按键值显示在7段数码管上。设计报告书目录包括设计目的、设计思路、设计内容、系统调试与结果、主要元器件与设备以及课程设计体会和参考文献。"

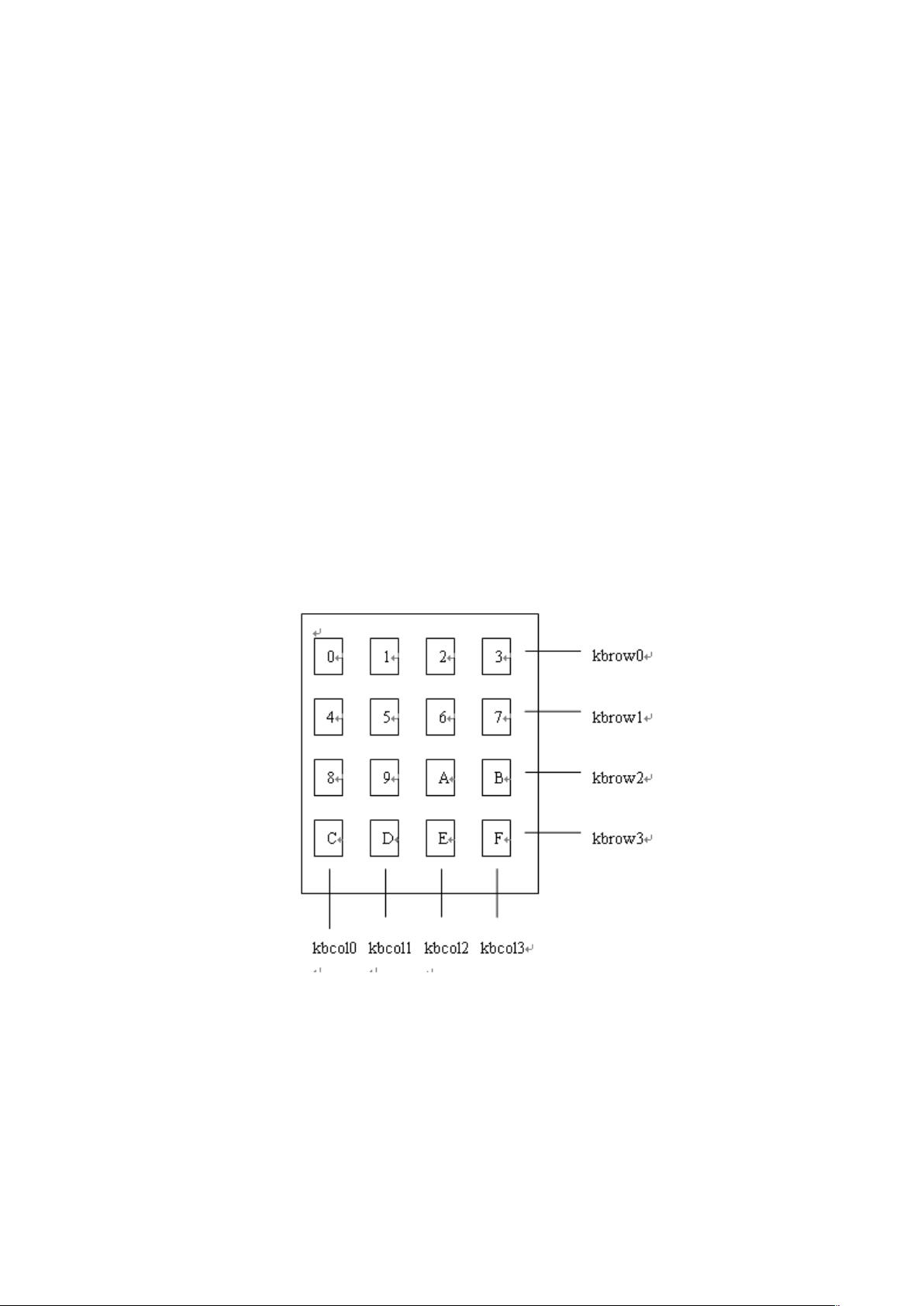

设计一个4×4键盘扫描电路旨在掌握行列式键盘接口电路的实现方法,同时学习更复杂的数字系统设计。设计思路是通过给键盘的四行线分别赋值为高电平,进行循环扫描,当某行线被置为高电平时,对应的列线如果检测到高电平,就表示有按键被按下。例如,当行线为"1000"时,如果0键被按下,列线"kbcol"会输出"1000",表示按键值为0,然后这个值将在7段数码管上显示。

在设计内容中,原理分析部分阐述了4×4矩阵键盘的工作原理,主要利用扫描技术。通过依次将列线设置为高电平,读取行线的反馈信号来识别按键状态。例如,当所有行线均为低电平时,如果检测到某一列线为高,则表明对应的键已被按下。这个过程通过VHDL编程实现,并在Quartus II环境中进行功能仿真。

程序设计阶段,开发者需要用VHDL语言编写代码,描述键盘扫描逻辑和数码管显示逻辑。这部分可能包含定义信号、处理时序逻辑和组合逻辑,以及状态机的设计,以实现键盘扫描的循环和按键值的识别。

在系统调试与结果部分,通常会记录仿真过程中发现的问题和解决办法,以及实际下载到EDA设计试验箱后的运行情况。此外,还会列出所使用的元器件清单,确保所有硬件组件能协同工作。

最后,课程设计体会部分是学生对整个设计过程的反思和总结,包括遇到的挑战、解决问题的过程以及从中学到的知识点。参考文献则列出了设计过程中参考的相关资料和技术文档。

该设计涵盖了硬件描述语言(VHDL)、FPGA开发工具(Quartus II)、数字系统设计原理、键盘接口技术以及电路仿真等多个方面的内容,是一个综合性的数字系统设计实践项目。

2021-08-09 上传

2020-07-14 上传

2019-07-20 上传

2021-10-07 上传

2021-09-16 上传

2022-06-17 上传

2022-02-16 上传

2023-07-05 上传

blank...

- 粉丝: 0

- 资源: 1

最新资源

- casa-inteligente

- esp:esp咨询开发人员

- Accuinsight-1.0.23-py2.py3-none-any.whl.zip

- 径向基函数 (RBF) 教程 - 作为函数逼近器的神经网络:关于径向基函数 (RBF) 的西班牙语教程,仅供学术和教育使用-matlab开发

- neighbors:le Wagon编码训练营的最终项目,批次531

- DP-060JA-Migrating-your-Database-to-Cosmos-DB

- 九九乘法口诀表(word打印版).rar

- AdsAuth

- athena_health:雅典娜健康宝石的叉子

- Digimon Database 数码兽数据库-数据集

- 西门子200发脉冲控制步进电机程序.rar

- monitor-bot:通过官方手柄跟踪网站的变化和新推文

- tap-console-parser:通过劫持 console.log 解析 TAP

- Login-page:登录页面以及链接到postgres的数据库

- TomKingDAO-猫王DAO框架

- Projeto-Site-de-Noticias-Cidade:城市新闻网站的设计