FPGA实现的曼彻斯特解码器设计与实践

需积分: 50 36 浏览量

更新于2024-09-08

3

收藏 878KB PDF 举报

"基于FPGA的曼彻斯特解码器设计与实现"

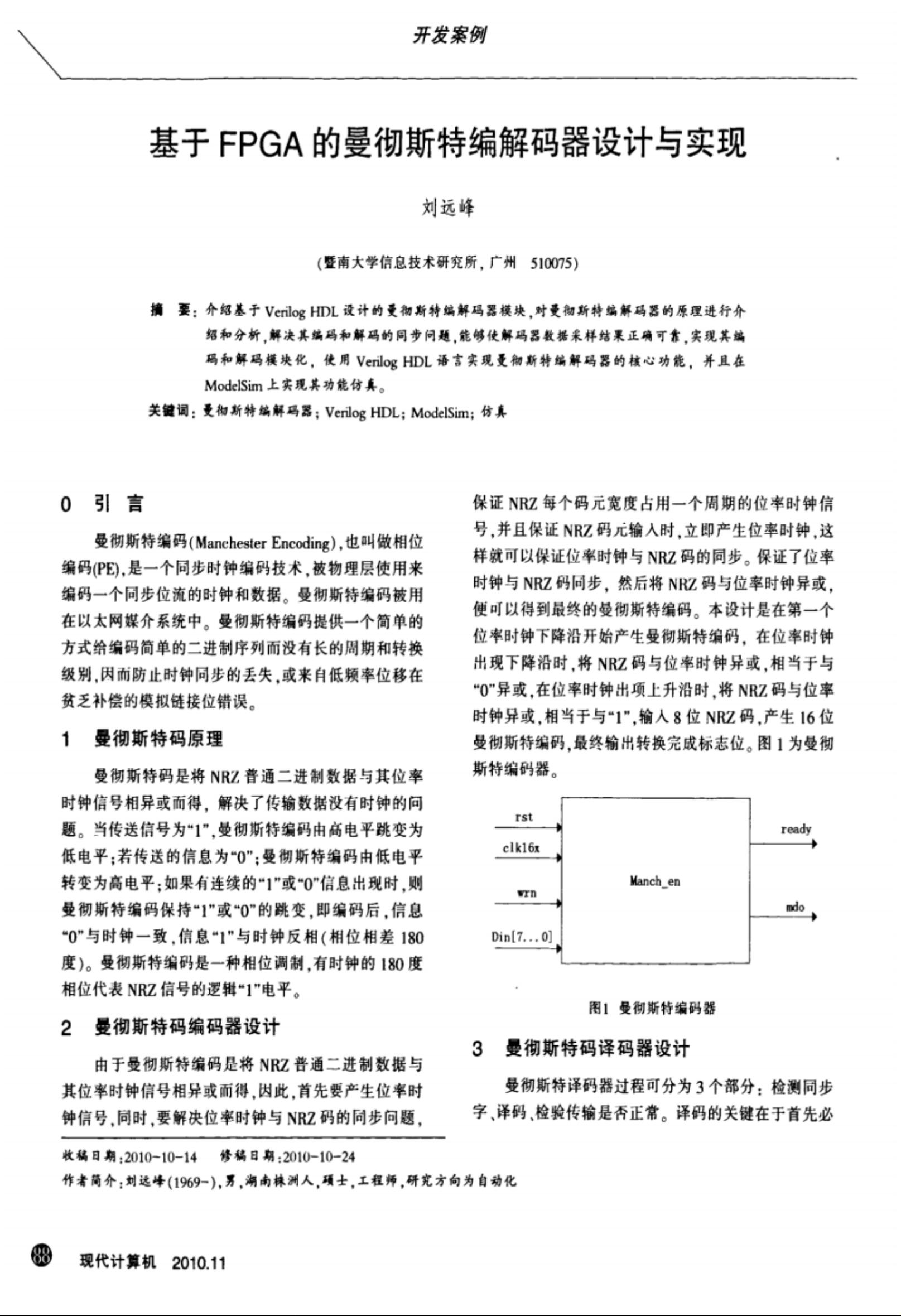

本文主要探讨了如何在FPGA(Field-Programmable Gate Array,现场可编程门阵列)上设计和实现曼彻斯特编码的解码器。曼彻斯特编码是一种同步数据传输编码方式,它在每个时钟周期的中间改变信号电平,以此来同时携带时钟信息和数据信息,确保数据传输的同步性,常用于局域网通信中。

曼彻斯特编码的特点是每个数据位的中间有电平翻转,如果前半个周期和后半个周期的电平相同,则表示0;相反,如果电平不同,则表示1。这种编码方式的优点在于能够自同步,即使在接收端丢失时钟信号的情况下,也能通过检测电平变化来恢复时钟,从而保证数据的正确解码。

在FPGA中实现曼彻斯特解码器,通常需要以下步骤:

1. **信号采样**:首先,需要对输入的曼彻斯特编码信号进行定时采样,通常在时钟周期的中间点进行,以获取信号的电平状态。

2. **电平比较**:比较前后两个采样点的电平,根据电平是否变化来判断数据位是0还是1。

3. **时钟恢复**:利用电平变化来恢复时钟信号,确保解码过程的同步。

4. **数据解码**:根据恢复的时钟,将连续的电平变化转换为原始的数据流。

文章可能提到了使用硬件描述语言(如Verilog HDL)来编写解码器的逻辑代码。Verilog HDL是一种用于描述数字系统的硬件级编程语言,可以用来定义电路的结构和行为,非常适合FPGA的设计。

在文中,作者可能讨论了具体的设计流程、代码实现细节以及可能遇到的问题,如信号同步、噪声处理、时序分析等。此外,还可能介绍了仿真验证的方法,以确保设计的正确性。参考文献中列举的书籍和论文提供了关于Verilog HDL的基础知识和实际应用,以及曼彻斯特编码和FPGA设计的相关资料,这些对于深入理解该主题非常有帮助。

通过阅读这些相关文献,读者可以了解到更多关于FPGA实现曼彻斯特编码器和解码器的技术细节,以及在实际应用中如何解决相关问题。例如,董健等人和林艺文等人分别研究了基于FPGA的曼彻斯特编解码器,而付林等人则探讨了FPGA技术在曼彻斯特编码器设计中的应用,这些研究都为理解曼彻斯特编码在实际系统中的实现提供了宝贵的经验和案例。

2023-04-21 上传

2023-06-11 上传

2023-06-09 上传

2023-05-19 上传

2023-06-12 上传

2023-06-09 上传

2023-09-27 上传

weixin_40369569

- 粉丝: 1

- 资源: 3

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析