优化逐次逼近ADC基准电压源设计:挑战与解决方案

54 浏览量

更新于2024-09-01

收藏 367KB PDF 举报

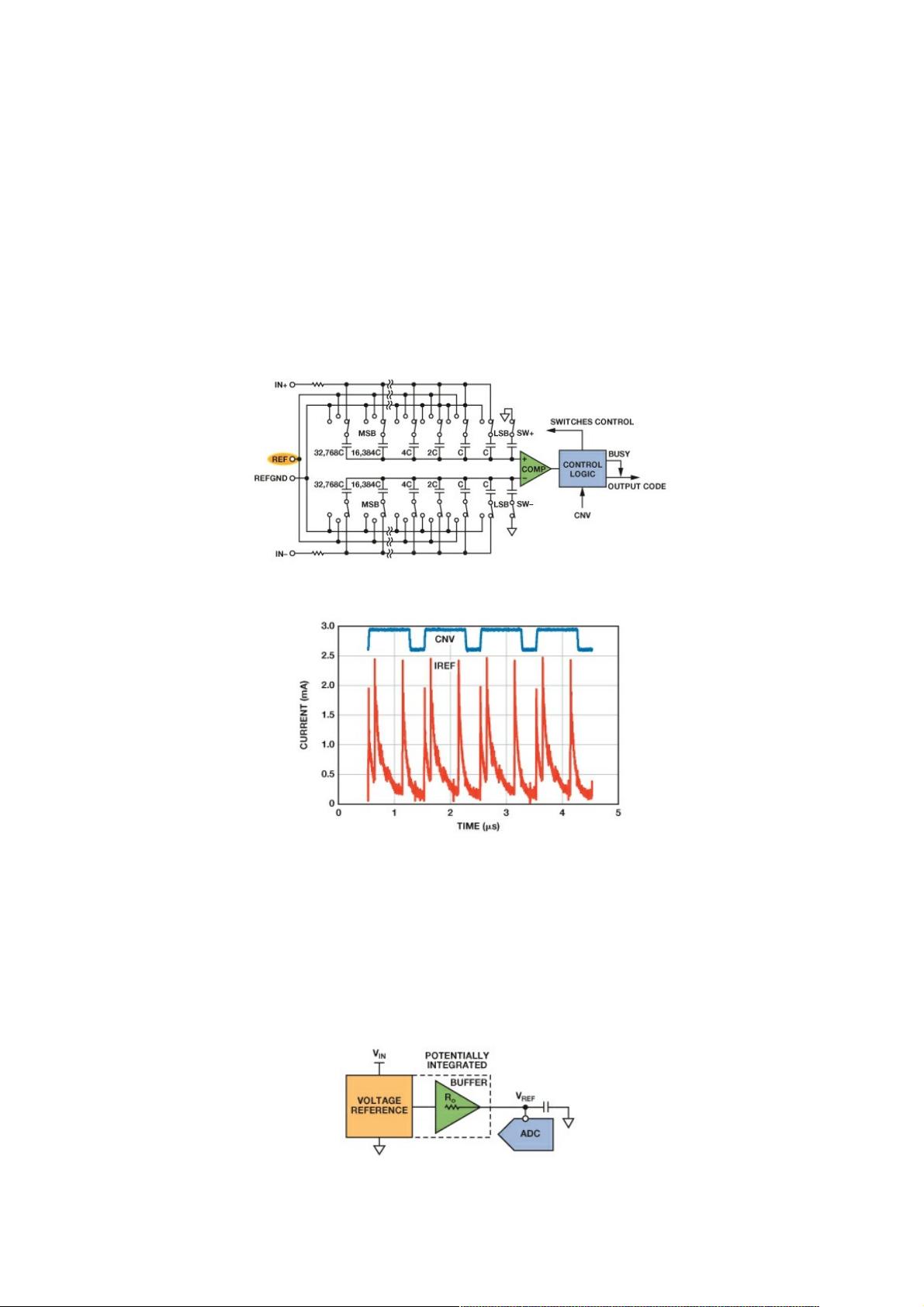

本文主要研究的是基于精密逐次逼近型ADC(Analog-to-Digital Converter)的基准电压源设计。高分辨率的ADC性能高度依赖于基准电压源的精度、稳定性和驱动能力。逐次逼近型ADC在工作过程中,基准电压输入端的开关电容会形成动态负载,这要求基准电压源电路能够处理与时间(转换周期)和吞吐速率(采样频率)相关的电流变化。

在ADC转换期间,例如16位的AD7980逐次逼近型ADC,基准电压输入处的电流峰值可高达2.5mA,这对基准电压源的电流供应能力提出了严峻考验。为了减小电流尖峰对基准电压的影响,通常会在基准电压输入附近放置一个高容量、低等效串联电阻(ESR)的储能电容,如10微法(µF)或更大,以平滑电流负载并减轻基准电压源的压力。然而,过大的电容可能导致稳定性问题,因为它们可能储存过多的电荷,从而影响基准电压的稳定性。

基准电压源的设计挑战包括确保在高吞吐率下提供足够的平均电流,例如AD7980在1MSPS下典型基准电流为330微安(μA),同时还要避免基准电压在转换间歇期下降过多。为了实现最佳性能,许多ADC芯片虽然内置了基准电压源和缓冲器,但在某些情况下,外部基准电压源电路仍然是优化性能的关键。

此外,设计者还需考虑功耗控制,因为在两次转换之间基准电压源应尽量不消耗电流。基准电压源电路的噪声抑制也是设计中的重要因素,因为基准电压的稳定性直接影响到整个ADC的信号质量。本文深入探讨了这些设计挑战,旨在为高精度ADC的基准电压源开发提供理论指导和技术支持,对于提高ADC的整体性能和可靠性具有重要的实践价值。

2020-08-28 上传

2020-04-20 上传

2020-10-18 上传

2020-06-22 上传

2020-10-20 上传

点击了解资源详情

2020-07-15 上传

2021-01-20 上传

weixin_38748210

- 粉丝: 5

- 资源: 927

最新资源

- 专用虚拟局域网(PVLAN)技术与应用.pdf

- IReport用户手册

- 最新的Prototype框架版本1.5.0的API帮助文档(英文原版)。

- 最新的Prototype框架版本1.5.1的API帮助文档(英文原版)。

- 最新的Prototype框架版本1.6.0的API帮助文档(英文原版)。

- 基于单片机的八路竞赛抢答器

- 柱透镜光栅用于显示综述

- suse+linux+10+下安装+oracle9i数据包

- Thinking.In.Java.3rd

- CLIPS-自定义模板属性

- 侯捷的MFC part2

- SharpMap程序开发实例图文教程

- 深入浅出MFC part1

- Vim用户手册中文版 7.2

- 计算机外文翻译C#外文翻译

- TMS320C6000