VHDL设计16位全加器:0.18μm CMOS工艺与性能优化

版权申诉

15 浏览量

更新于2024-06-25

收藏 963KB PDF 举报

本资源是一份关于使用VHDL语言实现16位全加器的设计报告,由托列吾别克·马杰尼在电路与系统01班完成,于2013年11月24日。设计题目旨在让学生熟悉CMOS数字集成电路设计的流程,包括功能验证、VHDL/Verilog建模、同步电路设计、性能评估等各个环节。目标是设计一个16位全加器,采用0.18μm数字CMOS工艺,并通过Synthesis工具进行功能验证、电路合成以及性能检测。

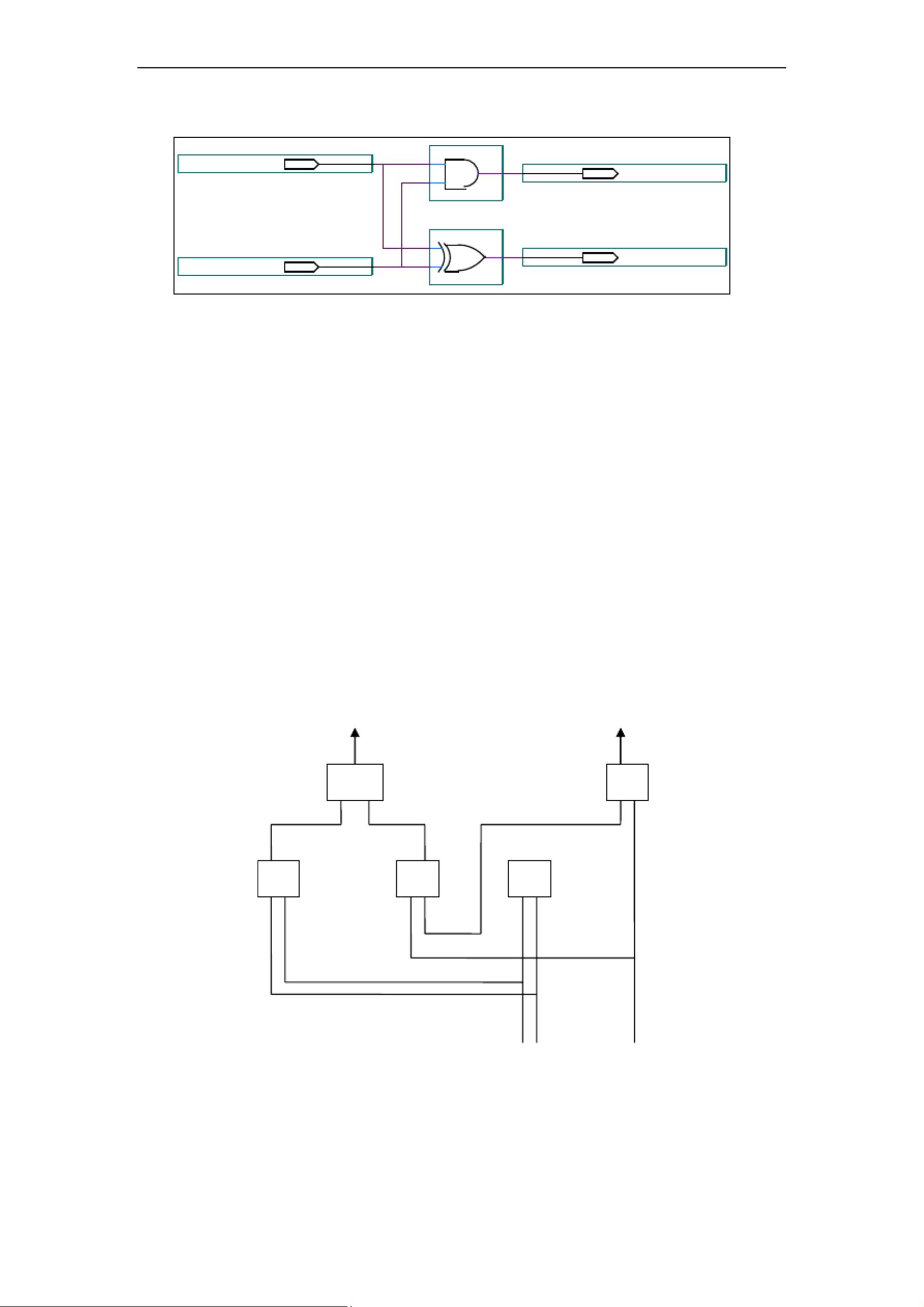

全加器是组合逻辑电路的核心模块,用于执行加法运算,特别关注高位进位。全加器可以分为并行和串行两种类型,前者在高位进位时同时处理,后者按照位序逐个进行。为了提高运算效率,报告提到了超前进位加法器的概念,它减少了进位信号传递时间,从而提升运算速度。

设计的关键部分是16位全加器的实现。首先,设计者需要根据加法运算的逻辑关系,创建真值表,然后利用这些信息写出逻辑函数表达式,绘制逻辑电路图。接下来,使用VHDL编程语言编写程序,将逻辑设计输入到QUARTUSⅡ等模拟工具中进行验证,确保其正确性和性能指标,如工作频率、功耗和物理面积等。

半加器是全加器的基础,它是没有考虑低位进位的简单加法操作。通过半加器,可以进一步理解全加器的工作原理,通过分析半加器的真值表和逻辑表达式,构建出更复杂的全加器设计。

这份报告涵盖了从理论分析到实际设计的全过程,对于学习和实践VHDL在16位全加器设计中的应用具有很高的参考价值,对于理解数字电路设计流程和技术细节有着重要的指导作用。

471 浏览量

305 浏览量

107 浏览量

2021-11-09 上传

2023-03-04 上传

2024-11-17 上传

2021-10-19 上传

hhappy0123456789

- 粉丝: 77

- 资源: 5万+

最新资源

- ajax ibm教程

- 清理乳峰让你的电脑飞起来,绝对是好的,大家看看吧

- s3c6410 user manual 1.0

- 00885a_cn00885a_cn

- Learning the vi editor 6th edition

- J2EE完全参考手册

- windows API 参考大全

- C#基础教程(.NET编程语言)

- ModBus通信协议.pdf

- 单片机应用编程技巧 (FAQ).pdf

- 源代码就是设计,真的

- 网络工程师试题2004-2007(有详细解答)

- R语言——参考卡片——R语言的参考资料

- Image Analysis Using a dual-tree M-band wavelet transform

- JavaScript实用技巧集锦

- 一些容栅传感器的资料