Quartus II与ModelSim仿真步骤详解

下载需积分: 0 | DOCX格式 | 198KB |

更新于2024-08-04

| 65 浏览量 | 举报

"Quartus II 是Altera公司的一款综合、适配、编程和调试工具,常用于FPGA设计。ModelSim是一款强大的硬件描述语言(HDL)仿真器,能够支持VHDL和Verilog等语言。本摘要将详细介绍如何在Quartus II中调用ModelSim SE进行仿真操作。"

在进行FPGA设计时,Quartus II 提供了丰富的IP CORE资源,简化了设计流程。然而,当需要验证设计的逻辑功能时,就需要进行仿真。以下是在Quartus II中调用ModelSim SE进行仿真的详细步骤:

1. 首先,创建一个新的工程,并将所需的IP CORE添加到工程中。这可以通过点击“File”菜单中的“New Project Wizard”,然后选择相应的IP CORE来完成。

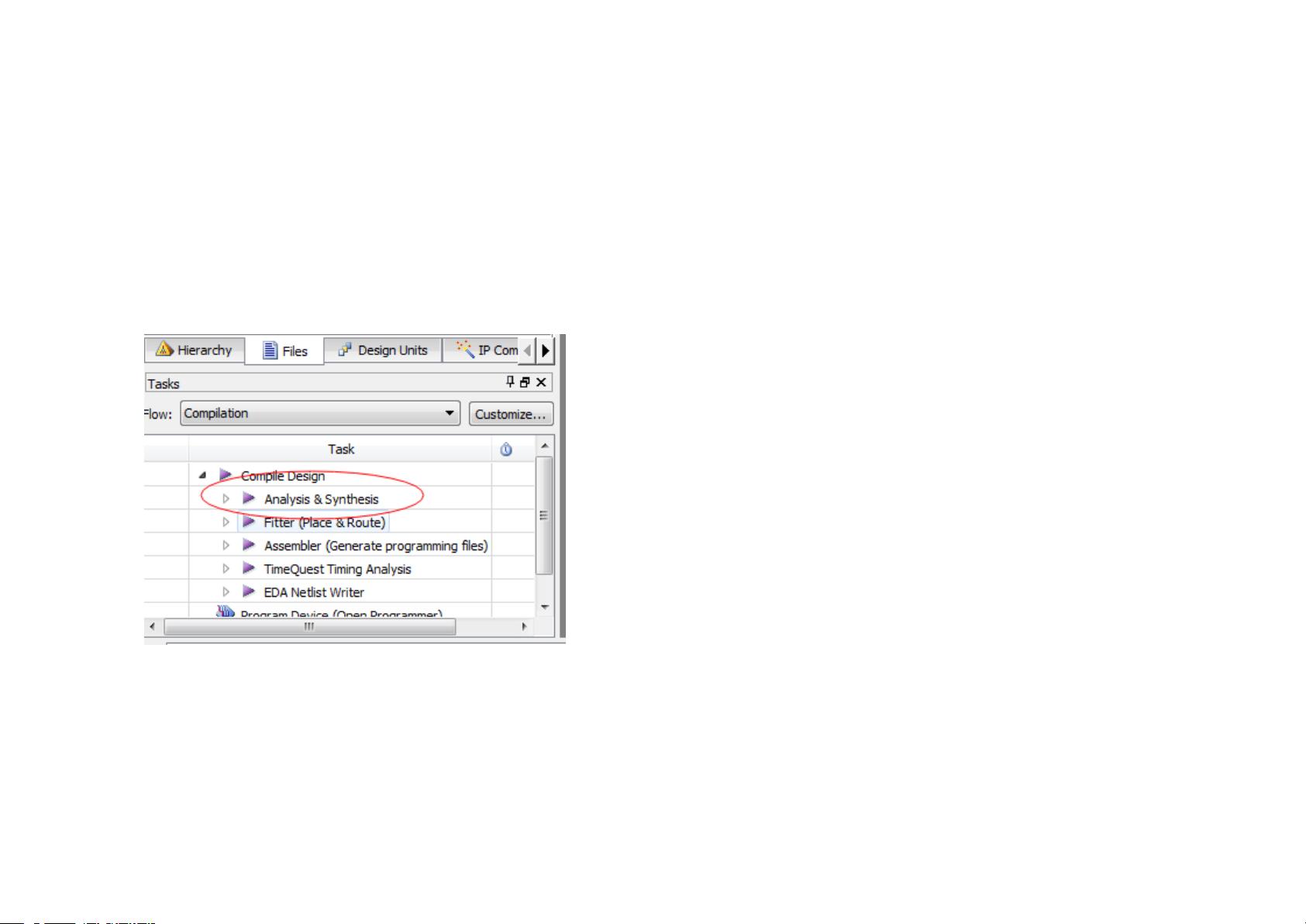

2. 完成IP CORE的添加后,进行编译。点击“Task”菜单中的“Analysis & Synthesis”以对设计进行综合,确保设计符合目标FPGA的资源限制。

3. 接下来,配置ModelSim仿真环境。在“Tools”菜单中选择“Options”,然后进入“EDATool Options”。在这里,指定ModelSim的安装路径,通常为包含`.exe`可执行文件的目录,可能是`/win32`或`/win64`。

4. 在“Assignments”菜单中,选择“Settings”,进一步设置仿真选项。在“EDATool Settings”的“Simulation”部分,可以调整仿真时钟周期,如将“Timescale”设置为1ns,以适应设计需求。

5. 运行“Start Testbench Template Writer”(在“Processing”->“Start”下)。这将自动生成一个测试模板文件,文件扩展名为.vt,位于工程的“simulation\modelsim”子目录下。

6. 使用文本编辑器(如Quartus II内置的文本编辑器或外部的vim编辑器,需要更改.vt文件扩展名为.v以获得更好的查看效果)打开这个测试模板文件,编写或修改测试激励,以驱动设计中的信号。

7. 在“Assignments” -> “Settings” -> “EDATool Settings” -> “Simulation”中,添加测试文件。点击“TestBenches”选项,然后选择“New”,导入刚创建的测试模板文件(.vt文件)并指定测试模块名称。

8. 最后,开始仿真。在“Tools”菜单中选择“Run” -> “Simulation Tool”,ModelSim会启动并运行仿真。如果对默认优化的波形不满意,可以手动停止仿真(通过“End Simulation”),然后按照常规的仿真步骤继续操作,以获取所需的仿真结果。

通过以上步骤,用户可以在Quartus II中方便地调用ModelSim SE进行逻辑仿真,验证设计的正确性。这个过程对于FPGA开发来说至关重要,因为它允许设计师在实际硬件编程之前发现并修复潜在的设计错误。

相关推荐

13572025090

- 粉丝: 853

最新资源

- C#高效多线程下载器组件源码V1.12发布

- 32位Windows汇编语言程序设计大全

- Sketch插件库替换器:简化库更换流程

- 首版投资组合网站的开发与部署指南

- C语言实现农历与阳历转换的新库发布

- 探索Linux下的Vim优雅配色方案:Colibri.vim

- STM32 TFT显示技术与刷屏方法解析

- STM32单片机控制交通灯毕设资料整合

- Vitamio实现后台Service播放m3u8音频流

- 使用Docker封装的Alpine版Vim体验

- 步步高高级版WarNards开源项目发布

- 使用JNI实现Java调用VC6 DLL与Linux SO的DEMO教程

- STM32与OLED显示技术的实践应用

- 全面技术覆盖的小区物业管理系统设计与源码

- 清华版编译原理专业课答案解析

- Linux系统下nginx添加SSL配置的详细步骤