"Verilog HDL基本语法与抽象级别说明"

需积分: 50 98 浏览量

更新于2024-01-22

1

收藏 903KB DOC 举报

FPGA基本语法是指在FPGA(Field-Programmable Gate Array)中使用的一些基本语法和规则,用于描述和设计数字逻辑电路。本文将对FPGA基本语法进行详细介绍。

首先,在FPGA中使用的主要语言之一是Verilog HDL(Hardware Description Language),它是一种用于数字逻辑电路设计的语言。Verilog HDL可以用来描述和建立电路的模型,其中包含了电路的行为描述和结构描述。

Verilog HDL既可以用来进行电路的行为描述,也可以用来进行电路的结构描述。行为描述是指使用代码描述电路的功能,例如实现逻辑运算、数学运算等。结构描述是指使用代码描述电路的组成结构,包括元器件和它们之间的连接关系。

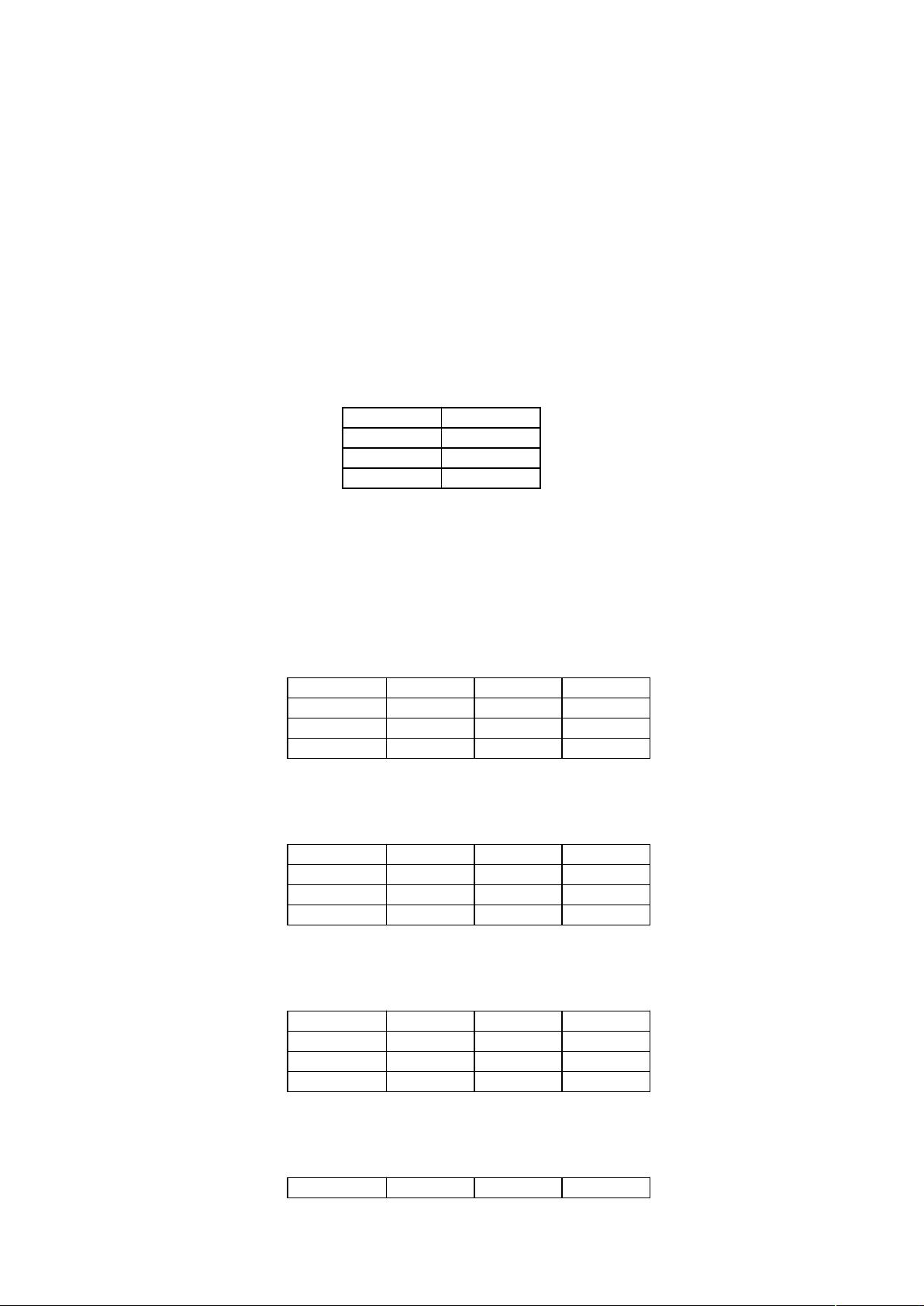

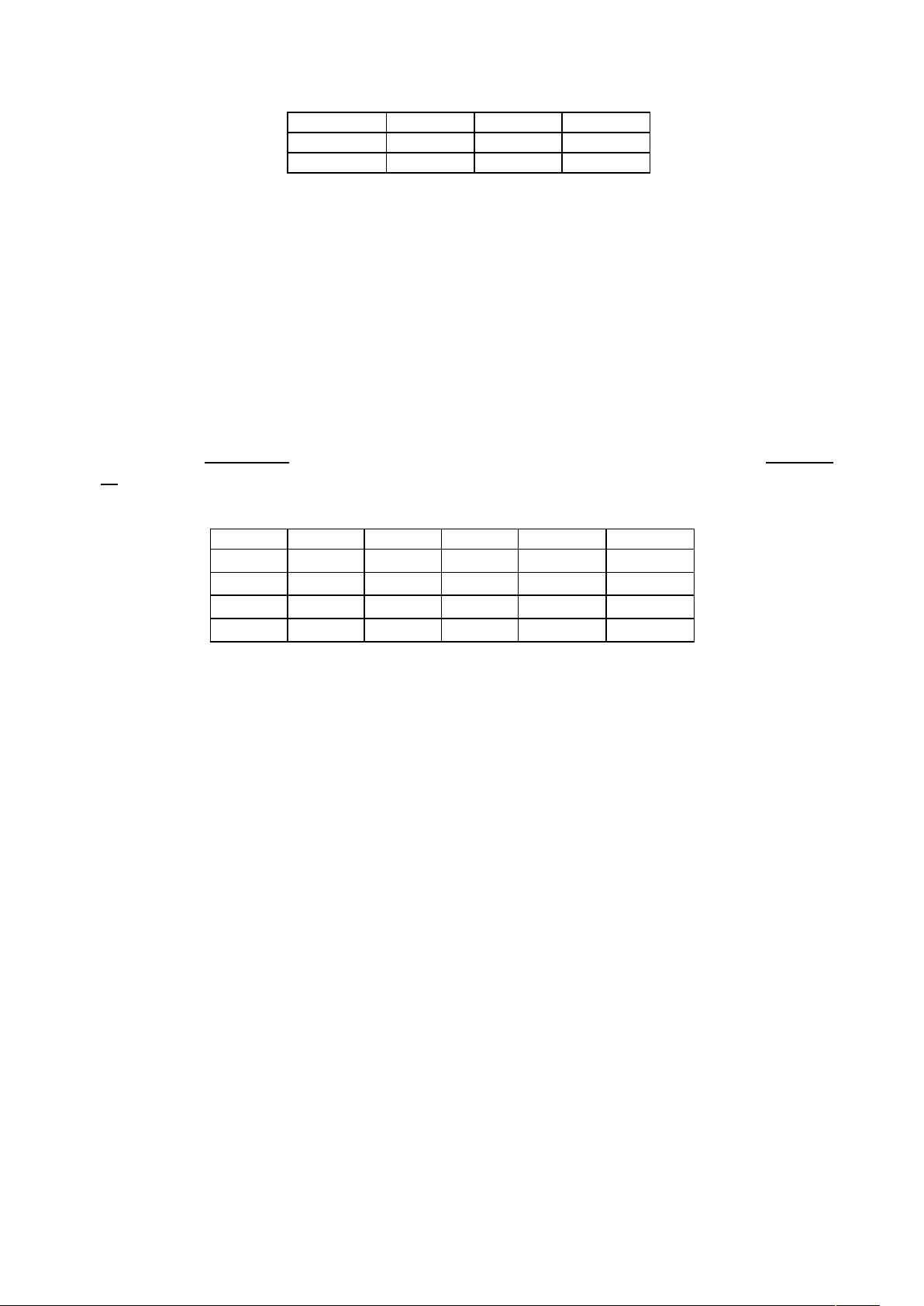

在Verilog HDL中,可以使用不同级别的抽象来建立电路的模型。这些抽象级别包括系统级、算法级、RTL级、门级和物理级。

系统级是抽象级别中最高级别的一种,它用高级语言结构来实现设计模块的外部性能的模型。系统级抽象主要关注整个系统的功能和性能等方面,而不关注具体的电路实现细节。

算法级是在系统级之下的一种抽象级别,它用高级语言结构来描述电路的设计算法。在算法级抽象中,重点关注电路设计的算法和计算过程,而对具体的电路实现细节不关心。

RTL级(Register Transfer Level)是在算法级之下的一种抽象级别,它用来描述数据在寄存器级别上的传输和转换过程。在RTL级抽象中,电路被描述为一系列寄存器之间的数据传输和逻辑运算,更加接近于最终的硬件实现。

门级是在RTL级之下的一种抽象级别,它用逻辑门和触发器等基本元器件来建立电路模型。在门级抽象中,电路被描述为逻辑门之间的连接和触发器的状态转换,进一步接近了实际的硬件实现。

物理级是抽象级别中最底层的一种,它用到了实际的物理接口和元器件参数来描述电路模型。在物理级抽象中,电路被描述为具体的器件布局和电路之间的位置和连接关系。

总之,FPGA基本语法包括了Verilog HDL的基本语法规则和不同抽象级别的使用方法。通过学习和理解FPGA基本语法,可以更加准确地描述和设计FPGA中的数字逻辑电路。

2020-08-04 上传

2024-07-04 上传

2022-12-29 上传

2021-10-02 上传

点击了解资源详情

ken108

- 粉丝: 2

- 资源: 1

最新资源

- 王珊 高等教育出版社 数据库第四版答案

- .net 软件自动化测试之道 pdf (.net平台下自动化测试必备之资料,精!!)

- 基于模糊预测算法的ATO仿真研究

- 3g技术讲解通信工程

- c#各种排序算法大全

- Cognos8.4新增功能优势说明

- JAVA基础面试题部分参考

- 段程序保存为文件名为Test.java的文件

- 影碟出租管理信息系统

- JAVA的学习笔记及开发模式

- Learning Oracle PL-SQL [O'Reilly, 524s, 2001r].pdf

- flash 适合于初学者的程序设计教程

- Visual C++开发工具与调试技巧整理

- 操作系统中的银行家算法

- Redhat Linux 9教学讲义

- RSVP协议端到端QOS控制机制的研究