VerilogHDL建模技巧探索与实践

"VerilogHDL那些事儿_建模篇v5"

在深入探讨VerilogHDL建模之前,我们首先要理解VerilogHDL是一种硬件描述语言,用于设计和实现数字系统,特别是在FPGA(Field-Programmable Gate Array)和ASIC(Application-Specific Integrated Circuit)领域。"建模"在VerilogHDL中至关重要,因为它允许设计者用抽象的方式描述电路的行为和结构,如同用积木搭建复杂的模型。

建模在VerilogHDL中分为不同的层次,主要包括门级建模、寄存器传输级(RTL)建模和行为级建模。门级建模直接对应于逻辑门电路,而RTL建模则更关注数据流和控制流,是大多数设计者最常使用的层次。行为级建模则允许使用更高级的算法描述,但通常需要在后期进行综合以转化为更低层次的表示。

学习VerilogHDL时,许多初学者感到困惑的原因在于,没有掌握有效的建模技巧。这可能导致理解困难,甚至产生对复杂源代码的恐惧感。建模技巧的关键在于代码的可读性、可维护性和模块化。编写清晰、结构化的代码能让其他开发者更容易理解你的设计意图,这对于团队合作和项目维护至关重要。

建模技巧包括以下几个方面:

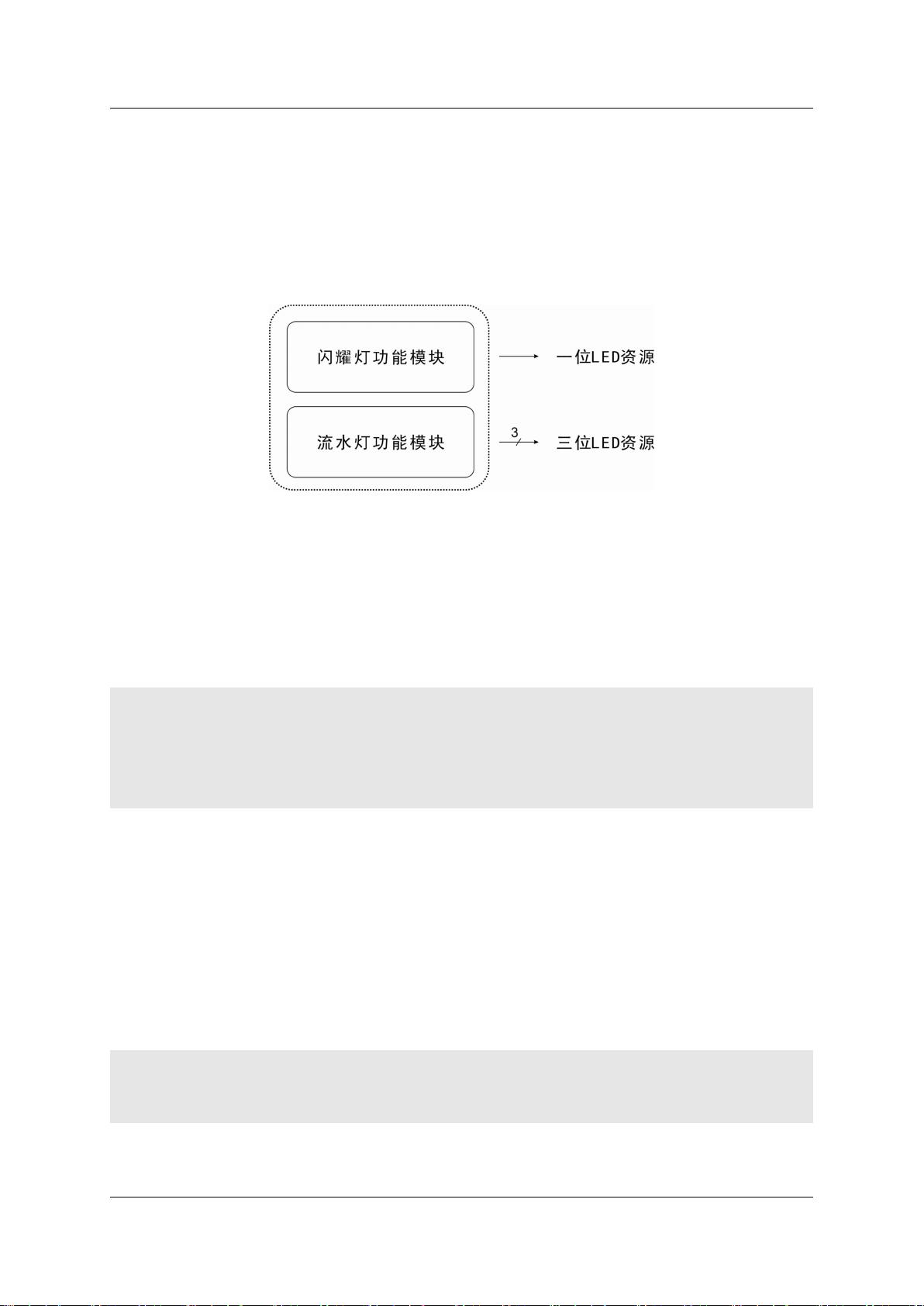

1. **模块化**:将设计分解为小的、独立的模块,每个模块负责特定的功能。这有助于降低复杂性,提高复用性。

2. **接口定义**:清晰定义模块的输入和输出,使其易于与其他模块连接。

3. **注释**:添加适当的注释来解释模块的功能和操作,帮助阅读者理解代码。

4. **命名规范**:使用有意义的变量和模块名,避免使用过于抽象或模糊的名称。

5. **数据流控制**:合理使用各种控制语句(如always块),确保数据流的清晰。

6. **避免硬编码**:减少在代码中直接使用硬编码数值,以增加代码的灵活性和可配置性。

7. **测试平台**:创建测试平台来验证模块的功能,确保设计正确无误。

8. **时序分析**:虽然在建模初期可能不涉及,但理解时序概念有助于写出符合实际时序特性的代码。

9. **仿真**:通过功能仿真检查设计的正确性,及时发现并修复问题。

对于初学者来说,理解并实践这些建模技巧能显著提高学习效果。通过不断的练习和参考优秀的设计,可以逐步建立起对VerilogHDL的深入理解和应用能力。不要害怕面对复杂的源码,而应将其视为提升自己建模技巧的机会。只有掌握了建模技巧,才能真正驾驭VerilogHDL,将设计理念转化为实际的硬件实现。

点击了解资源详情

164 浏览量

点击了解资源详情

2013-06-06 上传

116 浏览量

2019-07-11 上传

2018-05-03 上传

136 浏览量

107 浏览量

oTuiMo

- 粉丝: 0

最新资源

- iBATIS 2.0开发指南:入门与高级特性的全面解析

- ESRI Shapefile技术描述详解

- MIF格式详解:GIS地图交换标准

- WEB标准解析与网站重构实践

- 深入解析JUnit设计模式

- PowerDesigner 6.1数据库建模详解与教程

- Spring框架开发者指南(中文版)

- 中文Vim教程:实践导向的手册

- Jboss EJB3.0 实例教程:从入门到精通

- Ant入门与高级应用指南

- Linux系统移植实战:从Bootloader到交叉工具链

- 数缘社区:数学与密码学资源宝库

- ADO.NET深度探索:连接、执行与数据处理

- Eclipse基础入门:集成开发环境详解

- Oracle动态性能视图详解与使用

- Java开发必备:字符串处理与日期转换技巧