ALTERA FIFO IP核用户指南:9.0版详解与应用

需积分: 0 187 浏览量

更新于2024-07-27

收藏 1MB PDF 举报

Altera IP核使用手册是一份详细介绍了由Altera公司提供的FIFO(First-In-First-Out,先进先出)功能IP核的用户指南。这份文档的发布日期为2009年3月,适用于MegaCore版本9.0,地址位于101 Innovation Drive, San Jose, CA 95134。Altera是知名的可编程解决方案提供商,其商标和服务标志在全球范围内享有高度认可。

FIFO是一种数据结构,常用于在系统间传递数据,按照先进先出的原则进行存取操作。在这份手册中,用户可以了解到如何有效地利用Altera提供的FIFO IP核来优化系统设计,包括但不限于IP核的安装、配置、性能优化以及接口使用方法。IP核的HyperTransport技术使得数据传输速度和效率得到了提升,这对于处理实时或高带宽需求的应用场景尤其重要。

该手册覆盖了以下几个关键知识点:

1. **IP核概述**:解释了FIFO IP核的功能原理,它是如何在Altera的FPGA或CPLD平台中实现高效的存储和数据流管理的。

2. **硬件描述**:详细介绍FIFO IP的核心组件,如数据输入端口、数据输出端口、控制逻辑等,并说明其工作原理。

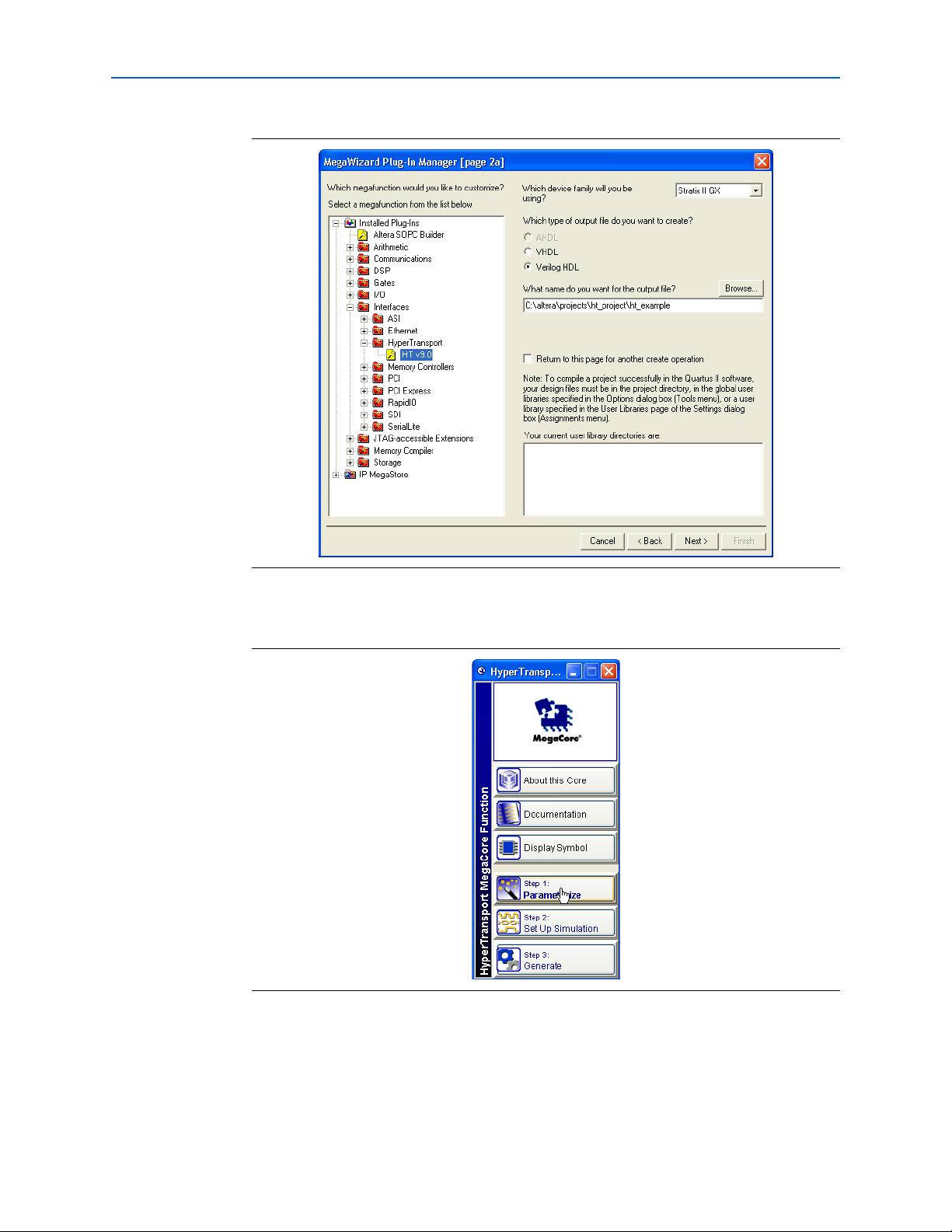

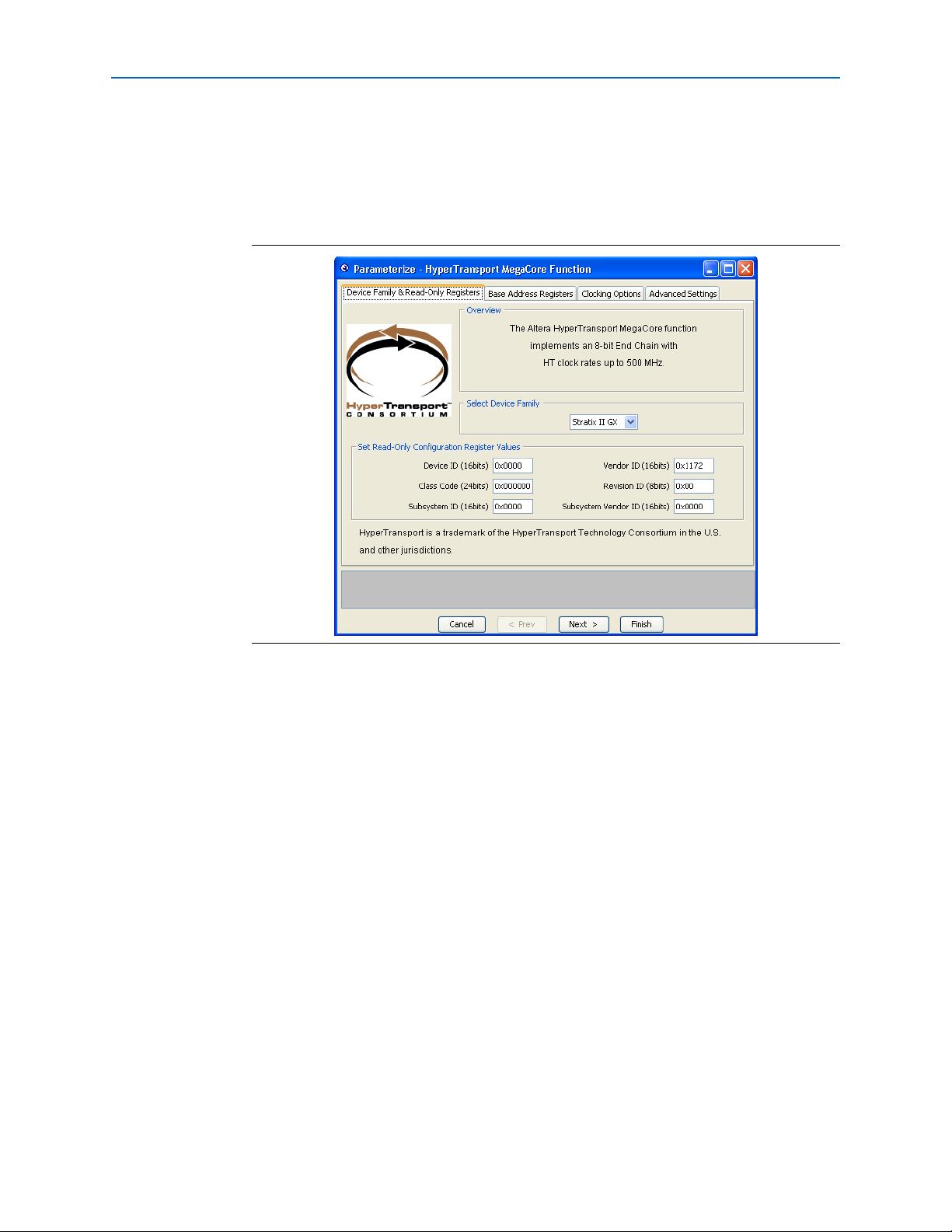

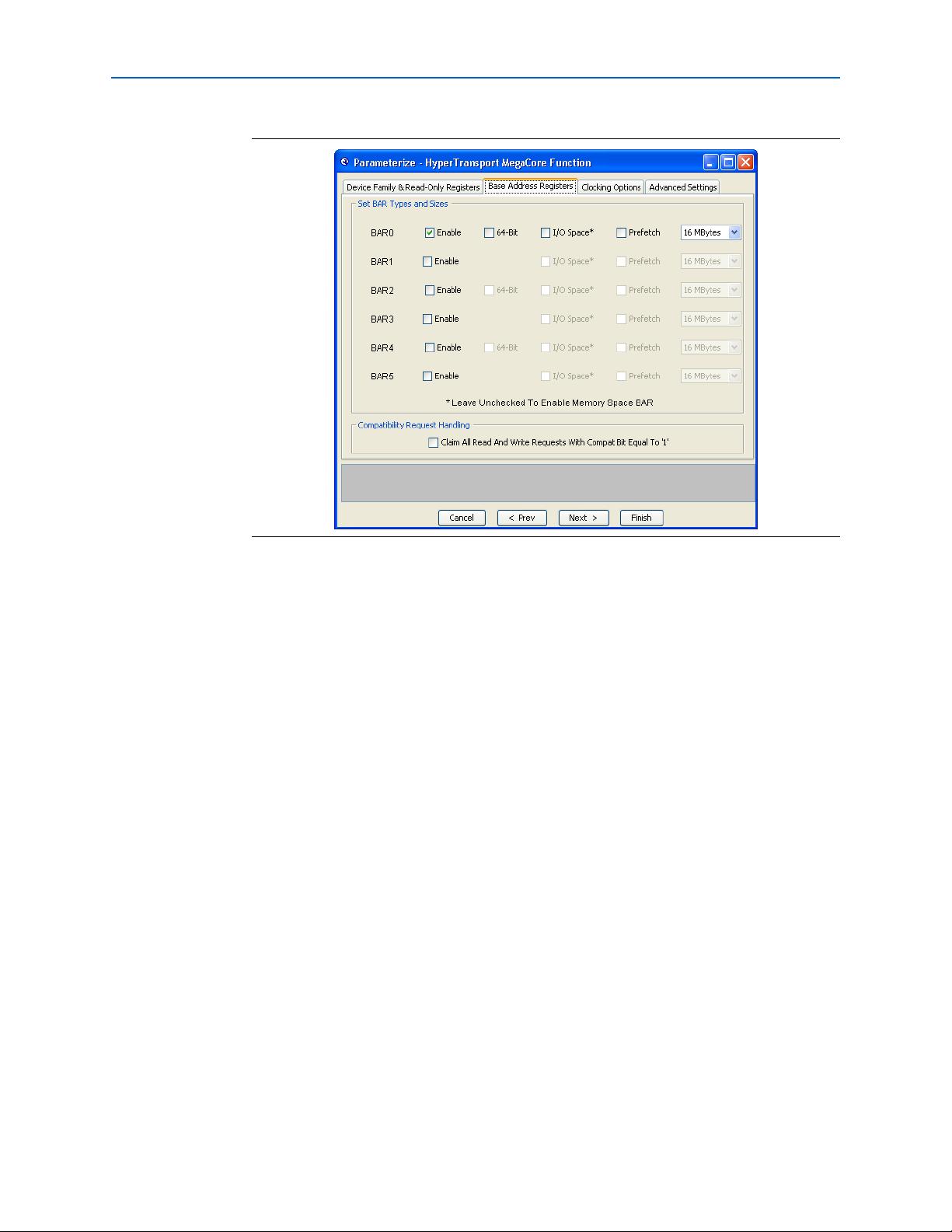

3. **配置和参数设置**:指导用户如何配置FIFO的容量、宽度、深度等关键参数,以适应不同的应用需求。

4. **接口设计**:如何与外部模块(如处理器、外围设备)正确地连接和通信,确保数据的有序流动。

5. **性能优化**:提供了关于减少延迟、提高吞吐量的建议,以及可能遇到的问题及其解决策略。

6. **错误处理和调试**:包含故障排查和调试技巧,帮助用户识别和修复潜在问题。

7. **版权和许可**:明确了使用这份文档和IP核的法律条款,强调了Altera的保修政策以及知识产权保护。

8. **注意事项**:警告用户在未经书面同意的情况下,不得擅自修改或复制Altera的产品和服务,以确保合规性和技术支持。

这本手册是硬件工程师和系统集成者深入理解和利用Altera FIFO IP核的必备参考资料,它不仅提供了技术细节,还强调了实际应用中的最佳实践和安全考虑。通过阅读和遵循手册中的指导,用户可以更加高效地在Altera FPGA或CPLD项目中集成和优化FIFO功能。

2015-09-07 上传

2013-08-02 上传

2014-07-14 上传

152 浏览量

2021-07-07 上传

2018-01-19 上传

2010-04-16 上传

shuchengbai

- 粉丝: 0

- 资源: 1

最新资源

- 开源通讯录备份系统项目,易于复刻与扩展

- 探索NX二次开发:UF_DRF_ask_id_symbol_geometry函数详解

- Vuex使用教程:详细资料包解析与实践

- 汉印A300蓝牙打印机安卓App开发教程与资源

- kkFileView 4.4.0-beta版:Windows下的解压缩文件预览器

- ChatGPT对战Bard:一场AI的深度测评与比较

- 稳定版MySQL连接Java的驱动包MySQL Connector/J 5.1.38发布

- Zabbix监控系统离线安装包下载指南

- JavaScript Promise代码解析与应用

- 基于JAVA和SQL的离散数学题库管理系统开发与应用

- 竞赛项目申报系统:SpringBoot与Vue.js结合毕业设计

- JAVA+SQL打造离散数学题库管理系统:源代码与文档全览

- C#代码实现装箱与转换的详细解析

- 利用ChatGPT深入了解行业的快速方法论

- C语言链表操作实战解析与代码示例

- 大学生选修选课系统设计与实现:源码及数据库架构