CMOS逻辑电路解析:静态门、复杂门设计与应用

下载需积分: 50 | PDF格式 | 1.06MB |

更新于2024-07-15

| 11 浏览量 | 举报

"该文件详细介绍了CMOS电路结构,涵盖了静态CMOS逻辑门的基本构成、复杂CMOS逻辑门的设计分析,以及异或门、多路器、全加器的实现,并涉及类NMOS逻辑电路的相关内容。"

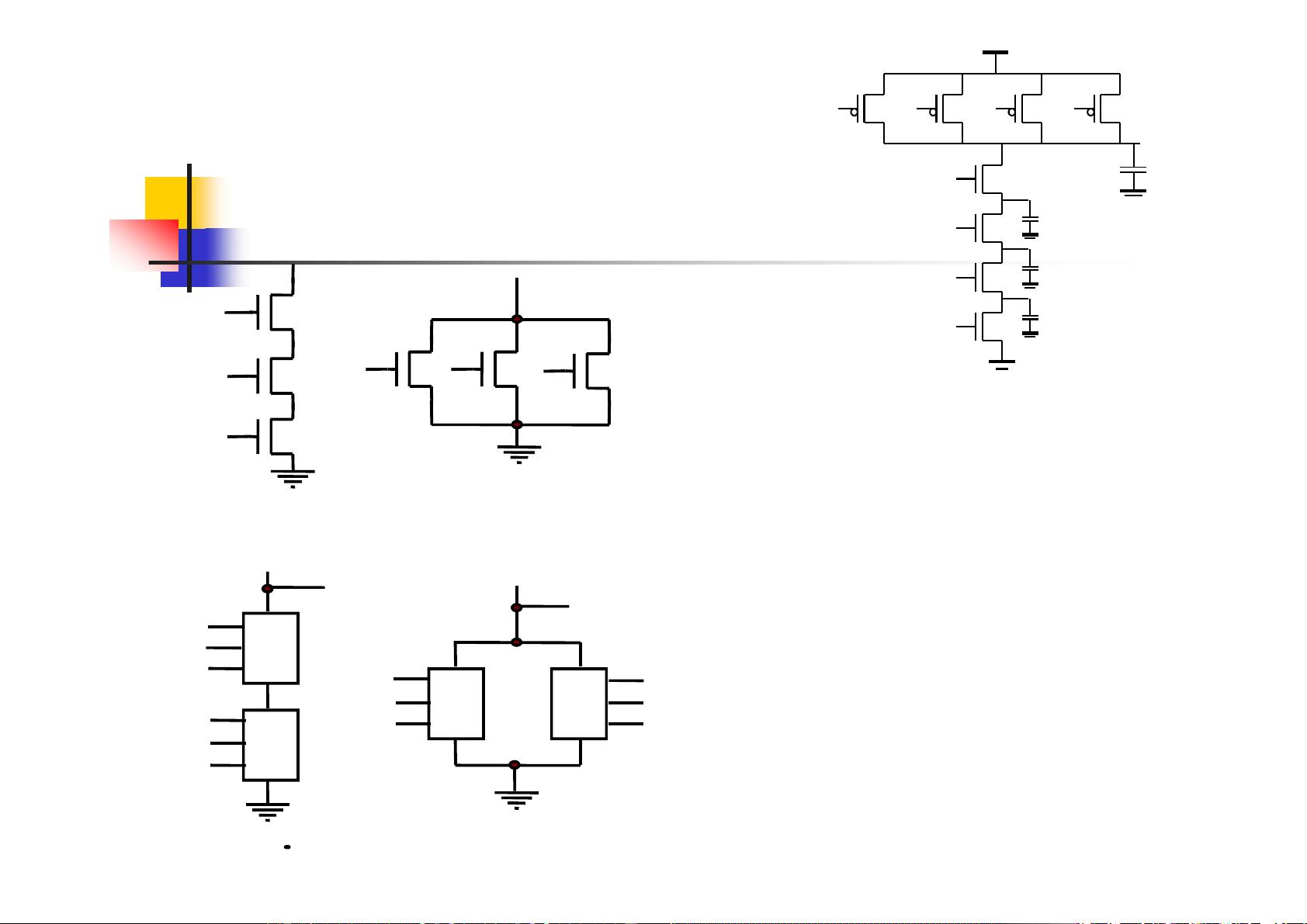

在数字集成电路领域,CMOS(互补金属氧化物半导体)技术因其低功耗和高集成度而被广泛应用。静态CMOS逻辑门是其核心组成部分,主要由PMOS(P型场效应晶体管)和NMOS(N型场效应晶体管)组成。这些逻辑门能够实现各种复杂的数字逻辑功能,如与非门、或非门等。

首先,静态CMOS逻辑门的构建原则是每个输入信号都与一个PMOS管和一个NMOS管的栅极相连。例如,对于n输入的逻辑门,将会有2n个晶体管。这种设计使得电路能够实现逻辑上的"非"功能。在图中所示的与非门中,可以看到输入A、B、C分别通过PMOS和NMOS管连接到输出端Y,且输出Y是所有输入的逻辑与非结果。

其次,逻辑函数F的实现取决于晶体管的连接方式。对于NMOS,它们通常是串联或并联,用于实现"与"或"或"操作;而对于PMOS,它们的组合可以形成串或并联,以完成相应逻辑功能。例如,一个三输入与非门(如图5所示),其输出F由三个输入A、B、C的逻辑与操作后取非得到。

此外,CMOS逻辑门还保留了CMOS反相器的特性,如低功耗和高噪声容限。这是因为当输入处于高电平时,NMOS管导通,PMOS管截止,反之亦然,这样电流主要在晶体管内部流动,而非流经电源,降低了功耗。同时,由于晶体管的互补工作模式,静态CMOS逻辑门具有良好的静态功耗性能。

文件中还提到了异或门、多路器和全加器,这些都是数字系统中的基本元件。异或门是一种能够区分输入是否相同的逻辑门,常用于数据比较和算术运算;多路器则能够根据选择信号从多个输入中选取一个信号输出,是数据路由的关键组件;全加器则可以执行二进制数字的加法运算,是构成加法器和计算器的基础。

类NMOS逻辑电路则是指那些模仿NMOS逻辑特性的电路设计,可能不完全由NMOS晶体管构成,但其工作原理和行为类似于NMOS逻辑电路。这些电路可能通过PMOS和NMOS的组合来模拟纯NMOS逻辑的功能,以满足特定应用需求或优化性能。

这份文件深入探讨了CMOS电路的基础和高级概念,对于理解和设计数字集成电路,尤其是FPGA(现场可编程门阵列)设计来说,是非常有价值的参考资料。

相关推荐

XXQ121

- 粉丝: 17

最新资源

- 支付宝订单监控免签工具:实时监控与信息通知

- 一键永久删除QQ空间说说的绿色软件

- Appleseeds训练营第4周JavaScript练习

- 免费HTML转CHM工具:将网页文档化简成章

- 奇热剧集站SEO优化模板下载

- Python xlrd库:实用指南与Excel文件读取

- Genegraph:通过GraphQL API使用Apache Jena展示RDF基因数据

- CRRedist2008与CRRedist2005压缩包文件对比分析

- SDB交流伺服驱动系统选型指南与性能解析

- Android平台简易PDF阅读器的实现与应用

- Mybatis实现数据库物理分页的插件源码解析

- Docker Swarm实例解析与操作指南

- iOS平台GTMBase64文件的使用及解密

- 实现jQuery自定义右键菜单的代码示例

- PDF处理必备:掌握pdfbox与fontbox jar包

- Java推箱子游戏完整源代码分享