Spartan™-3E开发板上的MicroBlaze SOC设计实验

"基于xilinx Spartan™-3E开发板的SOC设计"

在嵌入式系统设计领域,Soc(System on Chip)设计是将多种功能集成在同一块芯片上,包括微处理器、内存、外设接口等,以实现高度集成和低功耗的解决方案。Xilinx的Spartan™-3E系列FPGA是常用的一款低成本、高性能的可编程逻辑器件,非常适合进行SOC设计。本资料主要探讨如何在Xilinx Spartan™-3E开发板上进行SOC设计,特别是使用MicroBlaze软核处理器。

MicroBlaze是一款可配置的32位RISC处理器,由Xilinx公司提供,它可以在FPGA内部实现,为用户提供了一种灵活的、可定制的嵌入式处理解决方案。在Spartan-3E Starter Kit开发板上,MicroBlaze可以构建出一个完整的处理器系统,包含了必要的存储器、接口和外设。

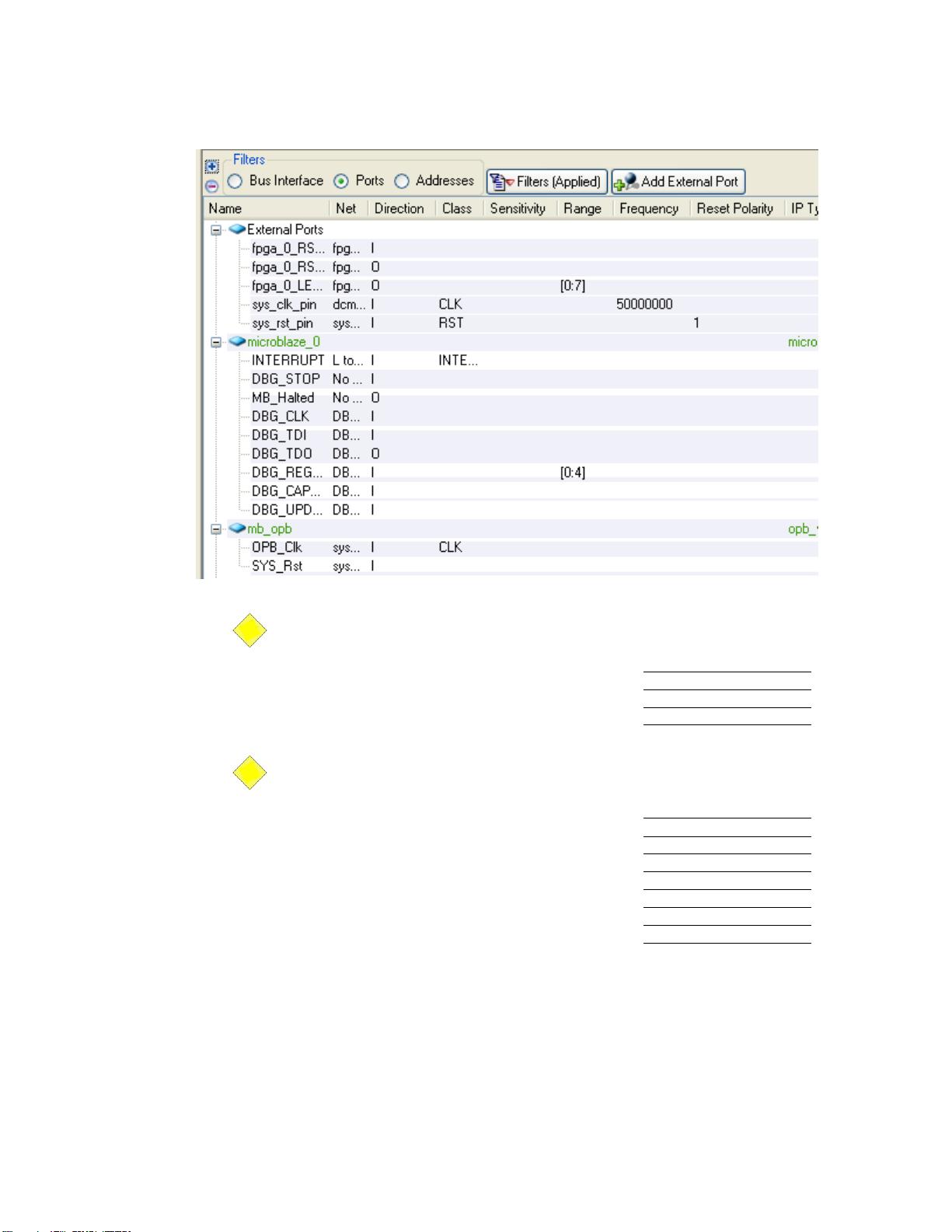

实验指导中,首先介绍了如何使用Xilinx Platform Studio (XPS)的BaseSystemBuilder (BSB)工具创建一个基于Spartan-3E Starter Kit的MicroBlaze处理器系统。这个过程涉及到以下关键步骤:

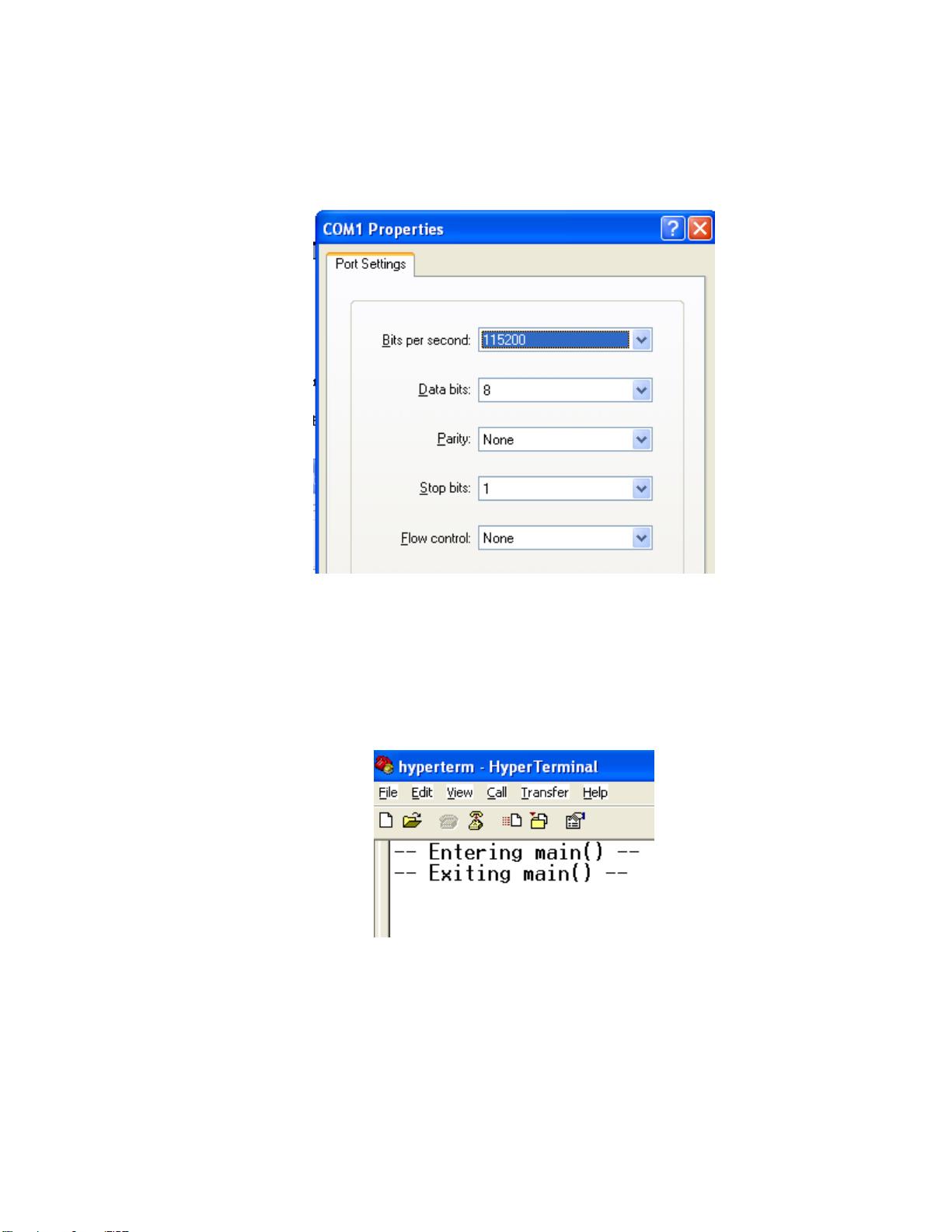

1. **创建XPS工程**:在XPS中启动一个新的工程,并选择Spartan-3E Starter Kit作为目标平台。同时,需要指定MicroBlaze处理器,以及处理器的总线时钟频率,例如50MHz。

2. **添加IP组件**:在BSB中,可以添加各种IP组件来扩展处理器的功能。例如,OPB(On-Chip Bus)总线用于连接处理器与其他模块,LMB(Local Memory Bus)用于连接本地存储器,如BRAM(Block RAM)控制器。此外,还包括UART(通用异步收发传输器)用于串行通信,GPIO(General Purpose Input/Output)用于控制LEDs或接收输入,中断控制器(INTC)、定时器和LCD接口等。

3. **分析和生成硬件设计**:在构建好系统配置后,XPS会生成一个硬件描述文件,这通常是.vhd或.bd文件,用于描述整个系统的结构。这个文件随后会被综合并实现到FPGA中。

4. **生成处理器和硬件IP网表**:完成系统配置后,XPS会生成处理器和硬件IP的网表,这些文件是VHDL或Verilog代码,用于在FPGA中实现硬件逻辑。

实验的每个阶段都有详细的指导和说明,帮助读者逐步理解并实践SOC设计的过程。每个步骤都分为概括介绍和逐步指导,以确保学习者能够逐步掌握设计的关键点。

在完成实验后,读者不仅掌握了如何使用XPS创建和配置一个基于MicroBlaze的硬件系统,还能了解如何将这些组件通过OPB、LMB等总线连接起来,形成一个完整的处理器系统。这对于进一步理解和设计复杂的嵌入式系统是非常重要的基础。此外,通过实际操作,读者还能熟悉FPGA设计流程,包括IP选型、系统集成以及硬件描述语言的应用。

101 浏览量

点击了解资源详情

193 浏览量

119 浏览量

138 浏览量

375 浏览量

2296 浏览量

156 浏览量

点击了解资源详情

shuanzi998

- 粉丝: 6

最新资源

- Premiere Pro CS6视频编辑项目教程微课版教案

- SSM+Lucene+Redis搜索引擎缓存实例解析

- 全栈打字稿应用:演示项目实践与探索

- 仿Windows风格的AJAX无限级树形菜单实现教程

- 乐华2025L驱动板通用升级解决方案

- Java通过jcraft实现SFTP文件上传下载教程

- TTT素材-制造1资源包介绍与记录

- 深入C语言编程技巧与实践指南

- Oracle数据自动导出并转换为Excel工具使用教程

- Ubuntu下Deepin-Wine容器的使用与管理

- C语言网络聊天室功能详解:禁言、踢人与群聊

- AndriodSituationClick事件:详解按钮点击响应机制

- 探索Android-NetworkCue库:高效的网络监听解决方案

- 电子通信毕业设计:简易电感线圈制作方法

- 兼容性数据库Compat DB 4.2.52-5.1版本发布

- Android平台部署GNU Linux的新方案:dogeland体验