Altera DE0实验板电路设计详解

需积分: 14 58 浏览量

更新于2024-08-01

收藏 339KB PDF 举报

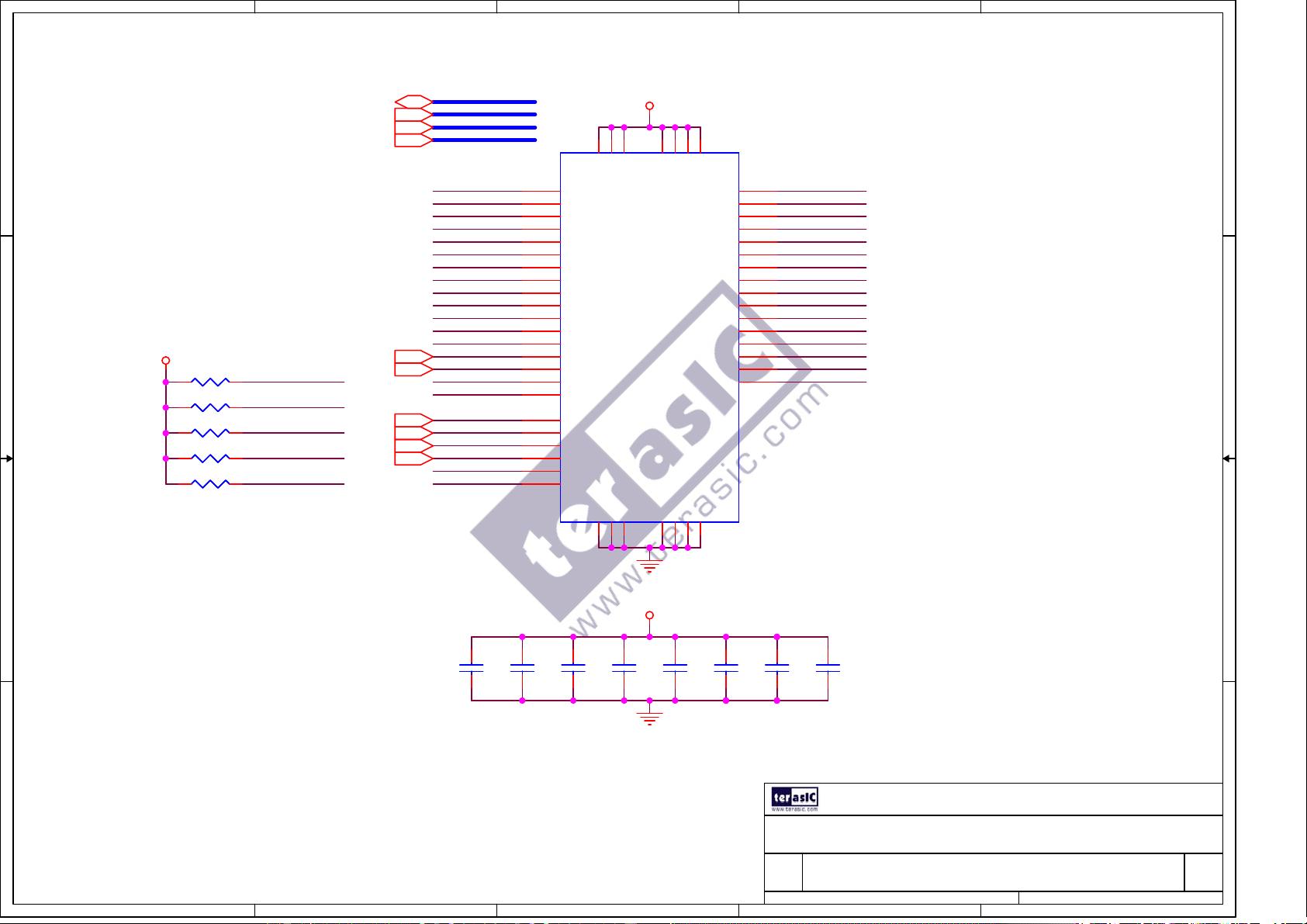

"ALTERA DE0 实验板是Terasic Technologies Inc.推出的一款基于ALTERA Cyclone III EP3C16 FPGA的开发与教育主板。电路原理图包含了该实验板的各种接口和组件,如显示模块(VGA、LED、7段数码管)、FPGA核心以及相关的支持电路。该文档可能由多个页面组成,日期标注为2009年7月3日,版权归属于Terasic Technologies Inc.,并强调未经许可不得复制或使用设计内容。"

在深入讨论ALTERA DE0实验板电路原理图之前,我们先来了解一下ALTERA DE0实验板的基础信息。ALTERA DE0是一款广泛用于教学和开发的硬件平台,它提供了丰富的外设和接口,便于用户进行数字逻辑设计的实践和学习。其核心是ALTERA的Cyclone III系列FPGA,EP3C16型号则表示该FPGA具有16K个逻辑元素。

DE0实验板的主要特点包括:

1. **ALTERA Cyclone III FPGA**:EP3C16是一个低功耗、高性能的现场可编程门阵列,能够实现复杂的数字逻辑设计。它提供了大量的可配置逻辑单元、嵌入式存储器块、乘法器以及输入/输出(I/O)引脚。

2. **显示模块**:

- **VGA接口**:允许用户实现图形输出,用于显示各种图像和视频。

- **LED**:通常包含一系列的红色和绿色LED,用于基本的二进制数据或状态指示。

- **7段数码管**:可以显示十进制数字或者简单的字母,适用于数值或字符的显示。

3. **其他接口与功能**:DE0实验板可能还包含其他接口,如串行通信端口(UART)、SPI、I2C、GPIO等,以及用于扩展的总线接口如PCI-E、USB、SD卡等,这些都是为了提供多样化的硬件平台,便于开发者进行各种实验和项目开发。

4. **开发环境与工具**:配合ALTERA的 Quartus II软件,用户可以进行FPGA的设计、编译、仿真和下载,同时Quartus II也提供了丰富的IP核库,方便用户快速集成常见的功能模块。

在电路原理图中,每一页通常会详细描绘一个或多个部分的电路细节,例如电源管理、时钟电路、FPGA的配置电路、各个接口的连接等。通过这些详细的设计图纸,工程师可以了解各个组件如何协同工作,以便于调试、改进或扩展设计。

ALTERA DE0实验板电路原理图是一个综合性的设计文档,它揭示了实验板的内部结构和工作原理,对于理解和使用这款开发板至关重要。无论是初学者还是经验丰富的工程师,都可以从中学习到FPGA设计的基本知识和实践经验。

270 浏览量

2024-11-05 上传

2024-11-05 上传

2024-11-05 上传

2024-10-27 上传

195 浏览量

174 浏览量

tahaa

- 粉丝: 0

- 资源: 8

最新资源

- 数据结构(c++版)

- Keil C51使用详解

- 3D论文-A Generic Framework for Efficient 2-D and 3-D Facial Expression Analogy

- 楼房销售论文.doc

- WebLogic Web Development

- The C Programming Language

- 一个RMI的分布式应用的实例

- 很好看的一个js的小日历

- Turbo C 屏幕函数

- ArcGIS9.3新特性

- CHD372中文资料

- C语言100例(精髓)

- 附录B Phase1-Phase2-Phase2+之间的差异

- ext中文手册(ext教程)

- 常用功能的测试方法-告诉你如何测试界面、功能、安装测试等

- 跟我一起写Makefile