全差分运放电路设计:高精度与高速特性

需积分: 47 170 浏览量

更新于2024-07-25

收藏 394KB PDF 举报

全差分运放电路是一种特殊的运算放大器电路结构,它主要用于提高信号处理的精度和抗共模干扰能力。在本文中,作者王彦和嵇楚详细探讨了全差分运放电路的设计原则以及几个关键步骤。

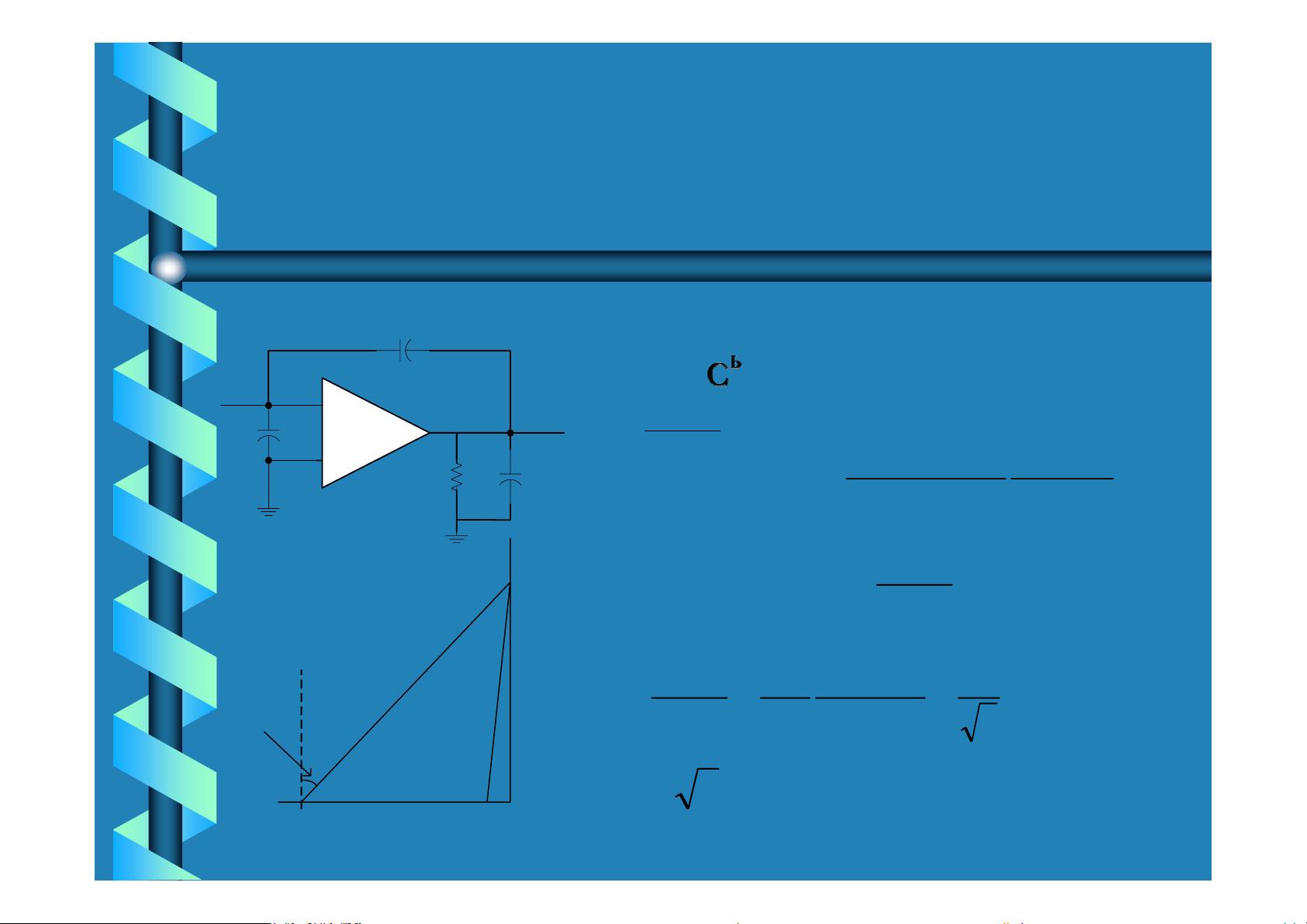

首先,设计要求是设计的核心,文中强调了几个重要的性能指标:直流增益(DC Gain)必须大于80dB,带宽增益(Gain-Bandwidth Product,GBW)要求大于50MHz,负载能力(Loading)为5pF,相位裕量(Phase Margin)大于60度,增益裕量(Gain Margin)大于12dB,斜率(Slew Rate)达到200V/us,共模电压范围(Commonmode Voltage)设定在2.5V(考虑到电源电压5V),共模反馈带宽(GBW of CMFB)要求超过10MHz。此外,还规定了输入噪声(Equivalent Input Noise)小于20nV/√Hz,输入失调电压(Input Offset Voltage)小于10mV,以及输出摆幅(Output Swing)要求每个通道至少2V,频率响应在±1Hz内。

电路结构的选择对于实现这些性能至关重要,设计者利用Slew Rate(200V/us)来决定电流路径中的电阻(R)和电容(C)。输入级的Slew Rate通过电容补偿方法确定,如选取2pF的电容值,而输出级的Slew Rate则相应地选择1pF,确保整个电路的性能。

参数计算部分着重于根据电路特性进行精确计算,包括电流的确定,以及如何通过调整电阻和电容来满足Slew Rate的要求。例如,通过计算得出电流I与Slew Rate的关系,同时考虑反馈网络(fb)、电感(L)和总电容(Ltotal)的影响,确保输出级的上升和下降时间(rise time 和 fall time)。

全差分运放电路设计的关键在于精细的参数匹配和优化,以满足高性能指标的同时保持良好的共模抑制比。通过严谨的计算和电路结构选择,可以实现高质量的信号处理,广泛应用于信号调理、测量和通信系统中。

点击了解资源详情

点击了解资源详情

218 浏览量

全差分运放电路源文件:增益140dB、带宽超1GHz等高指标电路设计详解,含模块功能解析及实验报告,全差分运放电路模块详解:增益达140dB,带宽超1G,含共源共栅结构等高级电路设计学习资料,全差分运

2025-02-17 上传

全差分运放电路模块详解:增益达140dB,高速响应,低噪声及高精度调整等特性电路设计源代码与理论分析,全差分运放电路电路源文件,包含模块有:折叠共源共栅结构运放,开关电容共模反馈,连续时间共模反馈电路

2025-01-19 上传

117 浏览量

807 浏览量

367 浏览量

1638 浏览量

lainiqiu

- 粉丝: 0

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程