Intel Quartus Prime Timing Analyzer详解:高级定时与基本操作

需积分: 10 138 浏览量

更新于2024-07-16

收藏 1.29MB PDF 举报

本文档主要介绍了如何使用Intel Quartus Prime Pro Edition进行FPGA时序分析,特别是针对ALTERA器件的高级功能。它深入探讨了基本的静态定时分析原理,并提供了详细的步骤指南来操作 Timing Analyzer 工具。

1. **基本概念与原理**

- **Timing Path and Clock Analysis**: 时序路径分析是确定设计中各逻辑单元之间信号传输延迟的关键环节,包括数据路径和控制路径的延迟。通过理解和优化这些路径,可以确保设计满足时钟周期的要求。

- **Clock Setup/Hold Analysis**: 分别关注时钟输入信号到达寄存器前的setup时间(数据必须在时钟上升沿之前进入)和保持时间(数据必须在时钟下降沿后继续存在),以防止数据丢失或错误。

- **Recovery and Removal Analysis**: 用于检查信号是否在时钟周期内有足够的时间进行恢复(信号在时钟周期结束后恢复到稳定状态)或去除(移除毛刺或噪声)。

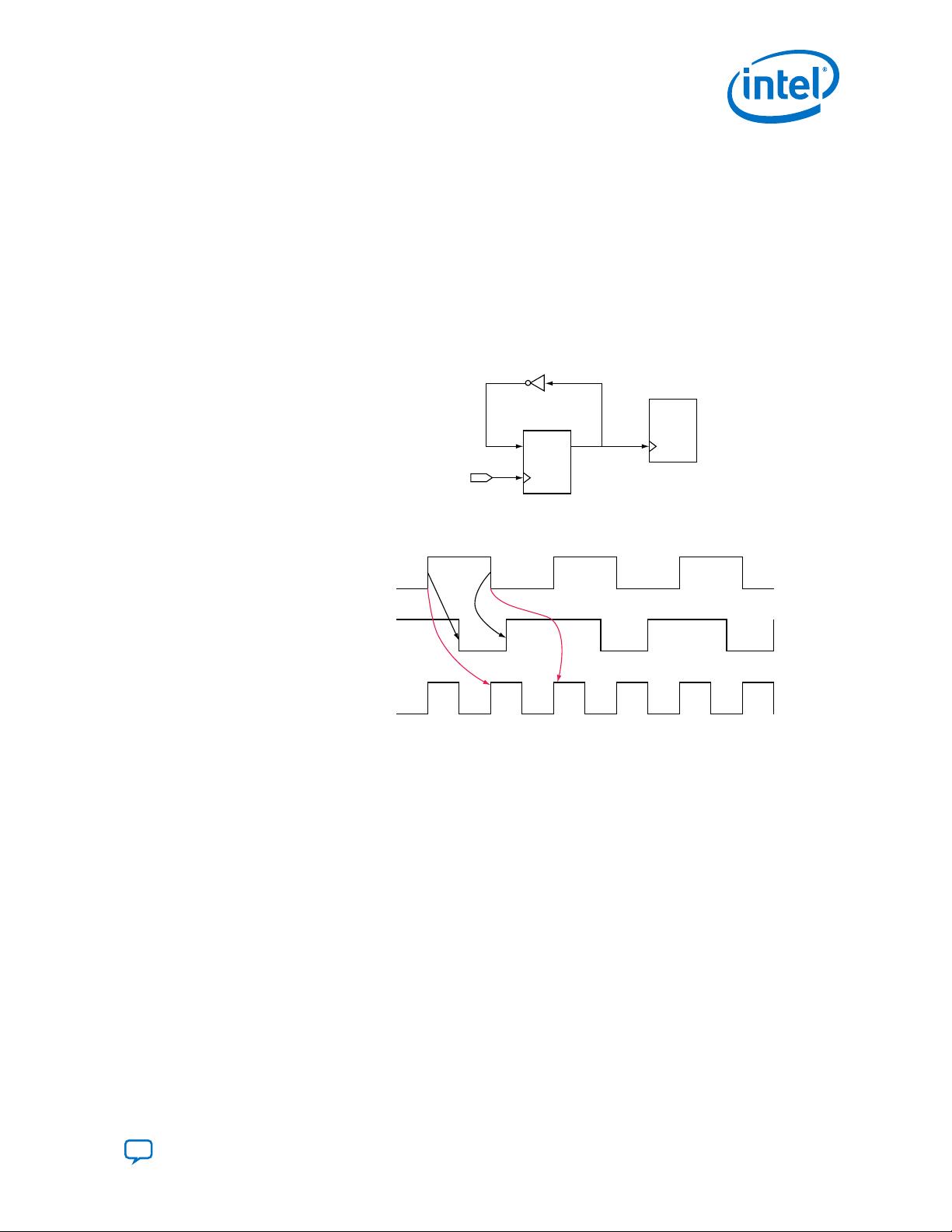

- **Multicycle Path Analysis**: 考虑到某些情况下信号可能需要经过多个时钟周期的延迟,此分析识别出允许多时钟周期延迟的路径。

- **Metastability Analysis**: 评估设计对于可能的 metastability(竞争冒险)现象的敏感性,确保信号在寄存器间传递时不会出现不稳定状态。

- **Timing Pessimism**: 描述设计中的保守估计,即为了安全考虑而假设的最坏情况下的延迟,这可能导致实际性能低于预期。

- **Clock-As-Data Analysis**: 时钟信号也可能作为数据流的一部分,此分析会检查时钟本身是否存在潜在问题,如抖动或失锁。

2. **使用 Intel Quartus Prime Timing Analyzer**

- **Enhanced Timing Analysis for Intel Arria®10 Devices**: 对于特定的Arria系列FPGA,该工具提供增强特性,可能包括专用算法或优化设置,以更好地适应这些器件的特性。

- **Basic Timing Analysis Flow**:

- **Step 1**: 打开项目并运行Fitter,这是初始化分析的前提,Fitter会生成设计的网表信息。

- **Step 2**: 配置 Timing Constraints,这是设定设计性能目标和限制的重要步骤,包括setup、hold、clock period等。

- **Step 3**: 设置一般 Timing Analyzer 参数,如分析模式、阈值和报告级别等,以适应特定的需求。

- **Step 4**: 运行 Timing Analysis,软件将根据设定进行模拟,计算延迟和分析结果。

- **Step 5**: 仔细解读分析结果,找出潜在问题并优化设计,可能涉及修改逻辑结构、调整布线策略或添加缓冲区等。

3. **使用Timing Constraints**

- **Recommended Initial SDC Constraints**: 文档提供了推荐的约束模板,帮助用户快速上手,但可能需要根据具体设计进行调整。

- **SDC File Precedence**: SDC(Synopsys Design Constraints)文件的优先级管理,理解何时何种类型的约束文件起作用,确保一致性。

- **其他注意事项**: 如何正确地应用约束以避免冲突和提高分析效率,可能包括设置合理的目标时间和处理全局时序约束。

本文档详细阐述了在Intel Quartus Prime Pro Edition中进行FPGA时序分析的基本步骤和关键概念,对于熟悉并优化FPGA设计性能具有重要参考价值。通过遵循文档中的指导,用户能够有效地利用 Timing Analyzer 来评估和改进其设计的时序行为。

2019-05-19 上传

2021-03-18 上传

2019-05-31 上传

2024-09-29 上传

2023-10-21 上传

2019-07-09 上传

2020-06-05 上传

liujie19862008

- 粉丝: 0

- 资源: 4

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍