FPGA时序分析指南:从基础到进阶

需积分: 10 36 浏览量

更新于2024-07-23

收藏 9.44MB PDF 举报

"这份文档详细介绍了FPGA的时序分析,包括TimeQuest静态时序分析模型、模型的角色、网表概念、时序报告、时序分析中的关键概念如余量、延迟因数以及 PLL 约束等。此外,还讨论了网表质量、外部模型对时序的影响,以及物理时钟的相关知识。通过一系列实验,读者可以深入理解并掌握时序分析的关键技巧。"

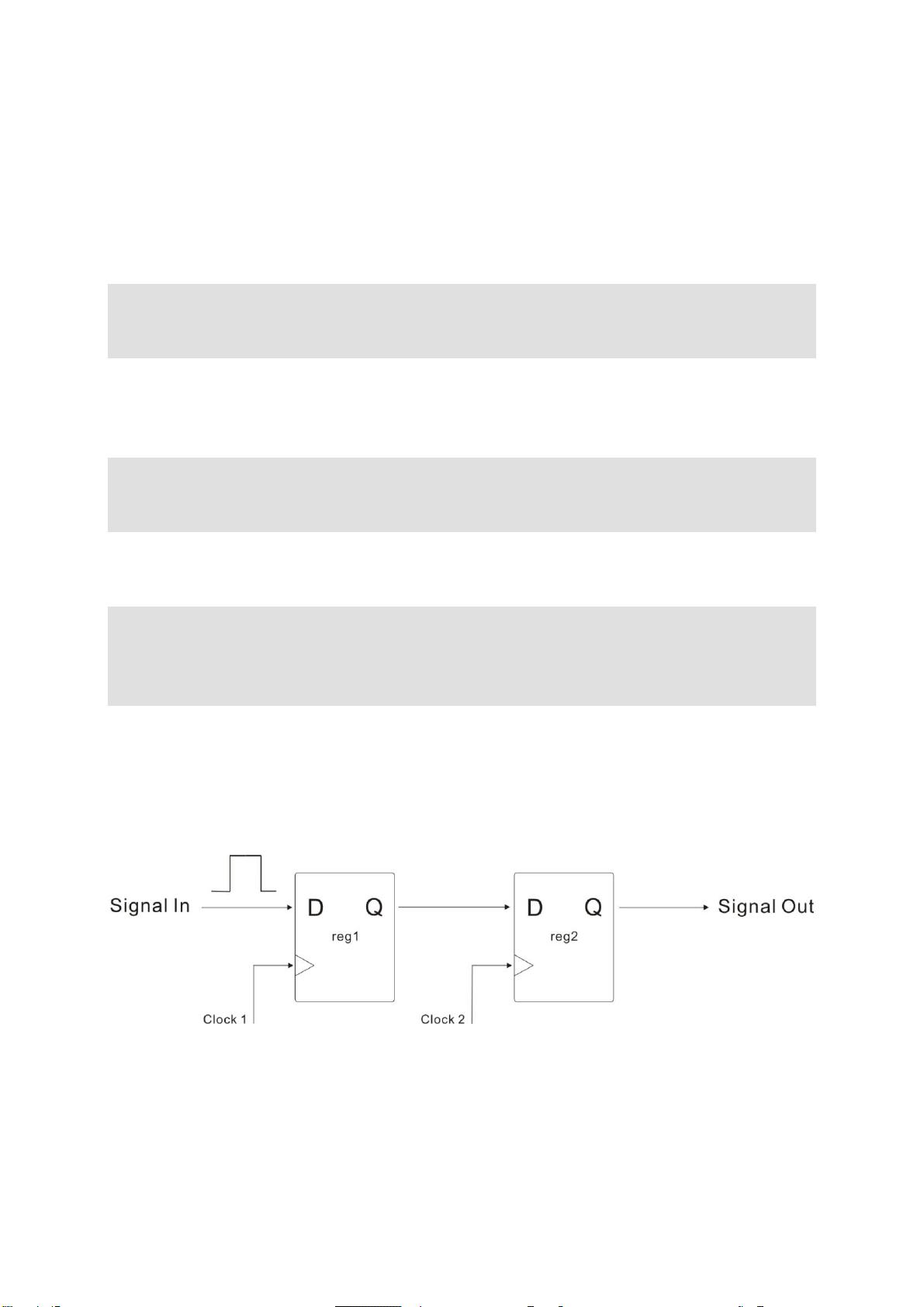

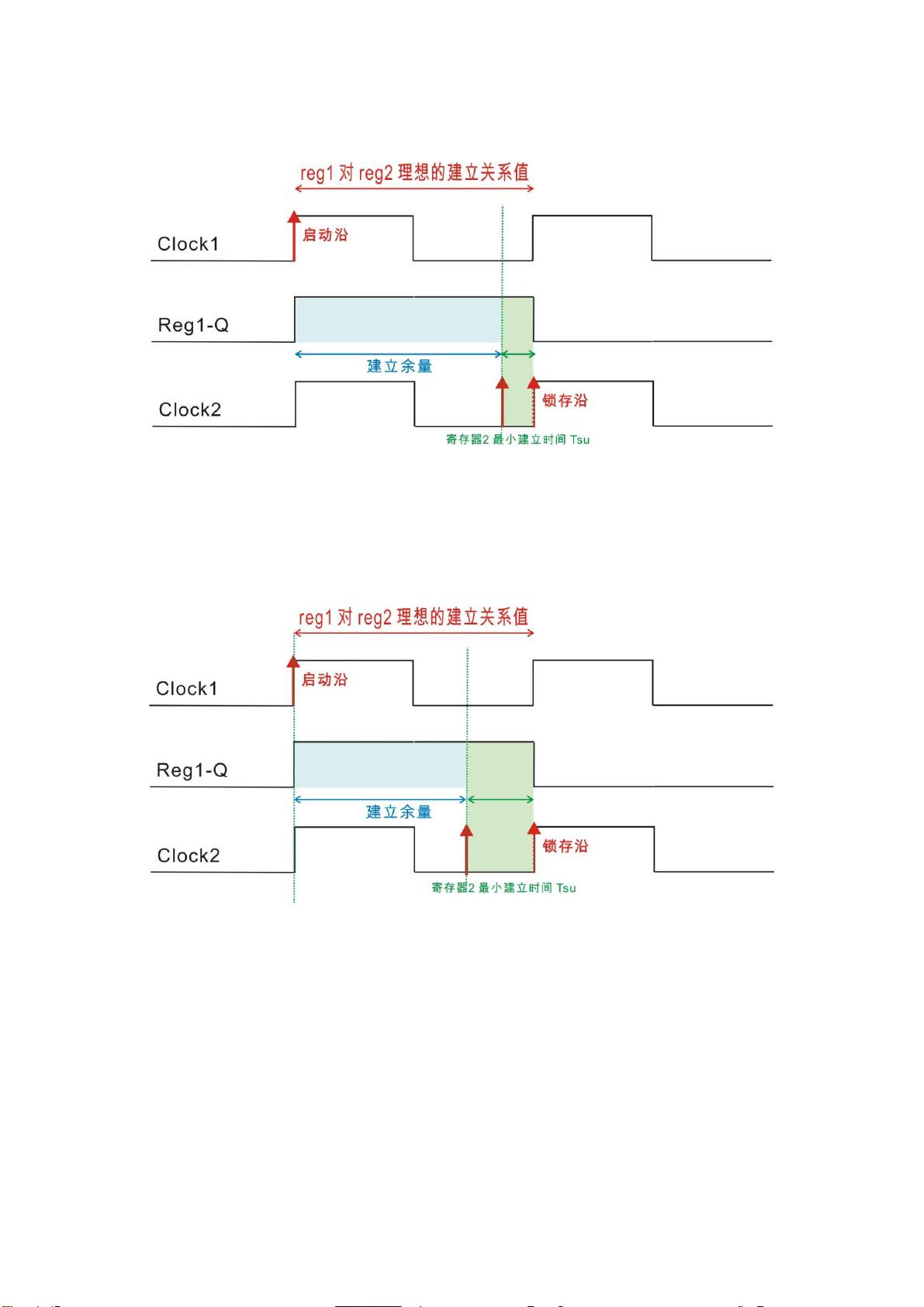

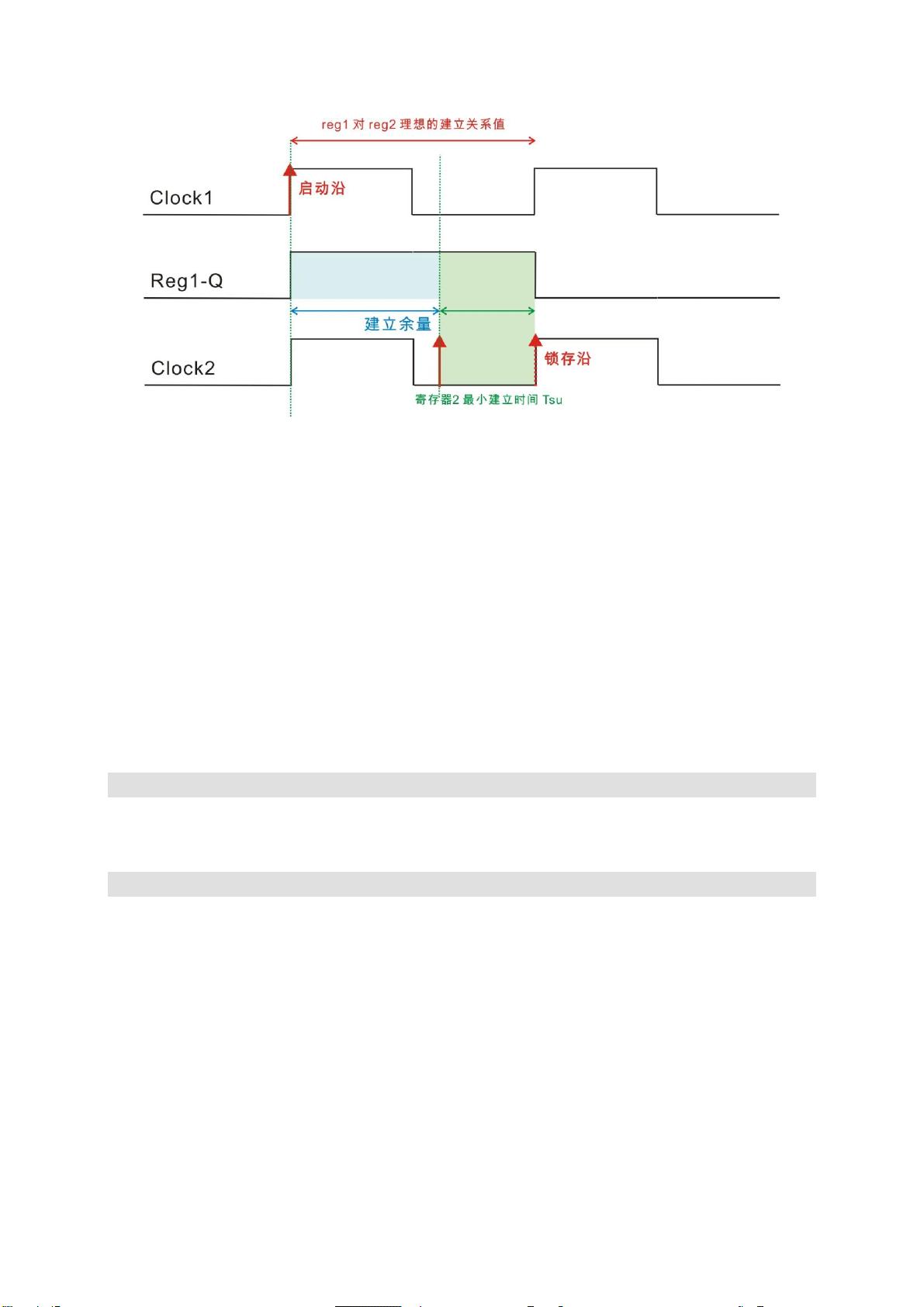

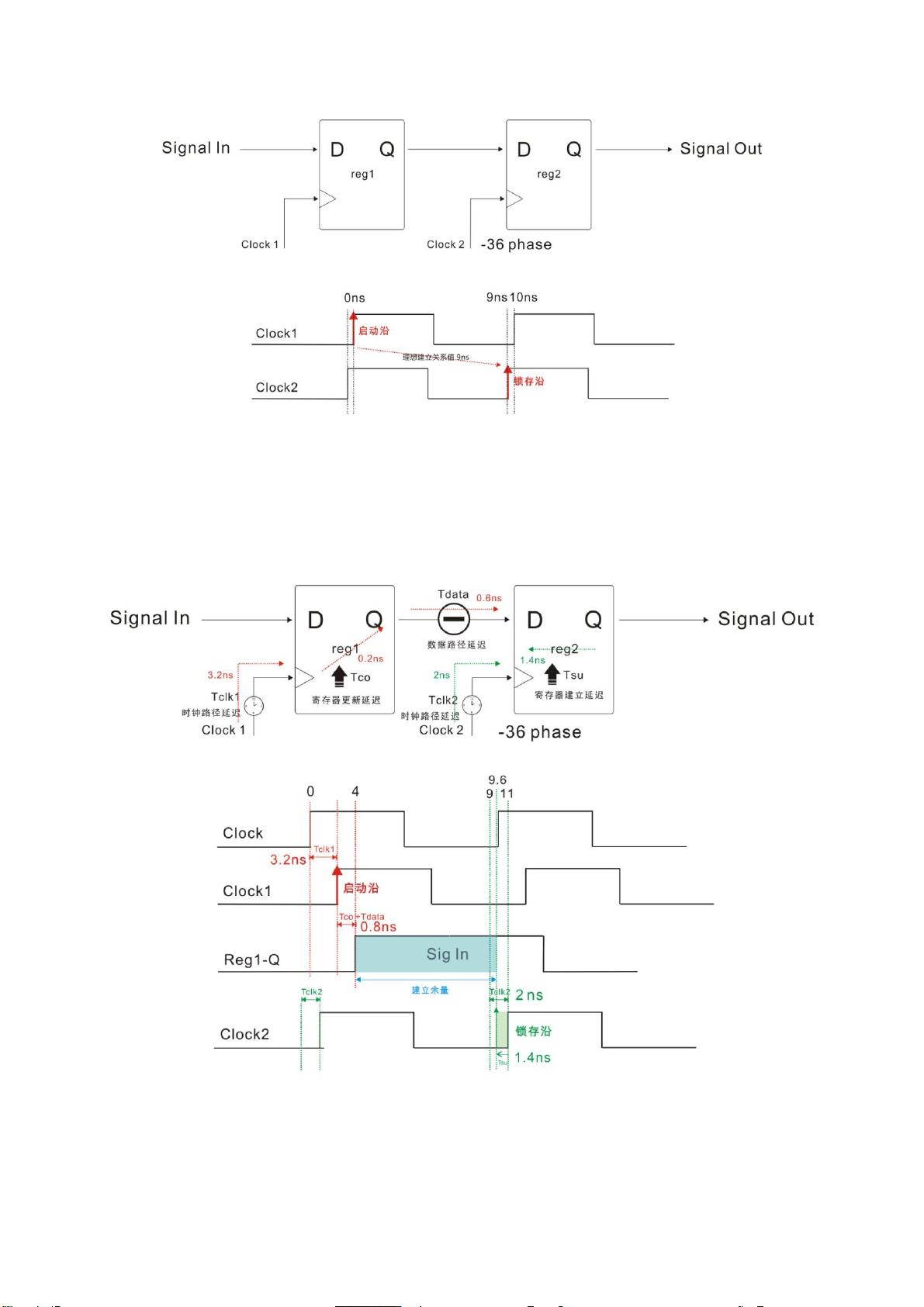

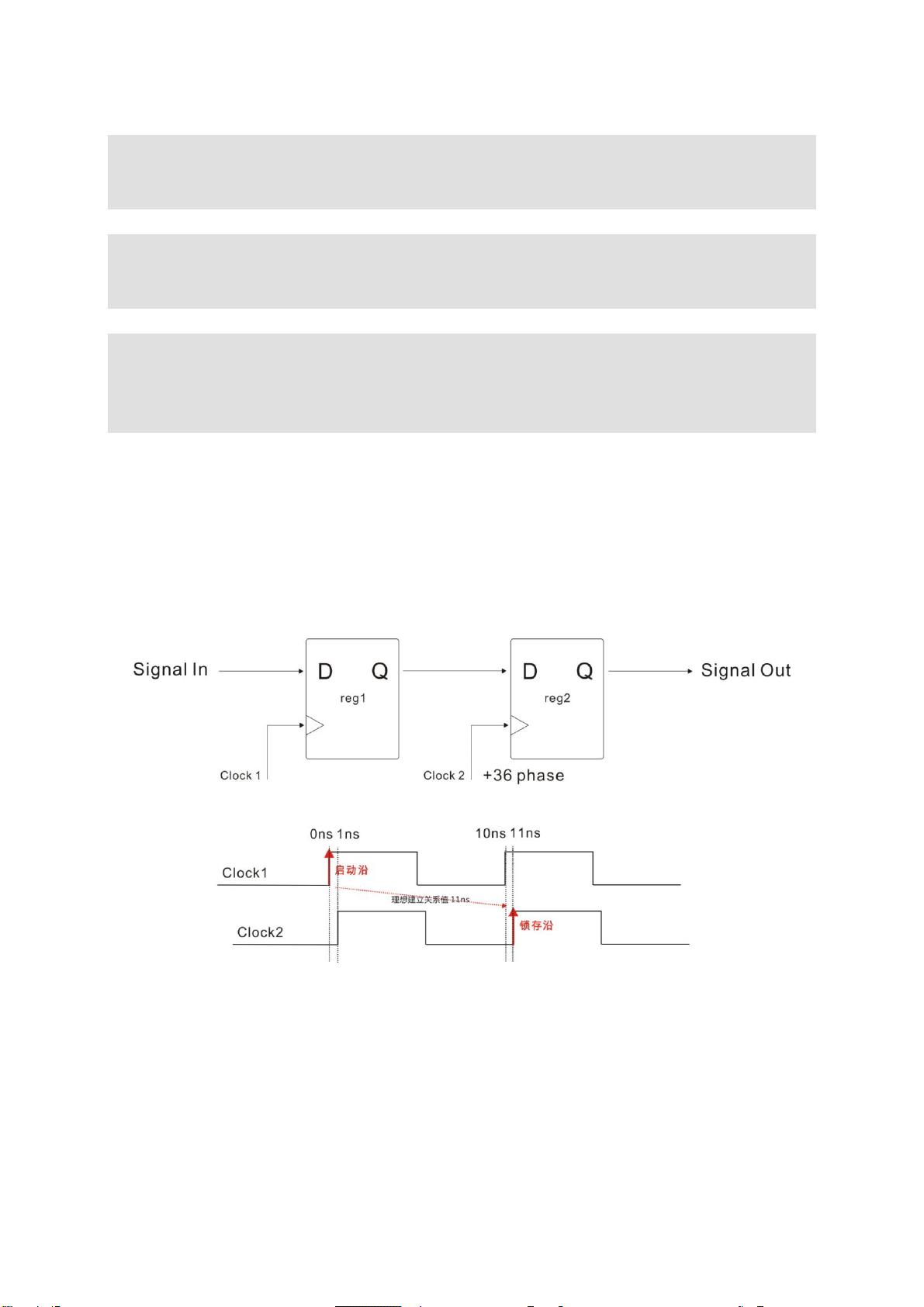

在FPGA设计中,时序分析是确保系统正确运行的核心部分。TimeQuest是一款常用的静态时序分析工具,它帮助设计师验证设计是否满足时序要求,即逻辑门之间的信号传输能否在规定的时间内完成。文档首先介绍了TimeQuest的时序分析模型,模型的基础单位是时钟周期,理想的建立关系值和保持关系值是分析的起点。在实际应用中,由于物理因素,会有建立时间和保持时间的需求,这些需求需要在设计中留出余量,以防止信号失真或错误。

第二章详细讲述了TimeQuest模型的运用,包括SDC(Synopsys Design Constraints)文件和网表的作用。通过实验,读者可以学习如何创建SDC文件来约束时钟,以及如何解读时序报告,这些对于理解和优化设计至关重要。

第三章深入解释了余量的概念,分为内部和外部延迟因数,并讨论了第一层和第二层时间要求。此外,还介绍了一些TimeQuest的特殊模型和约束命令的行为。

第四章涉及PLL(Phase-Locked Loop)与时钟约束,PLL常用于生成多个同步时钟,通过正确的约束,可以确保PLL产生的时钟满足设计的时序要求。实验部分则通过延迟怪兽的案例,演示了如何处理复杂的延迟问题。

第五章关注网表质量和外部模型,网表质量直接影响分析的准确性,Fmax评估值是衡量设计性能的一个重要指标。外部模型的输入/输出约束则可以帮助更准确地模拟接口行为。

最后一章探讨了物理时钟,包括时钟的延迟和抖动,以及如何使用set_clock_latency命令告知TimeQuest外部时钟的延迟信息。

这份文档提供了一个全面的学习路径,帮助FPGA设计师深入理解并熟练掌握时序分析的关键技术和实践操作。通过理论与实验的结合,读者可以逐步提升时序分析能力,从而优化设计性能,确保FPGA设计的成功实现。

2012-03-27 上传

2013-08-26 上传

2023-09-11 上传

2016-11-11 上传

2009-04-11 上传

2021-07-07 上传

点击了解资源详情

点击了解资源详情

vimer郑

- 粉丝: 6

- 资源: 7

最新资源

- gulishop_backend:一个基于vue和element-ul的二次开发项目

- capstone_cunysps

- google-homepage

- M1905播放器易语言源码-易语言

- DbfExporter-开源

- INFO6105_repo:数据科学工程存储库

- KCcoroutine:协程

- react-frec:这是一个类型库,用于编写简单的“ React.forwardRef”和“ React.ForwardRefExoticComponent”

- 0601、单电源运放图解资料手册.rar

- 删除重复文本-易语言

- alpine-droplet:用于数字海洋的Alpine Linux图像生成器

- landify:这是我在2020年11月进行的第一个项目

- 0548、单片机原理与应用实验指导书.rar

- movie_api

- DiskMonitor:适用于macOS的Apple DiskArbitration框架的简单包装程序包

- 位图结构易语言演示源码-易语言