Verilog HDL入门教程:数字系统设计与CPU组成解析

需积分: 3 84 浏览量

更新于2024-07-31

收藏 1.9MB PPT 举报

"这篇文档是关于Verilog HDL的学习指南,着重讲解了硬件描述语言的基础语法、句式以及在设计复杂数字系统中的应用,特别是针对初学者提供了丰富的实例验证,帮助理解Verilog HDL在复杂指令集CPU设计中的应用。"

在深入探讨Verilog HDL之前,我们首先了解一些计算机体系结构的基本概念。复杂指令集计算机(CISC)和精简指令集计算机(RISC)是两种主要的指令系统架构。CISC具有复杂的指令集,指令码长度不固定,执行一条指令可能需要多个时钟周期。而RISC则相反,它简化了指令集,指令码长度通常固定,每条指令在一个时钟周期内完成,从而提高了效率。

指令码格式通常包括操作码和地址码。操作码指示处理器执行何种操作,其位数取决于指令系统的规模。地址码则用于定位操作数,可以有零到多个。寻址方式包括寄存器寻址、立即寻址、直接寻址、间接寻址、变址寻址、基址寻址和基址+变址寻址等,这些方式各有优缺点,适用于不同场景。

接着,文档通过Intel 8086和MC16C54的指令系统实例,展示了数据传送、算术运算、逻辑运算、程序控制、输入输出、堆栈操作和字符串操作等多种指令类型。这些指令是CPU执行任务的基础,它们共同构成了CPU的指令集。

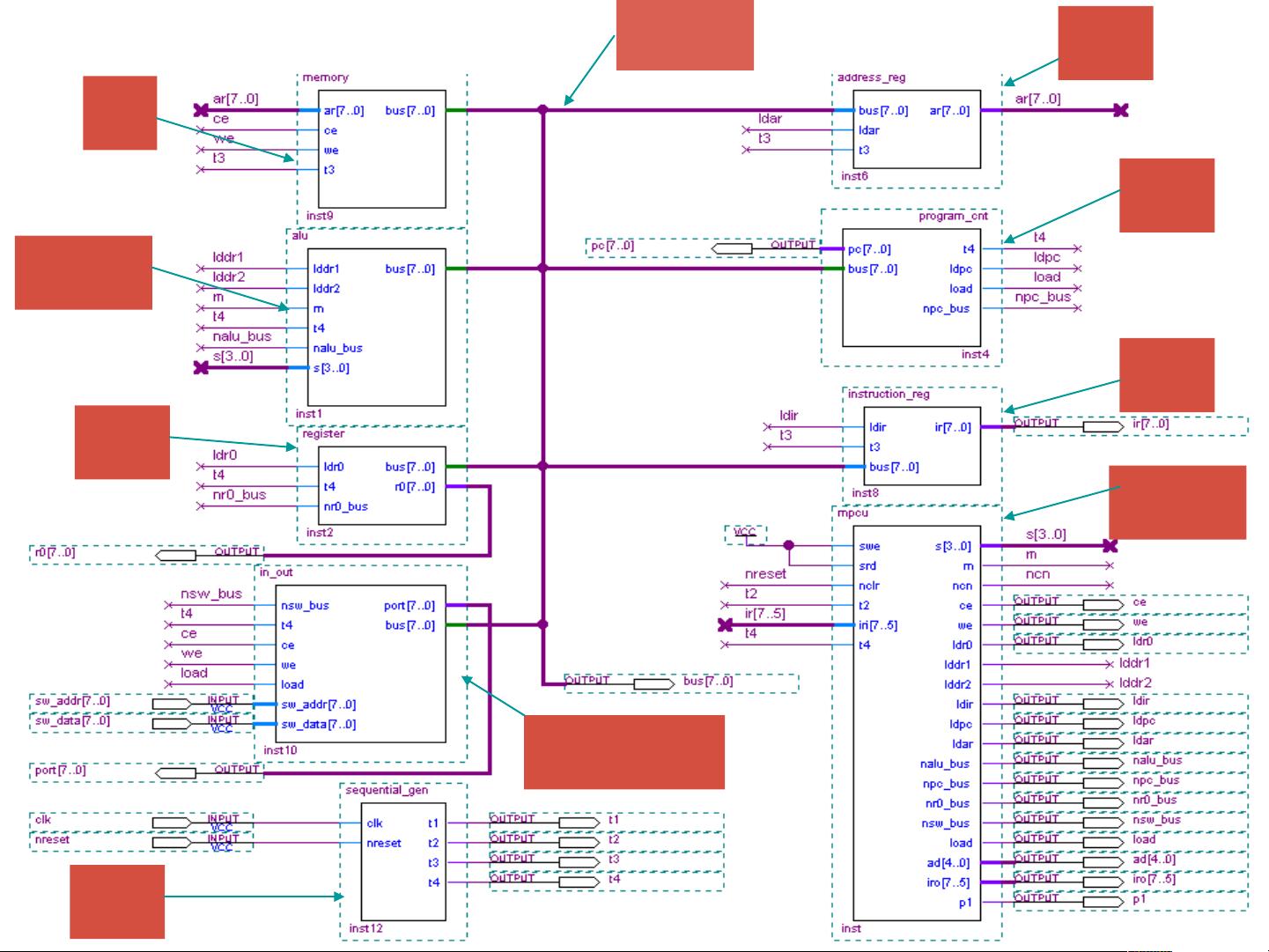

CPU是计算机的核心,由控制器和运算器组成。控制器包含程序计数器(PC)、指令寄存器(IR)、指令译码器(ID)、时序脉冲发生器和操作控制器,负责取指令、解码、控制执行流程。运算器主要包括算术逻辑单元(ALU)、累加器(AC)、数据缓冲寄存器和状态条件寄存器(如标志寄存器),执行算术和逻辑运算,并处理数据。

Verilog HDL是一种硬件描述语言,用于设计和验证数字系统,包括CPU等复杂系统。通过使用Verilog,设计师可以描述硬件行为和结构,模拟和综合电路,实现硬件的数字化建模。对于初学者来说,了解这些基础知识并结合实例进行学习,有助于更好地掌握Verilog HDL的语法和用法,进而能够设计出自己的数字系统。

2021-11-27 上传

2022-06-28 上传

2014-10-25 上传

2022-09-20 上传

2007-10-20 上传

2008-12-02 上传

2022-09-20 上传

2022-09-21 上传

chenxiaobo1224

- 粉丝: 0

- 资源: 3

最新资源

- nostalgebraist-autoresponder:tumblr bot nostalgebraist-autoresponder的代码

- Multi depth pointer based Triangle List:非常快速且可动态扩展的数据结构。-开源

- Android参考源码-调用Android中的软键盘.zip

- ynapshot-CPETT,c语言测试源码是否正确,c语言

- baseballmatching2

- grunt-boilerplate:Grunt、LESS 和 include-replace 满足您所有的 webapp 开发需求

- ibc2k1.github.io

- xryuseix.github.io

- Android应用源码之悬浮窗 监视内容.zip项目安卓应用源码下载

- zbzh,c语言二十一点游戏源码简单,c语言程序

- Vier Hack-crx插件

- BowlingScoreCalculator

- Kinematics-Web-Calculator

- OFDM 频谱:带 GI 的 OFDM 频谱。-matlab开发

- ChatApplication

- No roses-crx插件