Altera FPGA中复位电路详解:同步与异步策略与时间分析

需积分: 10 51 浏览量

更新于2024-07-23

收藏 494KB DOC 举报

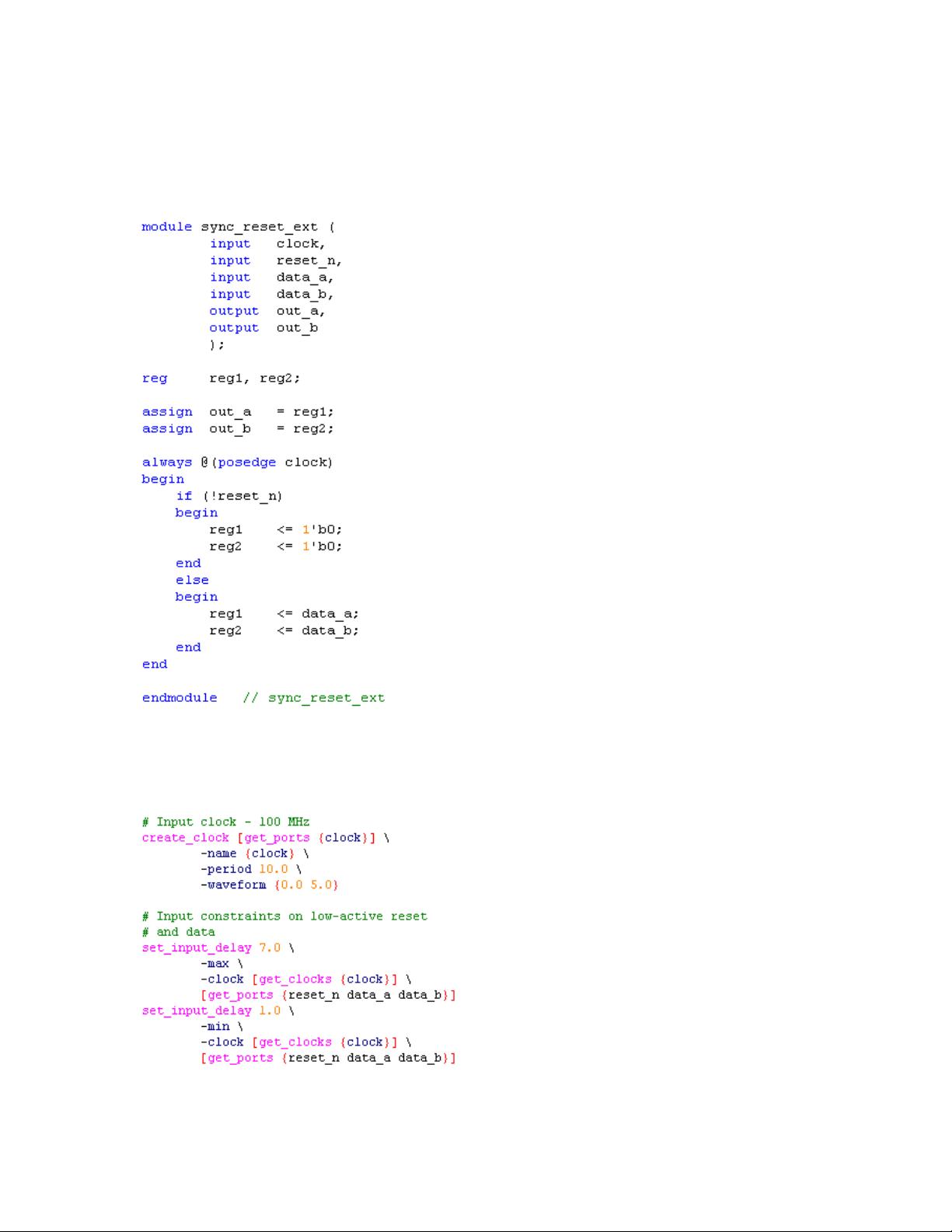

在Altera FPGA的设计实践中,复位电路(Reset Circuits)起着至关重要的作用,因为大多数基于FPGA和ASIC的系统都是时序同步的,包含大量的触发器或寄存器,需要确保这些元素能准确地初始化到预定义的状态(通常为逻辑'1'或'0')。本文档深入探讨了复位电路的不同类型,包括同步复位、异步复位以及同步与异步相结合的复位方式。

首先,同步复位(Synchronous Reset)是与系统时钟频率同步的,这意味着它会与被复位的寄存器或触发器的时钟周期同步发生。这种类型的复位通常更为精确,因为它避免了因不同信号延迟可能导致的不确定性。然而,同步复位的一个关键挑战是,如果时钟网络受到扰动,可能会引发潜在的复位冲突或延迟,这可能影响系统的稳定性。

相比之下,异步复位(Asynchronous Reset)则不受系统时钟控制,它直接作用于目标寄存器,无需等待特定时钟周期。这样可以更快地将设备置于预设状态,但它的缺点是复位时间可能会受到电源波动、噪声等因素的影响,不那么一致。异步复位通常用于需要快速响应的紧急情况或对复位时间有严格要求的应用。

同步异步复位(Synchronized Asynchronous Reset)是一种结合了两者优点的解决方案,它在系统启动时采用异步模式快速复位,然后切换到同步模式以确保所有寄存器都按照预期的时序进行操作。这种方式允许在系统稳定后利用同步复位的优势,同时保持对初始快速响应的需求。

在实际的FPGA设计中,实现这些复位电路可能涉及专用的复位单元、外部接口或复杂的触发器结构。Altera的TimeQuest定时分析工具对于评估复位电路的时序特性至关重要,设计师需要考虑复位信号的传输路径、延时以及与其他信号的交互,以确保满足FPGA的时序要求。

总结来说,复位电路设计是FPGA系统设计的关键环节,正确选择和优化复位策略,包括同步、异步和同步异步,能显著影响系统的性能和可靠性。理解这些复位类型的特点、实施方法以及在TimeQuest中的分析方法,有助于创建高效且稳健的FPGA设计。

2015-01-06 上传

2015-06-17 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

lkiller_hust

- 粉丝: 61

- 资源: 1

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程