Synopsys IC Compiler详解:物理设计与布局布线基础

需积分: 49 87 浏览量

更新于2024-07-15

6

收藏 2.43MB PDF 举报

本文档深入介绍了集成电路(IC)的布局布线基础,对于初学者来说是一份宝贵的学习资料。物理设计是IC设计的关键步骤,涉及将电路逻辑转化为能够应用于晶圆制造的版图,主要包括数据准备、布局、时钟树综合、布线和验证等环节。Synopsys的IC Compiler和Astro,以及Candance的SOC-Enconter是常用的设计工具,如IC Compiler能处理门级网表、库文件和时序约束,输出布局数据(GDSII格式)。

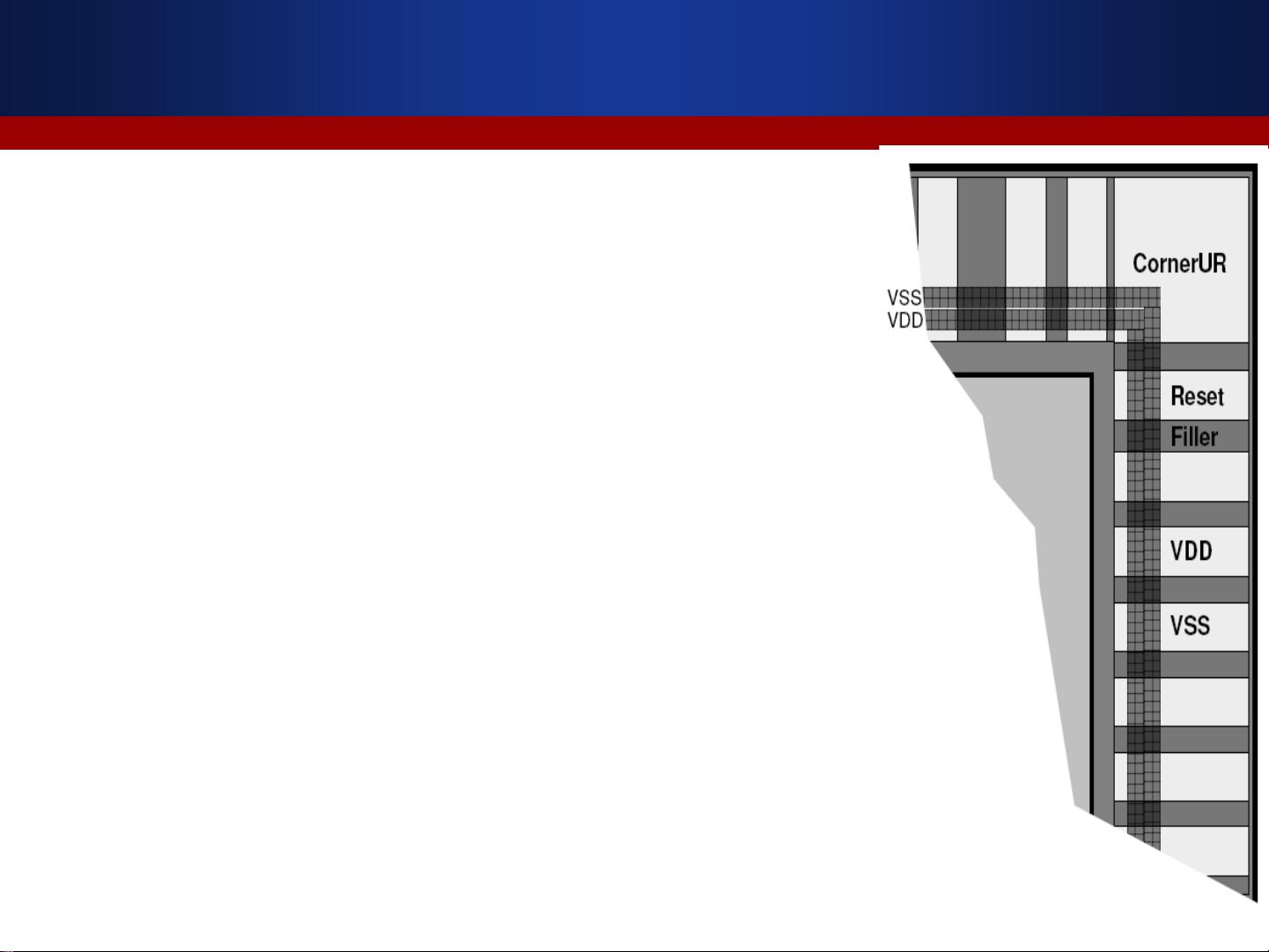

在进行物理设计之前,必须建立参考库,这包括standcell library(标准单元库,包含基本逻辑门如反相器、缓冲器、逻辑门等)、pad library(信号和电源地垫片库)以及macrocell(宏单元库,包含复杂功能模块)。四个角落的conner单元负责连接芯片边缘的IO pad,确保信号的正确传输。

布图规划(floorplan)是整个过程的核心,它决定了芯片的大小、输入输出(IO)分配、宏模块布局、电源网络设计等。地板计划的决策直接影响芯片的性能,如速度、功耗和布线效率。由于其手工干预程度高,优化和调整往往消耗大量时间,因此在设计流程中反复迭代是常见的。

典型的芯片结构分为核心区域(core area)和垫片区域(pad area),后者又细分为多个子区域,如电源区、接地区、IO连接区等。有效的布图规划能够提高芯片的一次性成功(oncepass)概率,降低后期修改的成本。

这篇资料详细讲解了从物理设计的基础概念、工具选择,到关键步骤如布图规划和参考库建设的实践操作,对于理解和掌握ICC布局布线技术非常有帮助。通过学习和实践,初学者可以逐步提升在实际项目中的应用能力。

176 浏览量

578 浏览量

144 浏览量

916 浏览量

591 浏览量

309 浏览量

andywang3791

- 粉丝: 0

- 资源: 11

最新资源

- cra-ts-prettier-commitlint-template:CRA模板,具有更漂亮,更沙哑,更出色的提交以及更多现成的设置

- portfolio-template:Jekyll产品组合网站模板,以使用GitHub Pages展示您的工作

- 供应链管理中的库存控制

- jsonviewerpackage.zip

- johnroids:Johnroids是在go,gopherjs和gowasm中实现的旧式小行星游戏

- localSolver:本地求解器的文件。 云托管代码不需要这些

- 供应链管理 供应链管理思想产生

- XCTAssertCrash:使用Mach异常处理程序或POSIX信号处理程序断言表达式崩溃

- kutik

- 47元手把手教你:图像识别的垃圾分类系统.rar

- gp_project:使用遗传编程找到多项式函数

- qrcode_scanner::hammer_and_wrench:Flutter QR码扫描仪插件

- 美赛各题型常见参考代码汇总.zip

- 供应链下的后勤管理

- 7Bot-Arduino-lib:这是7Bot的Arduino库

- 5.9【阿里云天池】零基础入门数据价格:二手车交易价格预测 car-price-forecast-master.zip