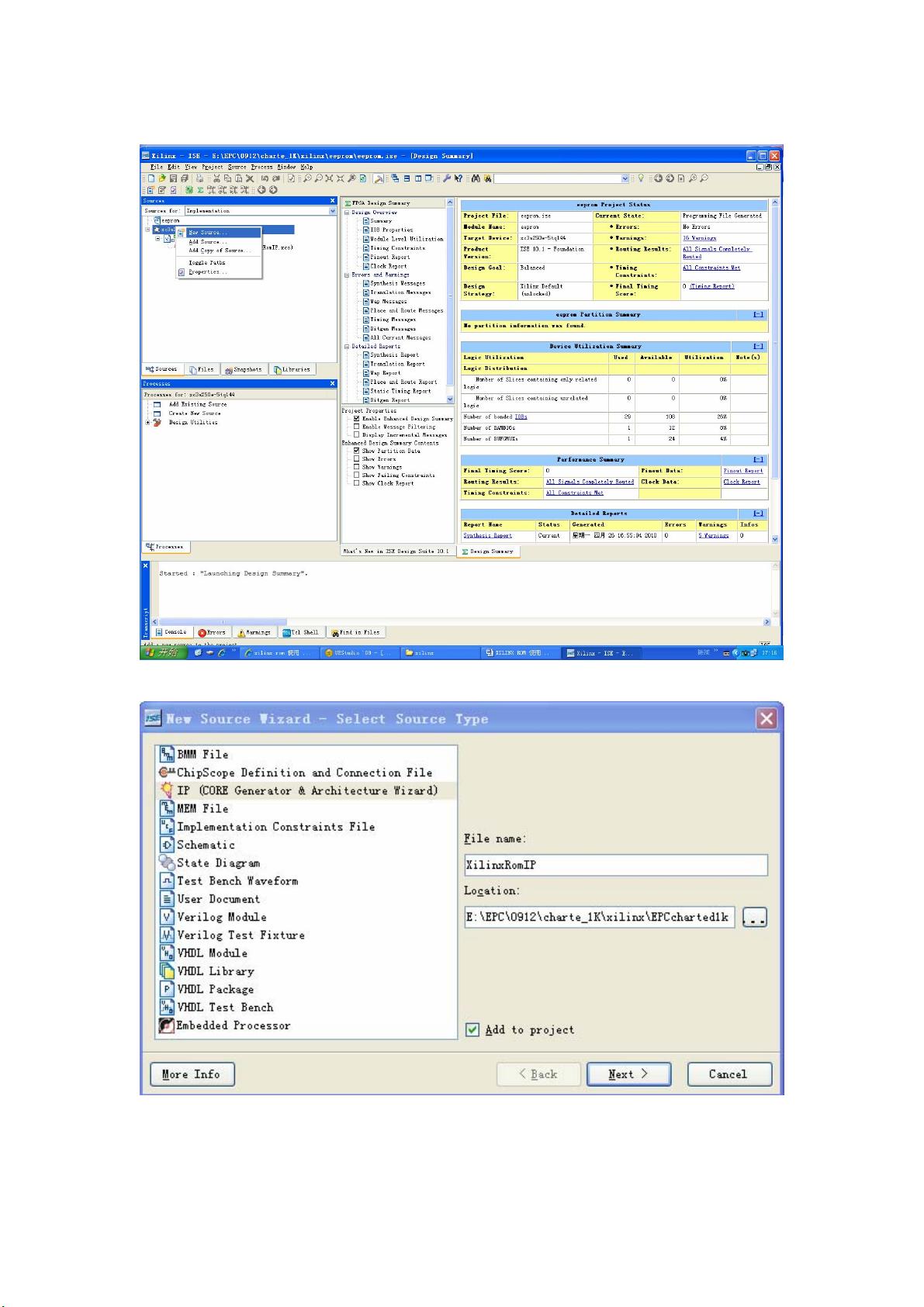

Xilinx ISE中详细ROM IP核创建与应用教程

本文档详细介绍了如何在Xilinx ISE环境下使用ROM IP核进行FPGA设计。首先,你需要打开Xilinx ISE工具,通过NEWSOURCE功能添加新的IP。选择合适的ROM IP核是关键步骤,主要有三种选项:BlockMemory、分布式Memory和单口或双口BLOCKRAM。对于内存需求较小且逻辑资源有限的情况,分布式ROM是一个节省BLOCKRAM的选择,但需注意它会占用额外的逻辑资源。

在生成设置向导中,用户需要指定Memory类型,如位宽和深度,这直接影响到ROM的容量。用户需要准备一个.COE文件,用于存放要存储在ROM中的数据。COE文件的内容应按照特定格式编写,包括定义数据的进制(10、2、16),接着是数据列表,每个数据项之间用逗号分隔,最后一行以分号结尾。数据的数量必须与定义的深度相匹配,否则可能导致编译错误。

创建完.COE文件后,将其导入到IP项目中,如果无误,可以通过查看显示确认数据正确。接着,点击Finish生成IP核,此时会自动生成一个.MIF文件,这是二进制形式的ROM数据,以及如ROM_COS.XCO这样的VHDL代码。用户可以选择.V或.VHD文件,双击VIEWHDLFUNCTIONALMODEL查看Verilog代码。

最后,将生成的HDL文件和其他相关文件一起进行综合,例如Eeprom.coe和Eeprom.v,以完成整个ROM IP核的集成。通过这些步骤,开发者能够有效地利用Xilinx的ROM IP核进行FPGA设计,确保代码的正确性和高效性。在整个过程中,理解并遵循每一步的细节至关重要,以避免潜在的设计问题。

2023-09-11 上传

2023-06-12 上传

2023-06-11 上传

2023-08-27 上传

2024-06-30 上传

2023-09-08 上传

qulecheng

- 粉丝: 1

- 资源: 2

最新资源

- Ansys Comsol实现力磁耦合仿真及其在电磁无损检测中的应用

- 西门子数控系统调试与配置实战案例教程

- ELM多输出拟合预测模型:简易Matlab实现指南

- 一维光子晶体的Comsol能带拓扑分析研究

- Borland-5技术资料压缩包分享

- Borland 6 技术资料分享包

- UE5压缩包处理技巧与D文件介绍

- 机器学习笔记:深入探讨中心极限定理

- ProE使用技巧及文件管理方法分享

- 增量式百度图片爬虫程序修复版发布

- Emlog屏蔽用户IP黑名单插件:自定义跳转与评论限制

- 安装Prometheus 2.2.1所需镜像及配置指南

- WinRARChan主题包:个性化你的压缩软件

- Neo4j关系数据映射转换测试样例集

- 安装heapster-grafana-amd64-v5-0-4所需镜像介绍

- DVB-C语言深度解析TS流