VHDL实现八位数码管动态扫描电路设计解析

"数码管扫描显示电路设计是利用VHDL语言在FPGA平台上实现的一种显示技术,旨在理解和掌握数码管动态扫描显示的原理以及如何使用EDA工具和VHDL设计复杂的时序逻辑电路。实验涉及到七段显示数码管的工作原理、静态与动态显示方式的比较,以及动态扫描显示的实现方法。"

数码管扫描显示电路的核心在于利用时钟信号进行分时复用,以减少所需的I/O资源和功耗。在VHDL设计中,时钟信号扮演着关键角色,它控制着数码管的轮流点亮。八位数码管扫描电路意味着可以同时显示8位数字或字符。

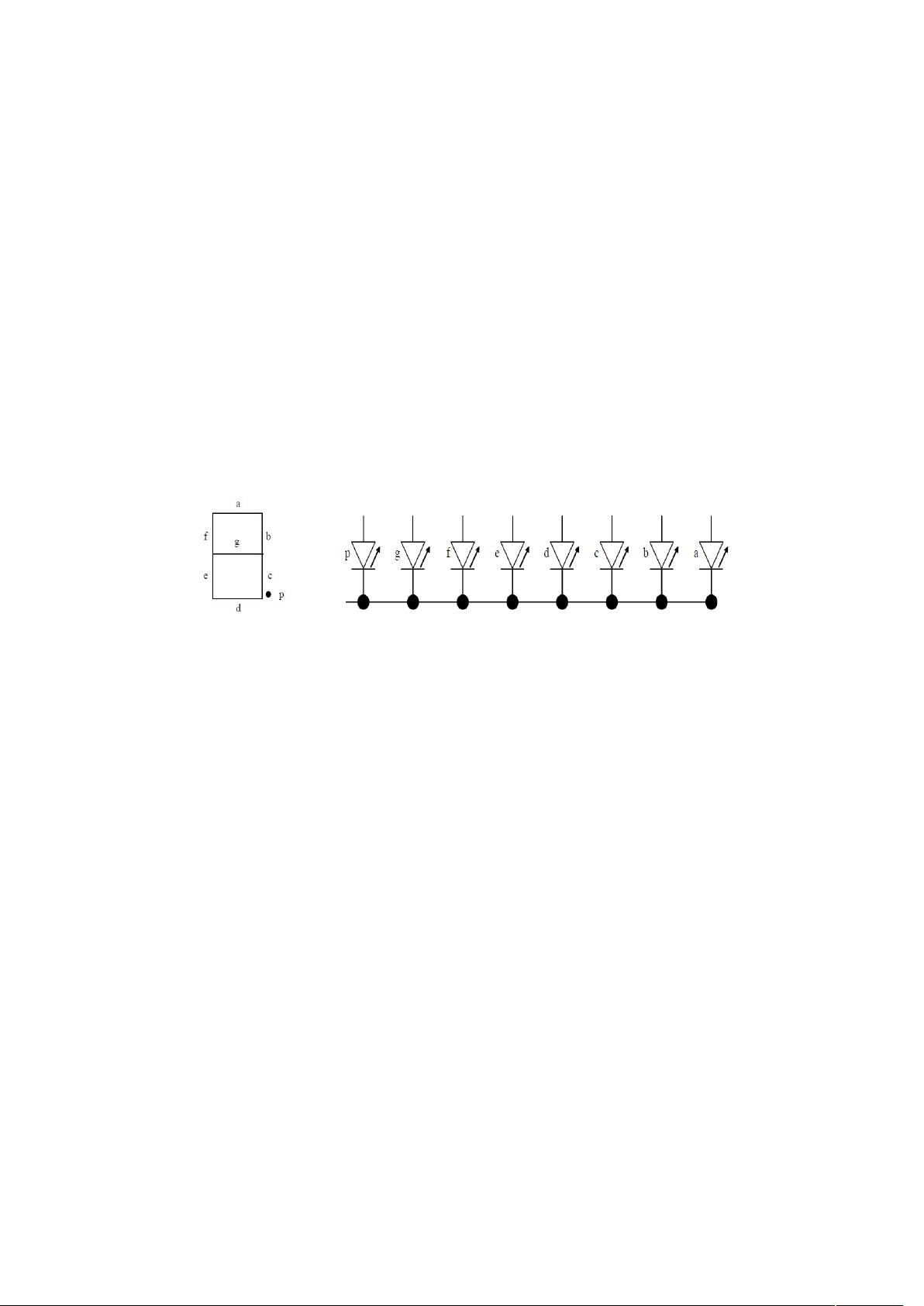

七段数码管分为共阳极和共阴极两种类型,它们由八个LED组成,对应数码管的七段a到g(如果有小数点,还会有一个额外的段)。对于共阴极数码管,LED的阴极连接在一起,阳极分别连接到电源,而共阳极数码管则相反。计算串联电阻的目的是确保LED在合适的电流下工作,以达到理想的亮度和寿命。

静态显示方式适用于少量数码管的场景,每个数码管都有独立的译码器和I/O口,优点是控制简单,但随着数码管数量增加,会消耗大量I/O资源且功耗较大。

相比之下,动态显示方式采用扫描技术,所有数码管共享相同的字形码,通过快速切换COM端口(共阴极数码管的公共端)来依次点亮数码管。虽然每个数码管的实际点亮时间很短,但人的视觉暂留现象使得看起来像是所有数码管同时稳定显示。动态显示节省了I/O口,降低了功耗,但控制逻辑相对复杂。

图6.2展示了8个数码管的动态扫描显示接口电路,COM0到COM7端口的波形如图6.3所示,这些波形控制着数码管的亮灭状态。理解这些波形和它们如何与VHDL代码中的时序逻辑配合至关重要。

在VHDL编程中,需要定义一个计数器来控制扫描序列,同时需要译码逻辑来决定哪个数码管应该显示。通过合理设计时钟分频和计数器,可以实现快速的扫描速度,以消除人眼看到的闪烁效果。

这个实验旨在通过设计和实现数码管扫描电路,深入理解数字系统中的时序逻辑设计,以及如何利用VHDL语言优化硬件资源的利用,提升系统的效率。

135 浏览量

点击了解资源详情

点击了解资源详情

130 浏览量

250 浏览量

532 浏览量

750 浏览量

2022-10-13 上传

2022-10-13 上传

qq_39792733

- 粉丝: 1

- 资源: 4

最新资源

- 英语常用3500词音频+PDF文件(含音频).zip

- 老板计时器

- Honey Boo Boo的算法和功能分解

- ember-addon-config

- 1.8wUA库.zip

- reading-notes:在这里您可以找到我的阅读资料库,主要用于总结我在编程方面的学习历程,希望您能找到一些有用的信息<3

- 视频播放可弹出弹幕,关闭弹幕

- simple-spawner:生成一个命令并将输出通过管道返回到 std{in,out,err}

- CSS_Assignment_2

- 使用注释将JDBC结果集映射到对象

- curious-blindas-api:CuriousCat克隆

- PRO-C21-BULLETS-AND-WALLS

- ff35mm:Flickr 的全画幅 (35mm) 焦距

- C#解析HL7消息的库

- 将Java System.out定向到文件和控制台的快速简便方法

- 库索逻辑-葡萄牙语