FPGA高速IO:HSTL与LVDS详解及应用

FPGA高速IO技术是现代集成电路设计中的关键组成部分,它主要关注在数据传输速度、信号完整性以及电源管理方面的优化。本文将重点介绍两种常见的高速IO标准:HSTL(High-Speed Transmission Logic)和LVDS(Low-Voltage Differential Signaling)。

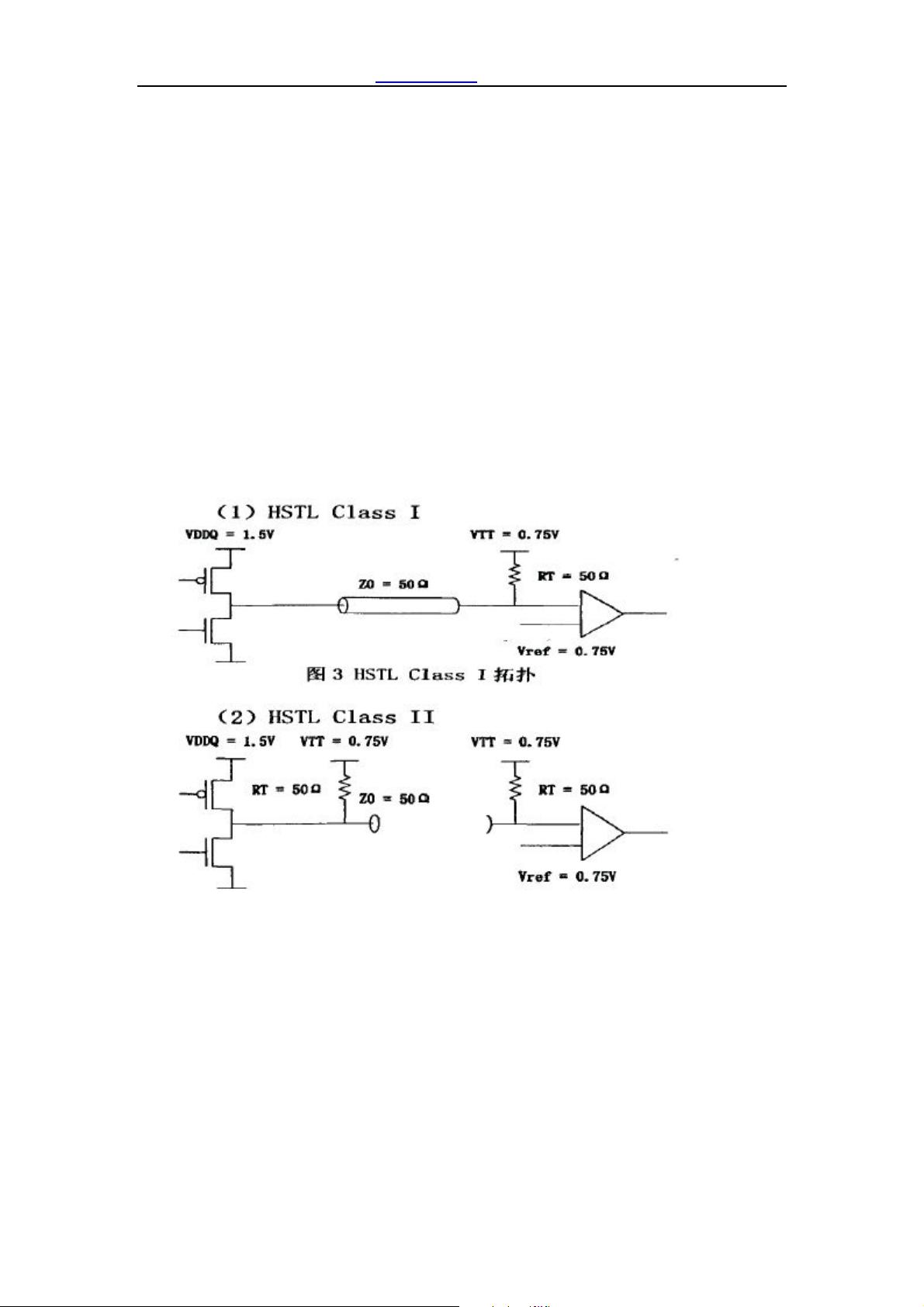

HSTL标准,由IBM发起并被JEDEC(联合电子设备工程委员会)采纳为EIA/JESD8-6电路逻辑标准,它的目标是实现1.5V的高速数据传输。HSTL标准分为四个等级(I-IV),I/II级为对称驱动器,适合低至中等速度应用,而III/IV级是非对称驱动器,适用于更高速度的接口,比如高速RAM的读写操作。HSTL技术的优势在于其技术独立性和灵活性,使得不同工艺的FPGA可以适应不同的高速接口需求。

LVDS高速I/O则采用了电流模式的差分信号传输,通过驱动器和接收器的配合来增强信号质量。驱动器部分由一个恒定电流源(典型值3.5mA)驱动一对差分信号线,这种设计能够提供更好的噪声抑制能力和驱动能力。接收器具有高直流阻抗,大部分驱动电流会在终端电阻上产生约350mV的压降,形成清晰的逻辑状态。LVDS的标准包括ANSI/TIA/EIA和IEEE 1596.3两个版本,后者定义了详细的电气参数,如上升时间和下降时间,确保了信号的准确传输。

LVDS的特点是低电压、差分信号处理,这降低了功耗,提高了信号的抗干扰能力。它的设计允许在长线路上保持稳定的信号质量,对于FPGA的高速外设连接至关重要。无论是HSTL还是LVDS,它们都是为了满足FPGA在数据传输速率不断提升的现代应用中的性能要求,如数据中心通信、高速网络和高性能计算等领域。

FPGA高速IO技术的发展和标准化是推动芯片性能进步的关键因素,理解并掌握这些技术对于FPGA设计者来说至关重要,它们直接影响着系统的可靠性和效率。通过使用合适的高速IO标准,FPGA能够在各种高速接口环境中稳定工作,实现数据的高效传输。

2023-09-13 上传

2023-05-05 上传

2023-05-25 上传

2024-07-03 上传

2024-10-27 上传

2024-10-27 上传

ydcqu2007

- 粉丝: 0

- 资源: 14

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍