PCB分层堆叠设计在控制EMI辐射中的关键策略

41 浏览量

更新于2024-09-01

收藏 237KB PDF 举报

"通过PCB分层堆叠设计控制EMI辐射"

在电子设备设计中,电磁干扰(EMI)的控制是一项至关重要的任务,因为它可能导致系统性能下降、功能异常甚至完全失效。本文主要探讨了如何通过PCB(印制电路板)的分层堆叠设计来有效抑制EMI辐射,从而提高硬件设计的稳定性与可靠性。

首先,解决EMI问题的方法多种多样,包括使用EMI抑制涂层、选择合适的EMI抑制组件以及进行EMI仿真设计。然而,本文重点聚焦于从PCB基础设计层面出发,特别是PCB的分层堆叠策略在控制EMI辐射方面的作用。

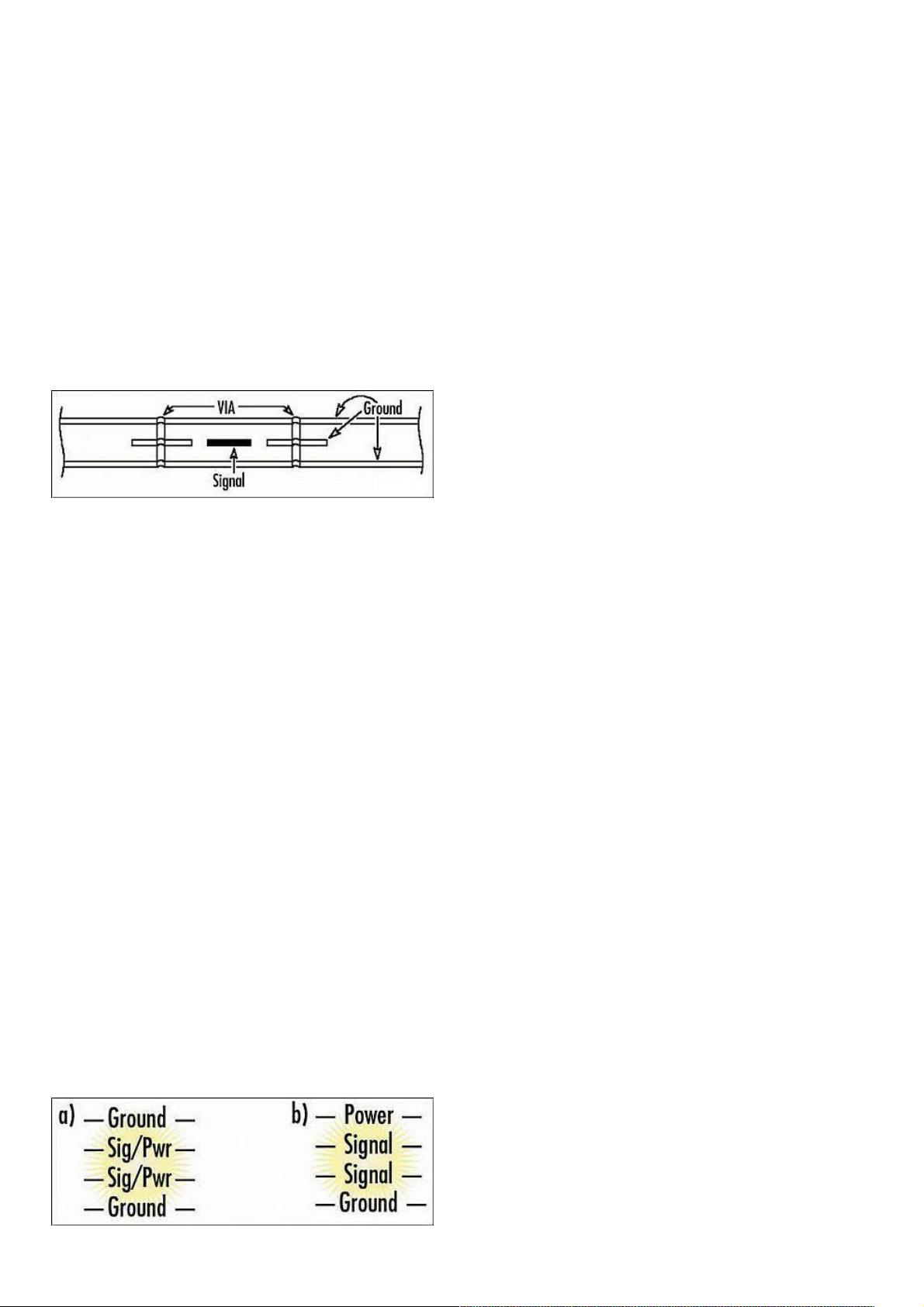

电源汇流排是EMI产生的一个关键环节。当IC(集成电路)电源引脚附近的电容不足以提供快速响应时,电源汇流排上的瞬态电压会在去耦路径的电感两端产生电压降,形成共模EMI干扰源。为了解决这一问题,我们需要优化电源层的设计。电源层应被视为高频电容器,能够收集并提供IC所需的高频能量。同时,电源层的电感要尽可能低,以减少由信号上升沿快速变化引起的瞬态信号,从而降低共模EMI。

为了有效地去耦和控制共模EMI,电源层应与IC电源引脚紧密连接,连线长度应尽可能短,以减少信号传输过程中的损失。此外,电源层的分层设计和材料选择也至关重要。例如,层间距越小,等效电容越大,对高频信号的响应能力越强。对于快速上升时间(如100到300ps)的器件,可能需要采用小于1mil的层间距和高介电常数的材料,如陶瓷或加陶塑料,以适应更高的频率需求。

对于当前常见的1到3ns上升时间的电路,3到6mil的层间距和FR4材料通常已经足够处理高端谐波。然而,随着技术的发展,更高速度的器件将需要更先进的材料和更精细的分层技术来应对EMI挑战。

通过优化PCB的分层堆叠设计,可以显著改善EMI辐射控制,确保电子系统的电磁兼容性。设计师需要考虑电源层的电容特性、电感、层间距以及材料的选择,以适应不同器件的工作频率和上升时间,从而实现高效且低EMI的电路设计。

210 浏览量

112 浏览量

2021-05-25 上传

2021-01-19 上传

2020-07-22 上传

2021-01-20 上传

2021-01-20 上传

2021-01-19 上传

2020-08-19 上传

weixin_38653385

- 粉丝: 2

- 资源: 942

最新资源

- Ufrayd

- cstore_fdw:由Citus Data开发的用于使用Postgres进行分析的列式存储。 在https:groups.google.comforum#!forumcstore-users上查看邮件列表,或在https:slack.citusdata.com加入我们的Slack频道。

- 正则化算法

- monaco-powershell:VSCode的Monaco编辑器+ PowerShell编辑器服务!

- ASP网上购书管理系统(源代码+论文).zip

- node-provider-service

- Gradle插件可将APK发布到Google Play-Android开发

- Uecker

- 阿里云机器学习PAI-DSW入门指南.zip

- Cardboard-Viewer:主要使用Three.js,我为Google Cardboard耳机创建了一个陀螺移动VR查看器,以查看我在克利夫兰地区使用Panono 360相机拍摄的360°全景照片和风景。 刷新页面从总共6张照片中选择一张随机照片。 要查看该应用程序,请单击链接:

- Jwg3full.github.io

- 简单的C++串口示例

- 高斯白噪声matlab代码-SPA_for_LDPC:此存储库是关于LDPC(又名低密度奇偶校验)代码的和积算法在二进制对称信道,二进制擦除信

- C/C++:二叉排序树.rar(含完整注释)

- U27fog

- godotenv:Ruby的dotenv库的Go端口(从`.env`加载环境变量。)