没有合适的资源?快使用搜索试试~ 我知道了~

首页ADI SC573数据手册:SHARC+双核DSP与Cortex-A5处理器

ADI SC573数据手册:SHARC+双核DSP与Cortex-A5处理器

需积分: 5 0 下载量 77 浏览量

更新于2024-07-19

收藏 3.38MB PDF 举报

ADI SC573是一款由Analog Devices公司生产的高性能数字信号处理器(DSP),它融合了SHARC+双核架构以及一个ARM Cortex-A5内核。SHARC和SHARC+都是Analog Devices公司的注册商标,代表着该公司在高性能信号处理领域的先进技术。这款产品的主要特性包括:

1. **双核增强SHARC+核心**:每个SHARC+核心具有强大的浮点运算能力,能够达到高达450MHz的工作频率,提供了极高的计算性能。

2. **存储资源**:每颗SHARC+核心配备最多3Mb(384kB)L1静态随机存取内存(SRAM),支持奇偶校验,可作为缓存使用,具有灵活性。用户可以根据需求配置这些存储资源。

3. **多模式计算**:支持32位、40位和64位浮点运算,以及32位固定点运算,可以适应不同的应用场景,提供广泛的精度选项。

4. **地址线兼容性**:设计有字节、短字、字和长字等多种地址寻址方式,增加了对不同数据结构的兼容性。

5. **ARM Cortex-A5集成**:与Cortex-A5内核相结合,使得SC573成为一个功能丰富的系统级芯片,能够处理控制任务和实时应用,增强了系统的整体效能。

6. **文档反馈**:Analog Devices对其提供的信息持信心,但不承担因使用该产品可能引发的专利侵权或其他第三方权利问题的责任,并且规格可能会随时更新,未经明确许可,不涉及任何专利授权。

7. **联系方式与版权信息**:ADI公司的联系信息、技术支持网站和版权声明,提醒用户尊重知识产权并寻求官方支持。

ADI SC573是一款专为高性能信号处理和混合信号应用设计的双核处理器,其卓越的性能、灵活的存储配置和多模式计算能力使其在工业控制、通信、音频处理等领域具有广泛的应用潜力。用户在使用时应确保遵循相关规范,并参考最新的技术文档以获取最新信息。

Rev. 0 | Page 16 of 142 | June 2017

The S/PDIF interface supports one stereo channel or com-

pressed audio streams. The S/PDIF transmitter and receiver are

AES3 compliant and support the sample rate from 24 KHz to

192 KHz. The S/PDIF receiver supports professional jitter

standards.

The S/PDIF receiver/transmitter has no separate DMA chan-

nels. It receives audio data in serial format and converts it into a

biphase encoded signal. The serial data input to the receiver/

transmitter can be formatted as left justified, I

2

S, or right justi-

fied with word widths of 16, 18, 20, or 24 bits. The serial data,

clock, and frame sync inputs to the S/PDIF receiver/transmitter

are routed through the signal routing unit (SRU). They can

come from various sources, such as the SPORTs, external pins,

and the precision clock generators (PCGs), and are controlled

by the SRU control registers.

Precision Clock Generators (PCG)

The precision clock generators (PCG) consist of two units

located in the DAI block. The PCG can generate a pair of signals

(clock and frame sync) derived from a clock input signal

(CLKIN, SCLK0, or DAI pin buffer). Both units are identical in

functionality and operate independently of each other. The two

signals generated by each unit are normally used as a serial bit

clock/frame sync pair.

Enhanced Parallel Peripheral Interface (EPPI)

The processors provide an enhanced parallel peripheral inter-

face (EPPI) that supports data widths up to 16 bits for the BGA

package and 12 bits for the LQFP package. The EPPI supports

direct connection to thin film transistor (TFT) LCD panels, par-

allel ADCs and DACs, video encoders and decoders, image

sensor modules, and other general-purpose peripherals.

The features supported in the EPPI module include the

following:

• Programmable data length of 8 bits, 10 bits, 12 bits, 14 bits,

and 16 bits per clock.

• Various framed, nonframed, and general-purpose operat-

ing modes. Frame syncs can be generated internally or ca

n

be supplied by an external device.

• ITU-656 status word error detection and correction for

ITU-656 receive modes and ITU-656 preamble and status

word decoding.

• Optional packing and unpacking of data to/from 32 bits

fr

om/to 8 bits and 16 bits. If

packing/unpacking is enabled,

configure endianness to change the order of pack-

ing/unpacking of bytes or words.

• RGB888 can be converted to RGB666 or RGB565 for trans-

mit modes.

• Various deinterleaving/interleaving modes for receiv

ing or

transmitting 4:2:2 YCrCb data.

• Configurable LCD data enable output available on Frame

Sync 3.

Universal Asynchronous Receiver/Transmitter

(UART) Ports

The processors provide three full-duplex universal asynchro-

nous receiver/transmitter (UART) ports, fully compatible with

PC standard UARTs. Each UART port provides a simplified

UART interface to other peripherals or hosts, supporting full-

duplex, DMA supported, asynchronous transfers of serial data.

A UART port includes support for five to eight data bits as well

as no parity, even parity, or odd parity.

Optionally, an additional address bit can be transferred to inter-

rupt only addressed nodes in multidrop bus (MDB) systems. A

frame is terminated by a configurable number of stop bits.

The UART ports support automatic hardware flow control

through the clear to send (CTS) input and request to send (RTS)

output with programmable assertion first in, first out (FIFO)

levels.

To help support the Local Interconnect Network (LIN) proto-

cols, a special command causes the transmitter to queue a break

command of programmable bit length into the transmit buffer.

Similarly, the number of stop bits can be extended by a pro-

grammable interframe space.

Serial Peripheral Interface (SPI) Ports

The processors have three industry-standard SPI-compatible

ports that allow the processors to communicate with multiple

SPI-compatible devices.

The baseline SPI peripheral is a synchronous, 4-wire interface

consisting of two data pins, one device select pin, and a gated

clock pin. The two data pins allow full-duplex operation to

other SPI-compatible devices. An extra two (optional) data pins

are provided to support quad-SPI operation. Enhanced modes

of operation, such as flow control, fast mode, and dual-I/O

mode (DIOM), are also supported. DMA mode allows for trans-

ferring several words with minimal central processing unit

(CPU) interaction.

With a range of configurable options, the SPI ports provide a

glueless hardware interface with other SPI-compatible devices

in master mode, slave mode, and multimaster environments.

The SPI peripheral includes programmable baud rates, clock

phase, and clock polarity. The peripheral can operate in a multi-

master environment by interfacing with several other devices,

acting as either a master device or a slave device. In a multimas-

ter environment, the SPI peripheral uses open-drain outputs to

avoid data bus contention. The flow control features enable slow

slave devices to interface with fast master devices by providing

an SPI ready pin (SPI_RDY) which flexibly controls the

transfers.

The baud rate and clock phase and polarities of the SPI port are

programmable. The port has integrated DMA channels for both

transmit and receive data streams.

Link Port (LP)

Two 8-bit wide link ports (LPs) for the BGA package (one link

port for the LQFP package) can connect to the link ports of

other DSPs or peripherals. Link ports are bidirectional and have

eight data lines, an acknowledge line, and a clock line.

ADSP-SC572/SC573/ADSP-21573

Rev. 0 | Page 17 of 142 | June 2017

ADC Control Module (ACM) Interface

The ADC control module (ACM) provides an interface that

synchronizes the controls between the processors and an ADC.

The analog-to-digital conversions are initiated by the proces-

sors, based on external or internal events.

The ACM allows for flexible scheduling of sampling instants

and provides precise sampling signals to the ADC.

The ACM synchronizes the ADC conversion process, generat-

ing the ADC controls, the ADC conversion start signal, and

other signals. The actual data acquisition from the ADC is done

by an internal DAI routing of the ACM with the SPORT0 block.

The processors interface directly to many ADCs without any

glue logic required.

Ethernet Media Access Controller (EMAC)

The processor features an ethernet media access controller

(EMAC): 10/100/1000 AVB Ethernet with precision time proto-

col (IEEE 1588).

The processors can directly connect to a network through

embedded fast EMAC that supports 10-BaseT (10 Mb/sec),

100-BaseT (100 Mb/sec) and 1000-BaseT (1 Gb/sec) operations.

Some standard features of the EMAC are as follows:

• Support and

MII/RMII/RGMII protocols for external

PHYs. RGMII is supported only for the BGA package

• Full-duplex and half-duplex modes

• Media access management (in half-duplex operation)

•Flow control

• Station management, including the generation

of

MDC/MDIO fr

ames for read/write access to PHY registers

Some advanced features of the EMAC include the following:

• Automatic checksum computation

of IP header and IP

payload fields of receive frames

• Independent 32-bit descriptor driven receive and transmit

DMA channels

• Frame status delivery to memory through DMA, incl

uding

frame completion semaphores for efficient buffer queue

management in software

• Transmit DMA support for separate descriptors for MAC

header and payload fields to eliminate buffer copy

operations

• Convenient frame alignment modes

• 47 MAC management statistics counters with selectab

le

clear on read behavior and programmable interrupts on

half maximum value

• Advanced power management

• Magic packet detection and wakeup frame filtering

• Support for 802.3Q tagged VLAN frames

• Programmable MDC clock rate and preamble suppression

Audio Video Bridging (AVB) Support

(10/100/1000 EMAC Only)

The 10/100/1000 EMAC supports the following audio video

bridging (AVB) features:

• Separate channels or queues for AV data transfer in

100 Mbps and 1000 Mbps modes)

• IEEE 802.1-Qav specified credit-based shaper (CBS) algo-

rithm for the additional transmit channels

• Configuring up to two additional channels (Channel 1 an

d

Channel 2) on the transmit and receive paths for AV traffic.

Channel 0 is available by default and carries the legacy best

effort Ethernet traffic on the transmit side.

• Separate DMA, transmit and receive FIFO for AVB latency

class

• Programmable control to route received VLAN tagged non

AV packets to channels or queues

Precision Time Protocol (PTP) IEEE 1588 Support

The IEEE 1588 standard is a precision clock synchronization

protocol for networked measurement and control systems. The

processors include hardware support for IEEE 1588 with an

integrated precision time protocol synchronization engine

(PTP_TSYNC).

This engine provides hardware assisted time stamping to

improve the accuracy of clock synchronization between PTP

nodes. The main features of the engine include the following:

• Support for both IEEE 1588-2002 and IEEE 1588-2008 pro-

tocol standards

• Hardware assisted time stamping capable of up to 12.5 n

s

resolution

•Lock adjustment

• Automatic detection of IPv4 and IPv6 pa

ckets, as well as

PTP messages

• Multiple input clock sources (SCLK0, RGMII, RMII, MII

clock, and external clock)

• Programmable pulse per second (PPS) output

• Auxiliary snapshot to time stamp external events

Controller Area Network (CAN)

There are two controller area network (CAN) modules. A CAN

controller implements the CAN 2.0B (active) protocol. This

protocol is an asynchronous communications protocol used in

both industrial and automotive control systems. The CAN pro-

tocol is well suited for control applications due to the capability

to communicate reliably over a network. This is because the

protocol incorporates CRC checking, message error tracking,

and fault node confinement.

The CAN controller offers the following features:

• 32 mailboxes (8 receive only, 8 transmit only, 16 configu-

rable for receive or transmit)

• Dedicated acceptance masks for each mailbox

• Additional data filtering on the first two bytes

ADSP-SC572/SC573/ADSP-21573

Rev. 0 | Page 18 of 142 | June 2017

• Support for both the standard (11-bit) and extended

(29-bit) identifier (ID) message formats

• Support for remote frames

• Active or passive network support

• Interrupts, including transmit and receive complete

, error,

and global

An additional crystal is not required to supply the CAN clock

because it is derived from a system clock through a programma-

ble divider.

Timers

The processors include several timers that are described in the

following sections.

General-Purpose (GP) Timers (TIMER)

There is one general-purpose (GP) timer unit, providing eight

GP programmable timers. Each timer has an external pin that

can be configured either as PWM or timer output, as an input to

clock the timer, or as a mechanism for measuring pulse widths

and periods of external events. These timers can be synchro-

nized to an external clock input on the TM_TMR[n] pins, an

external TM_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs

and the CAN controller to measure the width of the pulses in

the data stream to provide a software autobaud detect function

for the respective serial channels.

The GP timers can generate interrupts to the processor core,

providing periodic events for synchronization to either the sys-

tem clock or to external signals. Timer events can also trigger

other peripherals via the TRU (for instance, to signal a fault).

Each timer can also be started and/or stopped by any TRU mas-

ter without core intervention.

Watch d og Tim er (WDT)

Three on-chip software watchdog timers (WDT) can be used by

the ARM Cortex-A5 and/or SHARC+ cores. A software watch-

dog can improve system availability by forcing the processors to

a known state, via a general-purpose interrupt, or a fault, if the

timer expires before being reset by software.

The programmer initializes the count value of the timer, enables

the appropriate interrupt, then enables the timer. Thereafter,

the software must reload the counter before it counts down to

zero from the programmed value, protecting the system from

remaining in an unknown state where software that normally

resets the timer stops running due to an external noise condi-

tion or software error.

General-Purpose Counters (CNT)

A 32-bit counter (CNT) is provided that can operate in general-

purpose up/down count modes and can sense 2-bit quadrature

or binary codes as typically emitted by industrial drives or man-

ual thumbwheels. Count direction is either controlled by a level-

sensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support

and can input the push button signal of thumbwheel devices. All

three CNT0 pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable the timer to

measure the intervals between count events. Boundary registers

enable auto-zero operation or simple system warning by inter-

rupts when programmed count values are exceeded.

Housekeeping Analog-to-Digital Converter (HADC)

The housekeeping analog-to-digital converter (HADC) pro-

vides a general-purpose, multichannel successive

approximation ADC. It supports the following set of features:

• 12-bit ADC core (10-bit accuracy) with built in sample and

hold.

• Eight single-ended input channels for the BGA packag

e;

four single-ended input channels for the LQFP package.

• Throughput rates up to 1 MSPS.

• Single external reference with analog inputs between

0 V and 3.3 V.

• Selectable ADC clock frequency including the ability to

program a prescaler.

• Adaptable conversion type; allows single or continuous

conversion with option of autoscan.

• Autosequencing capability with up to eight autoconver-

sions in a single session. Each conversion can be

programmed to select one to eight input channels.

• Six data registers (individually addressable) to store con-

version values

USB 2.0 On the Go (OTG) Dual-Role Device Controller

(BGA Only)

The USB supports high speed/full speed/low speed (HS/FS/LS)

USB2.0 on the go (OTG).

The USB 2.0 OTG dual-role device controller provides a low

cost connectivity solution in industrial applications, as well as

consumer mobile devices such as cell phones, digital still cam-

eras, and MP3 players. The USB 2.0 controller allows these

devices to transfer data using a point to point USB connection

without the need for a PC host. The module can operate in a tra-

ditional USB peripheral only mode as well as the host mode

presented in the OTG supplement to the USB 2.0 specification.

The USB clock is provided through a dedicated external crystal

or crystal oscillator.

The USB OTG dual-role device controller includes a phase-

locked loop (PLL) with programmable multipliers to generate

the necessary internal clocking frequency for the USB.

Media Local Bus (MediaLB)

The automotive model has a Microchip MediaLB (MLB) slave

interface that allows the processors to function as a media local

bus device. It includes support for both 3-pin and 6-pin media

local bus protocols. The MLB 3-pin configuration supports

ADSP-SC572/SC573/ADSP-21573

Rev. 0 | Page 19 of 142 | June 2017

speeds up to 1024 × FS. The MLB 6-pin configuration supports

speed of 4096 × FS. The MLB also supports up to 63 logical

channels with up to 468 bytes of data per MLB frame.

The MLB interface supports MOST25, MOST50, and MOST150

data rates and operates in slave mode only.

2-Wire Controller Interface (TWI)

The processors include three 2-wire interface (TWI) modules

that provide a simple exchange method of control data between

multiple devices. The TWI module is compatible with the

widely used I

2

C bus standard. The TWI module offers the

capabilities of simultaneous master and slave operation and

support for both 7-bit addressing and multimedia data arbitra-

tion. The TWI interface utilizes two pins for transferring clock

(TWI_SCL) and data (TWI_SDA) and supports the protocol at

speeds up to 400 kb/sec. The TWI interface pins are compatible

with 5 V logic levels.

Additionally, the TWI module is fully compatible with serial

camera control bus (SCCB) functionality for easier control of

various CMOS camera sensor devices.

General-Purpose I/O (GPIO)

Each general-purpose port pin can be individually controlled by

manipulating the port control, status, and interrupt registers:

• GPIO direction control register specifies the direction of

each individual GPIO pin as input or output.

• GPIO control and status registers have a write one to mod-

ify mechanism that allows any combination of individu

al

GPIO pins to be modified in a single instruction, without

affecting the level of any other GPIO pins.

• GPIO interrupt mask registers allow each individual GPIO

pin to function as an interrupt to the processors. GPIO pins

defined as inputs can be configured to generate hardware

interrupts, while output pins can be triggered by software

interrupts.

• GPIO interrupt sensitivity registers specify whether indi-

vidual pins are level or edge sensitive and specify, if edge

sensitive, whether the rising edge or both the rising and

falling edges of the signal are significant.

Pin Interrupts

Every port pin on the processors can request interrupts in either

an edge sensitive or a level sensitive manner with programmable

polarity. Interrupt functionality is decoupled from GPIO opera-

tion. Five system level interrupt channels (PINT0–PINT4) are

reserved for this purpose. Each of these interrupt channels can

manage up to 32 interrupt pins. The assignment from pin to

interrupt is not performed on a pin by pin basis. Rather, groups

of eight pins (half ports) can be flexibly assigned to interrupt

channels.

Every pin interrupt channel features a special set of 32-bit mem-

ory-mapped registers that enable half-port assignment and

interrupt management. This includes masking, identification,

and clearing of requests. These registers also enable access to the

respective pin states and use of the interrupt latches, regardless

of whether the interrupt is masked or not. Most control registers

feature multiple MMR address entries to write one to set or

write one to clear them individually.

Mobile Storage Interface (MSI)

The mobile storage interface (MSI) controller acts as the host

interface for multimedia cards (MMC), secure digital memory

cards (SD), and secure digital input/output cards (SDIO). The

MSI controller has the following features:

• Support for a single MMC, SD memory, and SDIO card

• Support for 1-bit and 4-bit SD modes

• Support for 1-bit, 4-bit, and 8-bit MMC modes

• Support for eMMC 4.3 embedded NAND flash devices

•

An 11-signal external interface with clock, comman

d,

optional interrupt, and up to eight data lines

• Integrated DMA controller

• Card interface clock generation in the clock distribution

unit (CDU)

• SDIO interrupt and read wait features

SYSTEM ACCELERATION

The following sections describe the system acceleration blocks

of the ADSP-SC57x/ADSP-2157x processors.

Finite Impulse Response (FIR) Accelerator

The finite impulse response (FIR) accelerator consists of a

1024 word coefficient memory, a 1024 word deep delay line for

the data, and four MAC units. A controller manages the acceler-

ator. The FIR accelerator runs at the peripheral clock frequency.

The FIR accelerator can access all memory spaces and can run

concurrently with the other accelerators on the processor.

Infinite Impulse Response (IIR) Accelerator

The infinite impulse response (IIR) accelerator consists of a

1440 word coefficient memory for storage of biquad coeffi-

cients, a data memory for storing the intermediate data, and one

MAC unit. A controller manages the accelerator. The IIR accel-

erator runs at the peripheral clock frequency. The IIR

accelerator can access all memory spaces and run concurrently

with the other accelerators on the processor.

SYSTEM DESIGN

The following sections provide an introduction to system design

features and power supply issues.

Clock Management

The processors provide three operating modes, each with a dif-

ferent performance and power profile. Control of clocking to

each of the processor peripherals reduces power consumption.

The processors do not support any low power operation modes.

Control of clocking to each of the processor peripherals can

reduce the power consumption.

ADSP-SC572/SC573/ADSP-21573

Rev. 0 | Page 20 of 142 | June 2017

Reset Control Unit (RCU)

Reset is the initial state of the whole processor, or the core, and

is the result of a hardware or software triggered event. In this

state, all control registers are set to default values and functional

units are idle. Exiting a full system reset starts with the core

ready to boot.

The reset control unit (RCU) controls how all the functional

units enter and exit reset. Differences in functional require-

ments and clocking constraints define how reset signals are

generated. Programs must guarantee that none of the reset

functions put the system into an undefined state or causes

resources to stall. This is particularly important when the core

resets (programs must ensure that there is no pending system

activity involving the core when it is reset).

From a system perspective, reset is defined by both the reset tar-

get and the reset source.

The reset target is defined as the following:

• System reset—all functional units except the RCU are set to

default states.

• Hardware reset—all functional units are set to default states

without exception. History is lost.

• Core only reset— affects the core only. When in

reset state,

the core is not accessed by any bus master.

The reset source is defined as the following:

• System reset—can be triggered by software (writing to the

RCU_CTL register) or by another functional unit such as

the dynamic power management (DPM) unit or any of the

SEC, TRU, or emulator inputs.

•

Hardware reset—the SYS_HWRST

input signal asserts

active (pulled down).

• Core only reset—affects only the core. The core is not

accessed by any bus master when in reset state.

• Trigger request (peripheral).

Clock Generation Unit (CGU)

The ADSP-SC57x/ADSP-2157x processors support two inde-

pendent PLLs. Each PLL is part of a clock generation unit

(CGU); see Figure 7. Each CGU can be either driven externally

by the same clock source or each can be driven by separate

sources. This provides flexibility in determining the internal

clocking frequencies for each clock domain.

Frequencies generated by each CGU are derived from a com-

mon multiplier with different divider values available for each

output.

The CGU generates all on-chip clocks and synchronization sig-

nals. Multiplication factors are programmed to define the

PLLCLK frequency.

Programmable values divide the PLLCLK frequency to generate

the core clock (CCLK), the system clocks, the DDR1/DDR2/

DDR3 clock (DCLK), and the output clock (OCLK). For more

information on clocking, see the ADSP-SC57x/ADSP-2157x

SHARC+ Processor Hardware Reference.

Writing to the CGU control registers does not affect the behav-

ior of the PLL immediately. Registers are first programmed with

a new value and the PLL logic executes the changes so it transi-

tions smoothly from the current conditions to the new

conditions.

System Crystal Oscillator and USB Crystal Oscillator

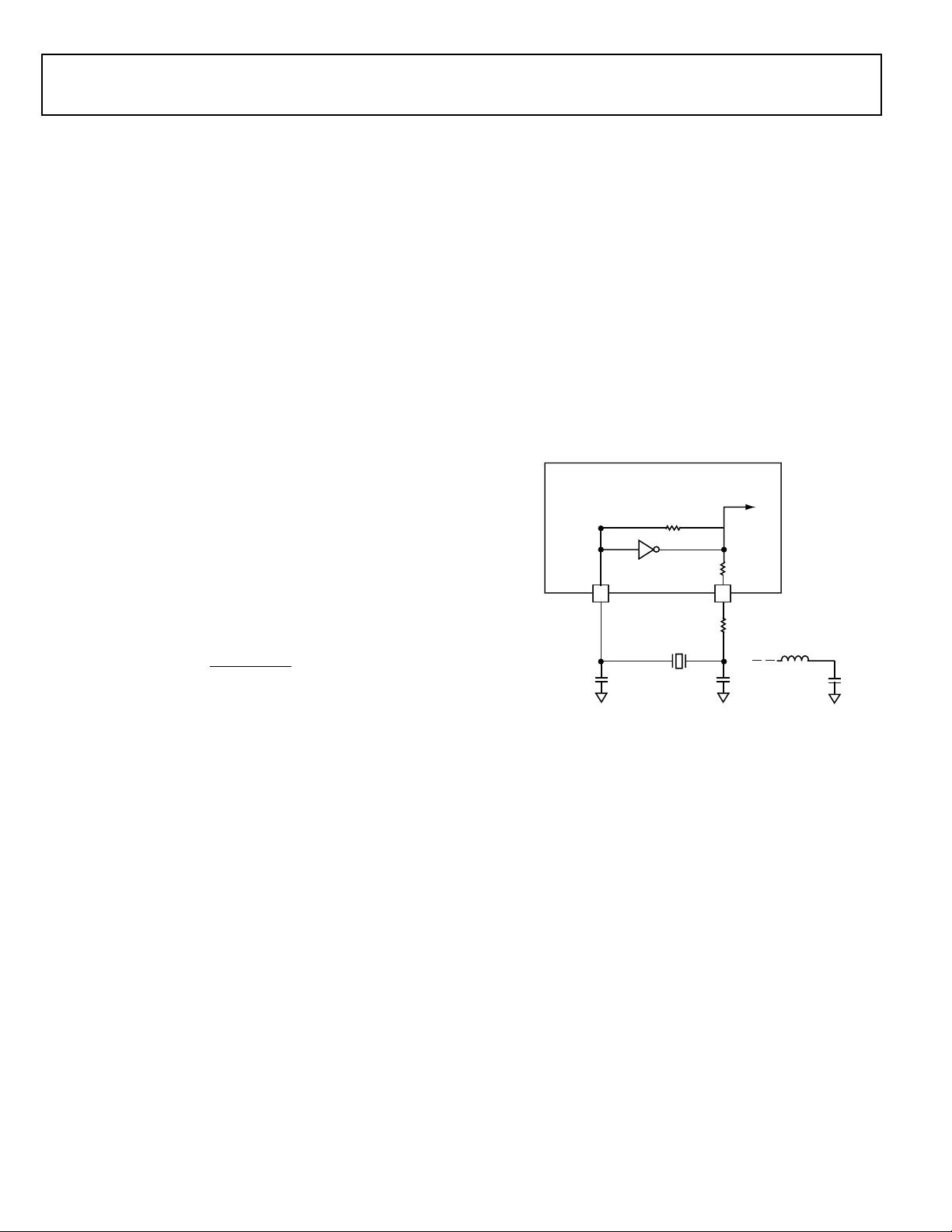

The processor can be clocked by an external crystal

(see Figure 6), a sine wave input, or a buffered, shaped clock

derived from an external clock oscillator. If using an external

clock, it must be a TTL-compatible signal and must not be

halted, changed, or operated below the specified frequency

during normal operation. This signal is connected to the SYS_-

CLKINx pin and the USB_CLKIN pin of the processor. When

using an external clock, the SYS_XTALx pin and the USB_X-

TAL pin must be left unconnected. Alternatively, because the

processor includes an on-chip oscillator circuit, an external

crystal can be used.

For fundamental frequency operation, use the circuit shown in

Figure 6. A parallel resonant, fundamental frequency, micro-

processor grade crystal is connected across the SYS_CLKINx

pin and the SYS_XTALx pin. The on-chip resistance between

the SYS_CLKINx pin and the SYS_XTALx pin is in the 500 kΩ

range. Further parallel resistors are typically not recommended.

The two capacitors and the series resistor, shown in Figure 6,

fine tune phase and amplitude of the sine frequency. The capac-

itor and resistor values shown in Figure 6 are typical values

only. The capacitor values are dependent upon the load capaci-

tance recommendations of the crystal manufacturer and the

physical layout of the printed circuit board (PCB). The resistor

value depends on the drive level specified by the crystal manu-

facturer. The user must verify the customized values based on

careful investigations on multiple devices over the required

temperature range.

Figure 6. External Crystal Connection

SYS_CLKINx

TO PLL

CIRCUITRY

FOR OVERTONE

OPERATION ONLY

NOTE: VALUES MARKED WITH * MUST BE CUSTOMIZED, DEPENDING

ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR

FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE

OF 18 pF MUST BE TREATED AS A MAXIMUM.

18 pF*

18 pF

*

*

SHARC

®

PROCESSOR

ȍ

SYS_XTALx

Nȍ

ADSP-SC572/SC573/ADSP-21573

剩余141页未读,继续阅读

153 浏览量

2014-07-30 上传

143 浏览量

303 浏览量

610 浏览量

142 浏览量

132 浏览量

2024-06-23 上传

Audio707

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功