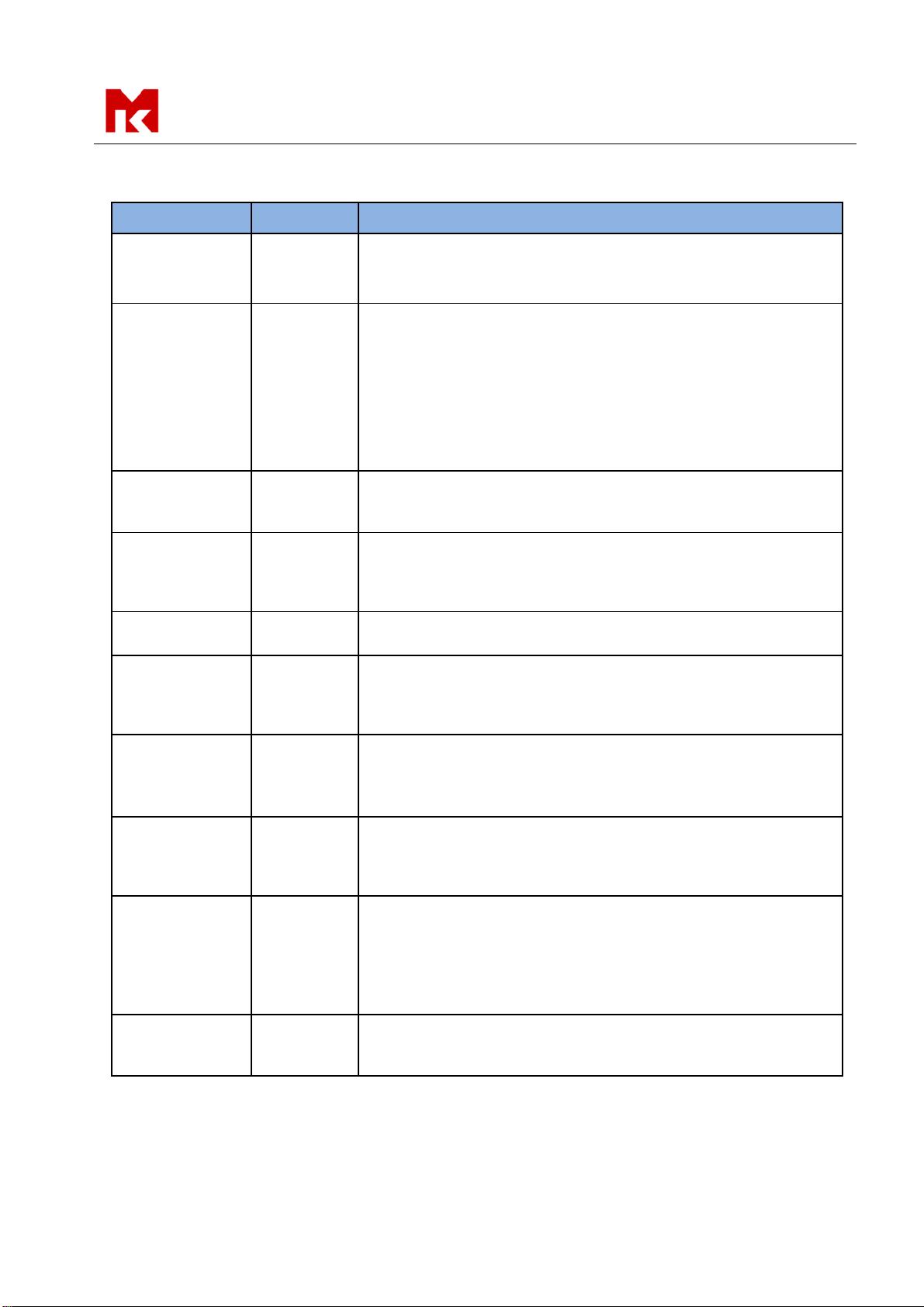

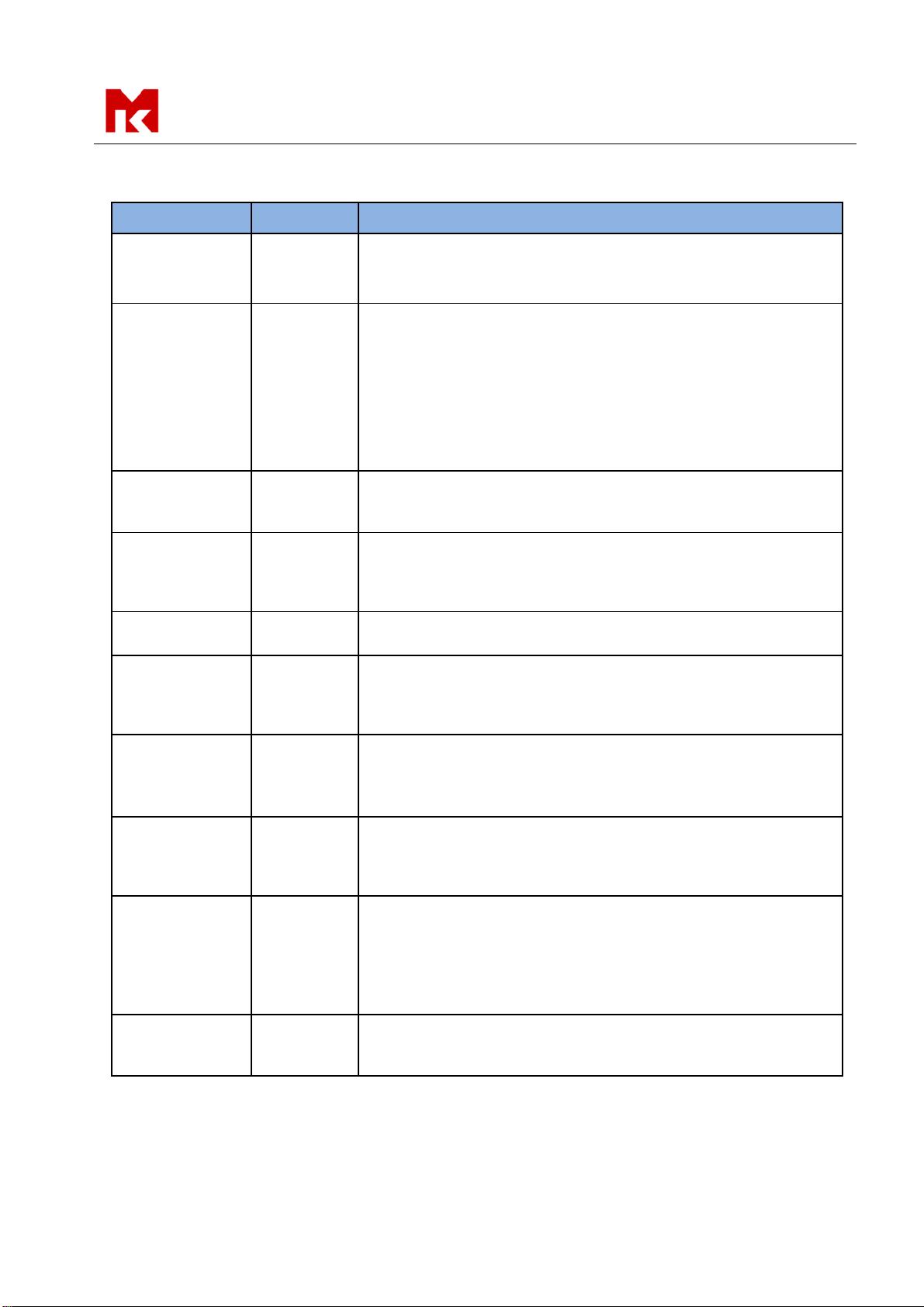

Ball Description

Clock: CK and /CK are differential clock inputs. All address and control input

signals are sampled on the crossing of the positive edge of CK and negative

edge of /CK. Output (read) data is referenced to the crossings of CK and /CK

Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock

signals and device input buffers and output drivers. Taking CKE Low provides

Pre-charge Power-Down and Self Refresh operation (all banks idle), or Active

Power-Down (Row Active in any bank). CKE is asynchronous for self-refresh exit.

After V

REFCA

has become stable during the power on and initialization

sequence, it must be maintained during all operations (including Self-Refresh).

CKE must be maintained high throughout read and write accesses. Input buffers,

excluding CK, /CK, ODT and CKE are disabled during Power Down. Input

buffers, excluding CKE, are disabled during Self Refresh.

Chip Select: All commands are masked when /CS is registered HIGH. /CS

provides for external Rank selection on systems with multiple Ranks. /CS is

considered part of the command code.

On Die Termination: ODT (registered HIGH) enables termination resistance

internal to the DDR3/L SDRAM. When enabled, ODT is only applied to each

DQ, DQS, /DQS and DM. The ODT pin will be ignored if the Mode Register

(MR1) is programmed to disable ODT.

Command Inputs: /RAS, /CAS and /WE (along with /CS) define the

command being entered.

Input Data Mask: DM is an input mask signal for write data. Input data is

masked when DM is sampled HIGH coincident with that input data during a

Write access. DM is sampled on both edges of DQS.

Bank Address Inputs: BA0-BA2 define the bank to which an Active, Read,

Write or Pre-charge command is being applied. Bank address also determines if

the mode register or extended mode register is to be accessed during a MRS

cycle.

Address Inputs: Provide the row address for Active commands and the column

address for Read/Write commands to select one location out of the memory

array in the respective bank. The address inputs also provide the op-code during

Mode Register Set commands. (A10/AP and A12/BC have additional functions,

see below)

Auto Pre-charge: A10 is sampled during Read/Write commands to determine

whether Auto pre-charge should be performed to the accessed bank after the

Read/Write operation (HIGH: Auto pre-charge; LOW: No Auto pre-charge). A10

is sampled during a Pre-charge command to determine whether the Pre-charge

applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to

be pre-charged, the bank is selected by bank addresses.

Burst Chop: A12 is sampled during Read and Write commands to determine if

burst chop (on-the-fly) will be performed. (HIGH: no burst chop, LOW: burst

chopped). See command truth table for details.