使用QuartusⅡ设计8位全加器的原理图输入法

需积分: 15 174 浏览量

更新于2024-07-31

收藏 495KB PPT 举报

"第四章_原理图输入方法.ppt"

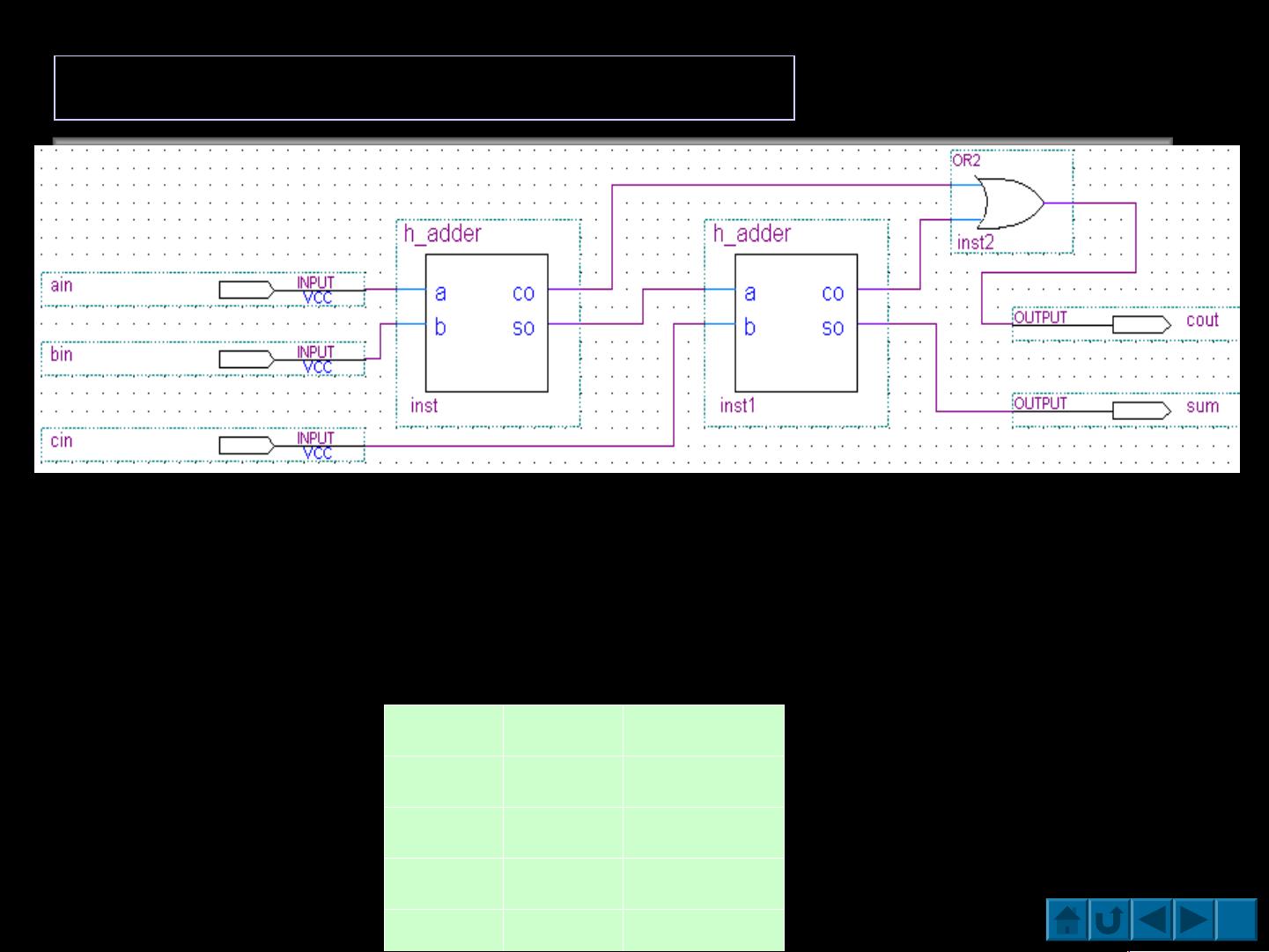

本资源主要讲解了使用QuartusⅡ软件通过原理图输入方法设计电子线路,特别是针对8位全加器的层次化设计过程。全加器是一种基本的数字逻辑电路,用于执行二进制加法操作,包括进位。在这一章中,主要包含了以下知识点:

1. **1位全加器设计**:全加器由两个半加器构成,每个半加器处理两个输入位的加法,同时考虑来自上一位的进位信号。通过真值表可以理解全加器的工作原理,例如C1和C2是两个半加器的进位输入,Cout是全加器的进位输出。

2. **设计步骤**:设计8位全加器的步骤包括创建工程文件夹、输入设计项目、设置可调用元件、绘制顶层原理图以及设置工程和时序仿真。在原理图中,需要正确连接各个全加器单元,确保进位信号的正确传递。

3. **层次化设计**:为了扩展设计,可以将1位全加器作为基本元件构建多位全加器。进位信号可以通过串行或并行的方式产生。串行进位意味着每个全加器的进位输出连接到下一个全加器的进位输入,而并行进位则涉及所有进位信号的并行计算。

4. **扩展设计**:

- **设计2:7人表决电路**:可以利用全加器的进位信号来实现表决功能。如果同意的人数超过半数(即4人),进位信号Cout将为1,表示表决通过,触发绿色指示灯;反之,如果同意人数不足4人,Cout为0,红色指示灯亮起。

- **设计3:n位行波进位补码加/减法器**:基于全加器设计的补码加法器,遵循补码加法的公式,可以进行正负数的加减运算。在行波进位中,进位信号从低位向高位逐位传递,实现n位的加减运算。

5. **时序仿真**:在完成设计后,使用QuartusⅡ的工程设置窗进行时序仿真,以验证设计的正确性。例如,全加器的仿真波形可以显示输入和输出信号随时间的变化,帮助分析电路的行为。

通过以上内容的学习,读者能够掌握利用EDA软件进行原理图输入方式的电子线路设计的基本流程,并能够应用这些知识设计更复杂的数字逻辑系统。

2009-07-17 上传

2022-09-14 上传

2023-06-02 上传

2023-05-25 上传

2023-07-13 上传

2023-03-08 上传

2023-06-02 上传

2023-06-10 上传

2023-06-02 上传

v_the

- 粉丝: 0

- 资源: 3

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布