TAGE-SC-L Branch Predictors

∗

Andr

´

e Seznec

INRIA/IRISA

Outline

The TAGE predictor [12] is considered as one of the

most storage effective global branch/path history predictors.

It has been shown that associated with small adjunct predic-

tors like a statistical corrector (SC for short) and/or a loop

predictor (L for short) [11, 10], TAGE can even be more ef-

fective. In this study, we explore the performance limits of

these TAGE-SC-L predictors for respectively 32Kbits stor-

age budget, 256 Kbits storage budget and quasi-unlimited

(< 2 Gbits) storage budget.

With a 32Kbits storage budget, only a very limited stor-

age budget can be invested in the adjunct predictors. Then

our submitted predictor used most of its storage budget on

the TAGE predictor and features only a small loop predictor

LP and a simple corrector filter CF. The submitted 32Kbits

predictor achieves 3.315 MPKI on the CBP-4 traces.

With a larger storage budget, one can invest more signifi-

cant storage budget in the adjunct predictors. The submitted

256Kbits TAGE-SC-L predictor features a TAGE predictor,

a loop predictor LP and a quite complex (≈ 45 Kbits) statis-

tical corrector SC that exploits local history, global branch

history and return-associated branch history. The 256Kbits

TAGE-SC-L predictor achieves 2.365 MPKI on the CBP-4

traces.

The no-limit budget allows to use a statistical corrector

build with many components exploiting global branch and

path histories, local histories and some form of skeleton his-

tories. The submitted predictor achieves 1.782 MPKI on the

CBP-4 traces.

1. General view of the TAGE-SC-L predictor

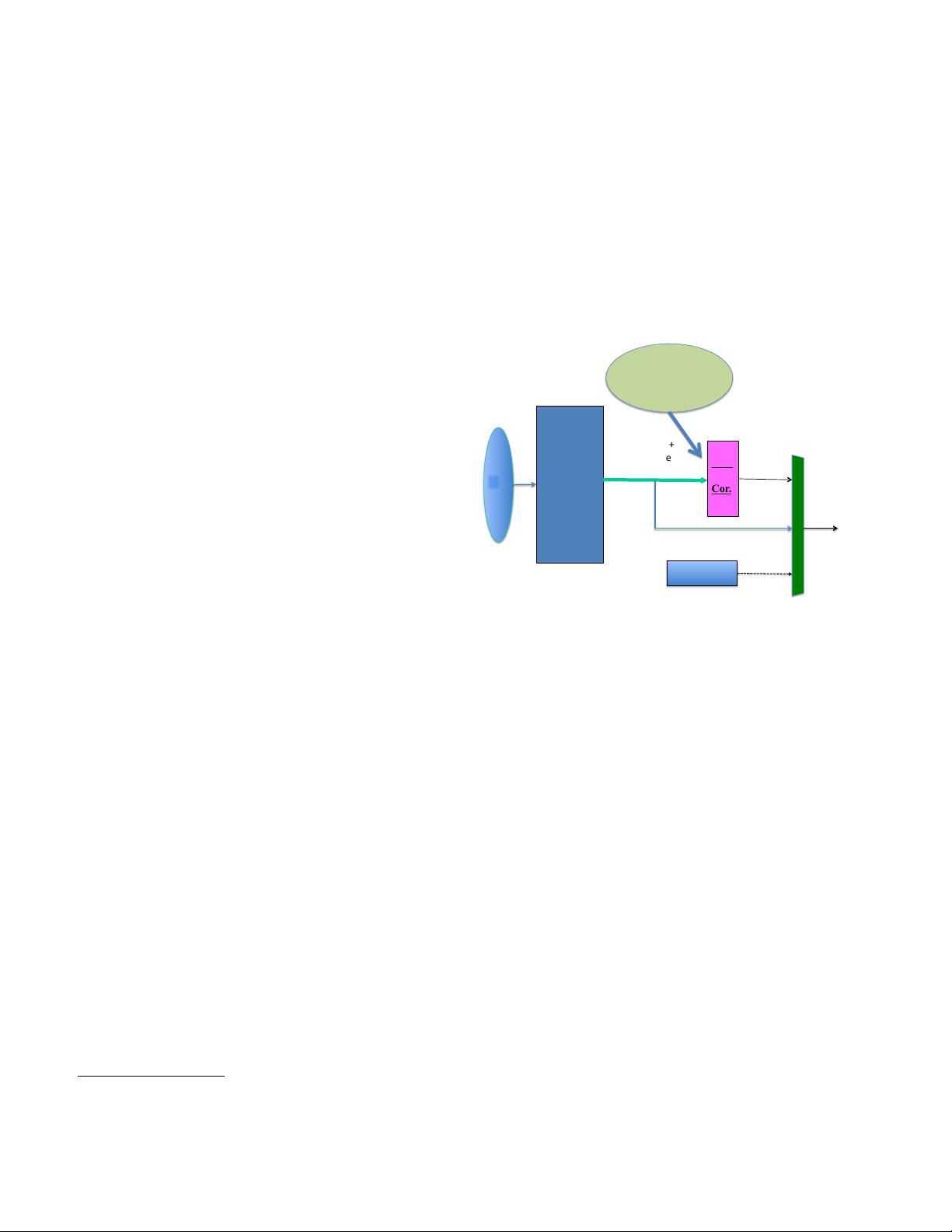

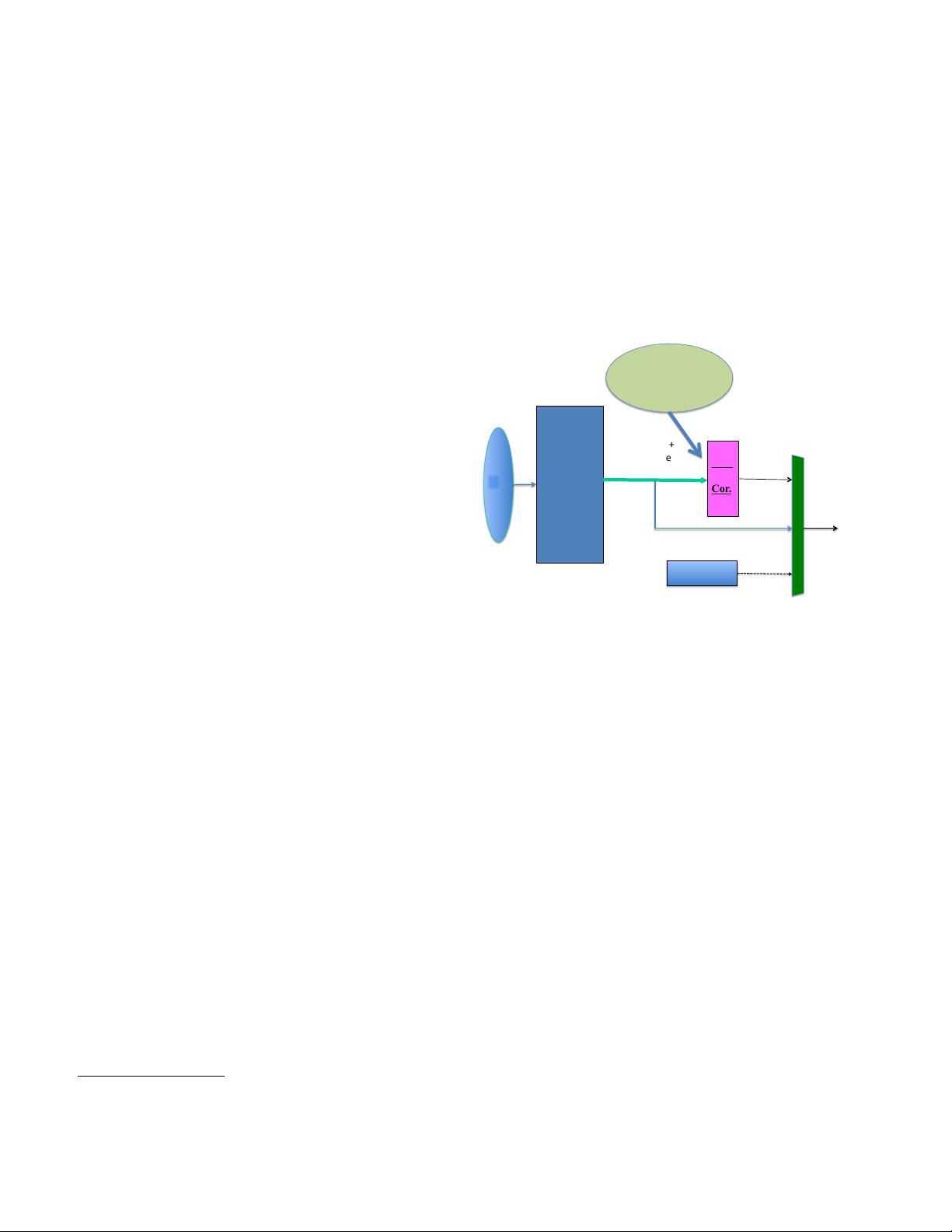

The TAGE-SC-L predictor consists of three components:

a TAGE predictor, a statistical corrector predictor and a loop

predictor (Figure 1).

The TAGE predictor provides the main prediction. Then

this prediction is used by the statistical corrector predictor

which role consists in confirming (general case) or reverting

∗

This work was partially supported by the European Research Council

Advanced Grant DAL No 267175

(Main)

!!

TAGE

!

Predictor

Stat.

!

Cor.

Predic(on!+!

Confidence!

Loop!!Predictor!

PC

Global!history!

Global,!local,!

skeleton!histories!

Figure 1. The TAGE-SC-L predictor: a TAGE

predictor backed with a Statistical Corrector

predictor and a loop predictor

the prediction. The statistical predictor reverts the predic-

tion when it appears that, in similar circumstances (predic-

tion, branch histories, branch confidence, ..) TAGE statisti-

cally mispredicted. The loop predictor is useful to predict

regular loops with long loop bodies.

2. The TAGE conditional branch predictor

The TAGE predictor was described in [12] and [9]. Only

marginal modifications are introduced in this study.

Figure 2 illustrates a TAGE predictor. The TAGE pre-

dictor features a base predictor T0 in charge of providing

a basic prediction and a set of (partially) tagged predictor

components Ti. These tagged predictor components Ti, 1 ≤

i ≤ M are indexed using different history lengths that form

a geometric series [6], i.e, L(i) = (int)(α

i−1

∗L(1)+0.5).

In practice, the set of history lengths used in the sub-

mitted predictors were obtained, first through exploring the

use of a geometric series, then through refinements. These

refinements led to limited benefits (< 0.5% ) on accuracy.

Throughout this paper, the base predictor will be a sim-

1