Rev. 1.3 17

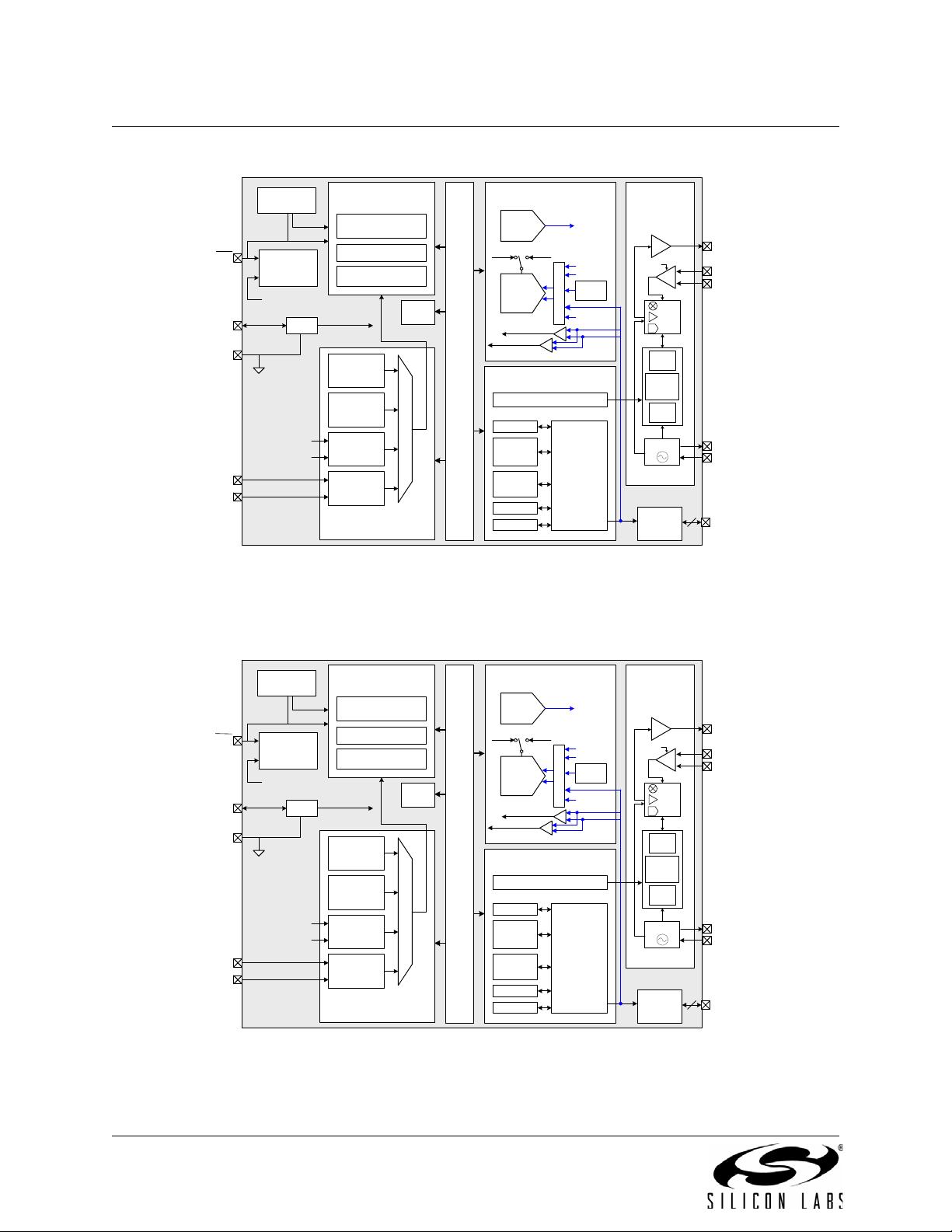

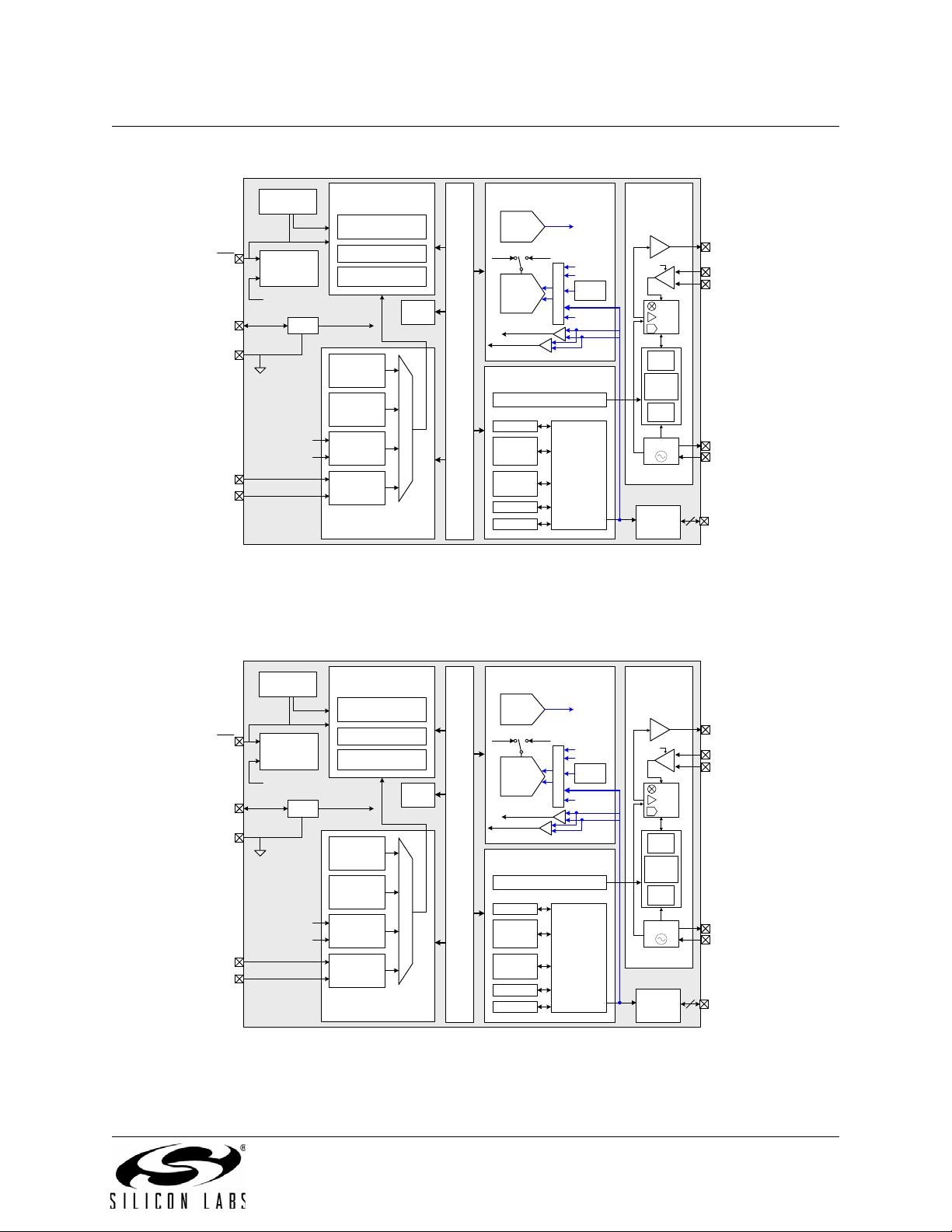

Si1000/1/2/3/4/5

1. System Overview

Si1000/1/2/3/4/5 devices are fully integrated mixed-signal system-on-a-chip MCUs. Highlighted features

are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

240–960 MHz EZRadioPRO

®

transceiver

Single/Dual battery operation with on-chip dc-dc boost converter

High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

In-system, full-speed, non-intrusive debug interface (on-chip)

True 10-bit 300 ksps 23-channel single-ended ADC with analog multiplexer

6-bit programmable current reference

Precision programmable 24.5 MHz internal oscillator with spread spectrum technology

64 kB or 32 kB of on-chip flash memory

4352 bytes of on-chip RAM

SMBus/I

2

C, Enhanced UART, and two Enhanced SPI serial interfaces implemented in hardware

(SPI1 is dedicated for communication with the EZRadioPRO peripheral)

Four general-purpose 16-bit timers

Programmable counter/timer array (PCA) with six capture/compare modules and watchdog timer

(WDT) function

On-chip power-on reset, V

DD

monitor, and temperature sensor

Two on-chip voltage comparators with 18 touch sense inputs

19 or 22 port I/O (5 V tolerant except for GPIO_0, GPIO_1, and GPIO_2)

With on-chip power-on reset, V

DD

monitor, watchdog timer, and clock oscillator, the Si1000/1/2/3/4/5

devices are truly standalone system-on-a-chip solutions. The flash memory can be reprogrammed even in-

circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User

software has complete control of all peripherals, and may individually shut down any or all peripherals for

power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip

resources), full speed, in-circuit debugging using the production MCU installed in the final application. This

debug logic supports inspection and modification of memory and registers, setting breakpoints, single

stepping, and run and halt commands. All analog and digital peripherals are fully functional while debug-

ging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging

without occupying package pins.

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (–40 to +85 °C).

The Port I/O and RST

pins are tolerant of input signals up to 5 V. The Si1000/1/2/3/4/5 are available in a

42-pin LGA package (lead-free and RoHS compliant). See Table 2.1 for ordering information. Block dia-

grams are included in Figure 1.1 through Figure 1.6.

The transceiver's extremely low receive sensitivity (–121 dBm) coupled with industry leading +20 dBm out-

put power ensures extended range and improved link performance. Built-in antenna diversity and support

for frequency hopping can be used to further extend range and enhance performance. The advanced radio

features including continuous frequency coverage from 240–960 MHz in 156 Hz or 312 Hz steps allow pre-

cise tuning control. Additional system features such as an automatic wake-up timer, low battery detector,

64 byte TX/RX FIFOs, automatic packet handling, and preamble detection reduce overall current con-

sumption. The transceivers digital receive architecture features a high-performance ADC and DSP-based

modem which performs demodulation, filtering, and packet handling for increased flexibility and perfor-

mance. The direct digital transmit modulation and automatic PA power ramping ensure precise transmit

modulation and reduced spectral spreading, ensuring compliance with global regulations including FCC,

ETSI, ARIB, and 802.15.4d regulations.

An easy-to-use calculator is provided to quickly configure the radio settings, simplifying customer's system

design and reducing time to market.