"数字集成电路英文课件:静态MOS门电路设计与应用"

版权申诉

99 浏览量

更新于2024-02-22

收藏 2.44MB PPT 举报

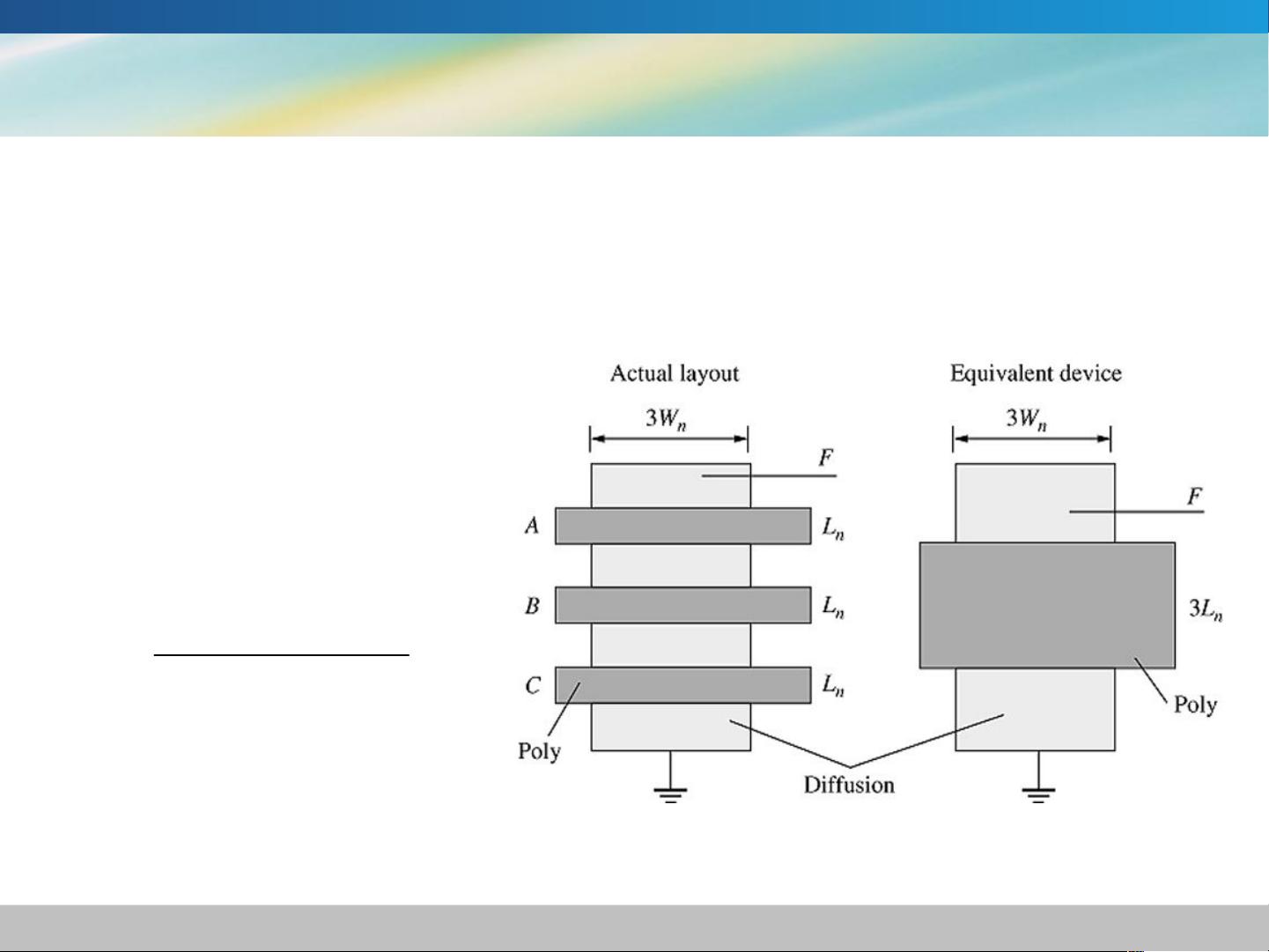

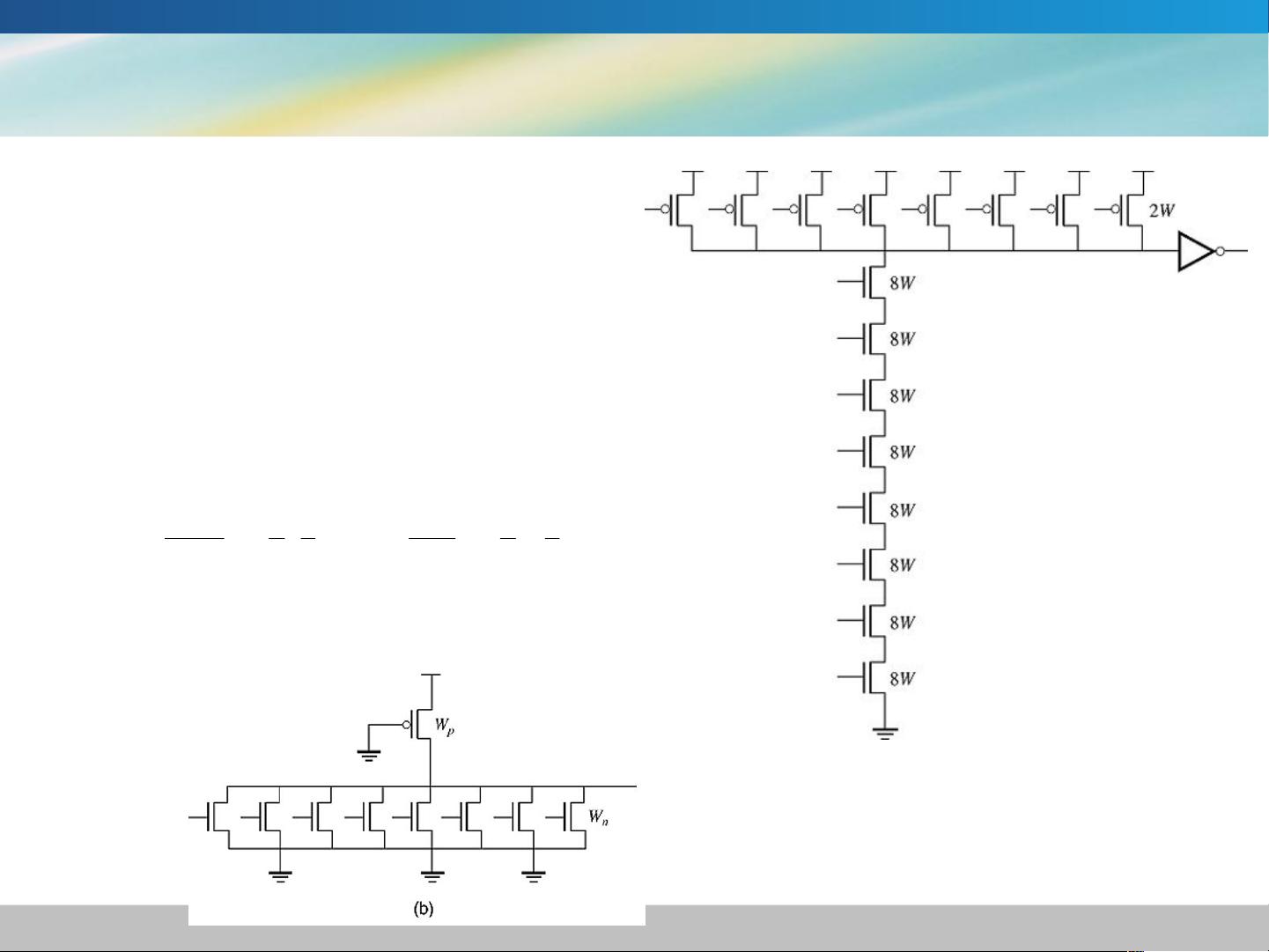

Chapter 5 of the Digital Integrated Circuits course at the Faculty of Materials and Energy at Guangdong University of Technology focused on Static MOS Gate Circuits. The chapter covered various topics including an introduction and basic knowledge, CMOS gate circuits, complex CMOS gate circuits, XOR gates and XNOR gates, multiplexers, triggers and latches, D-flip flops and D-latches, and the power consumption and trade-offs between power consumption and delay in CMOS gate circuits.

The chapter began with an introduction to the design of combinational and sequential CMOS static logic gates. Combinational logic circuits, such as NAND, NOR, XOR, and multiplexers, were discussed in terms of their voltage transfer characteristics, transistor sizing, delay, and power consumption. Sequential logic circuits, which have the ability to store information, were also introduced. These circuits have outputs that are both functions of the input values and functions of the output values, with positive feedback loops between the input and output. This section included a discussion of triggers and latches, as well as D-flip flops and D-latches.

Overall, the chapter provided a comprehensive overview of the design and analysis of static MOS gate circuits. Students were introduced to the various types of logic gates and learned about their design considerations, performance characteristics, and trade-offs. This knowledge is essential for understanding the behavior and performance of digital integrated circuits, and is foundational for further study and practical application in the field.

2021-09-17 上传

2021-09-17 上传

2022-07-04 上传

2022-06-16 上传

2021-09-17 上传

2022-07-03 上传

2021-09-17 上传

2022-06-21 上传

2021-09-17 上传

智慧安全方案

- 粉丝: 3837

- 资源: 59万+

最新资源

- Flex 3 Cookbook.pdf

- ibatis_developing.pdf (ibatis开发指南)

- JavaScript字符串函数大全

- Modicon Modbus Protocol Ref. Guide1996

- 编码的奥秘.pdf 计算机原理

- linux svn帮助

- 初学者如何快速开发arm

- PADS Power-PCB

- FileStream 构造函数

- 按键程序(包含长按键)

- db2数据库的sqlcode

- 一些常用的SQL语句,很有用的。

- strutsInAction.pdf

- oracle标准语法速查表

- SAP 4.6 Basic Skills Self-Study Edition 2.00

- unix基本面试问答