Verilog HDL学习指南

需积分: 10 112 浏览量

更新于2024-07-28

收藏 263KB PDF 举报

"Verilog HDL 教学资料"

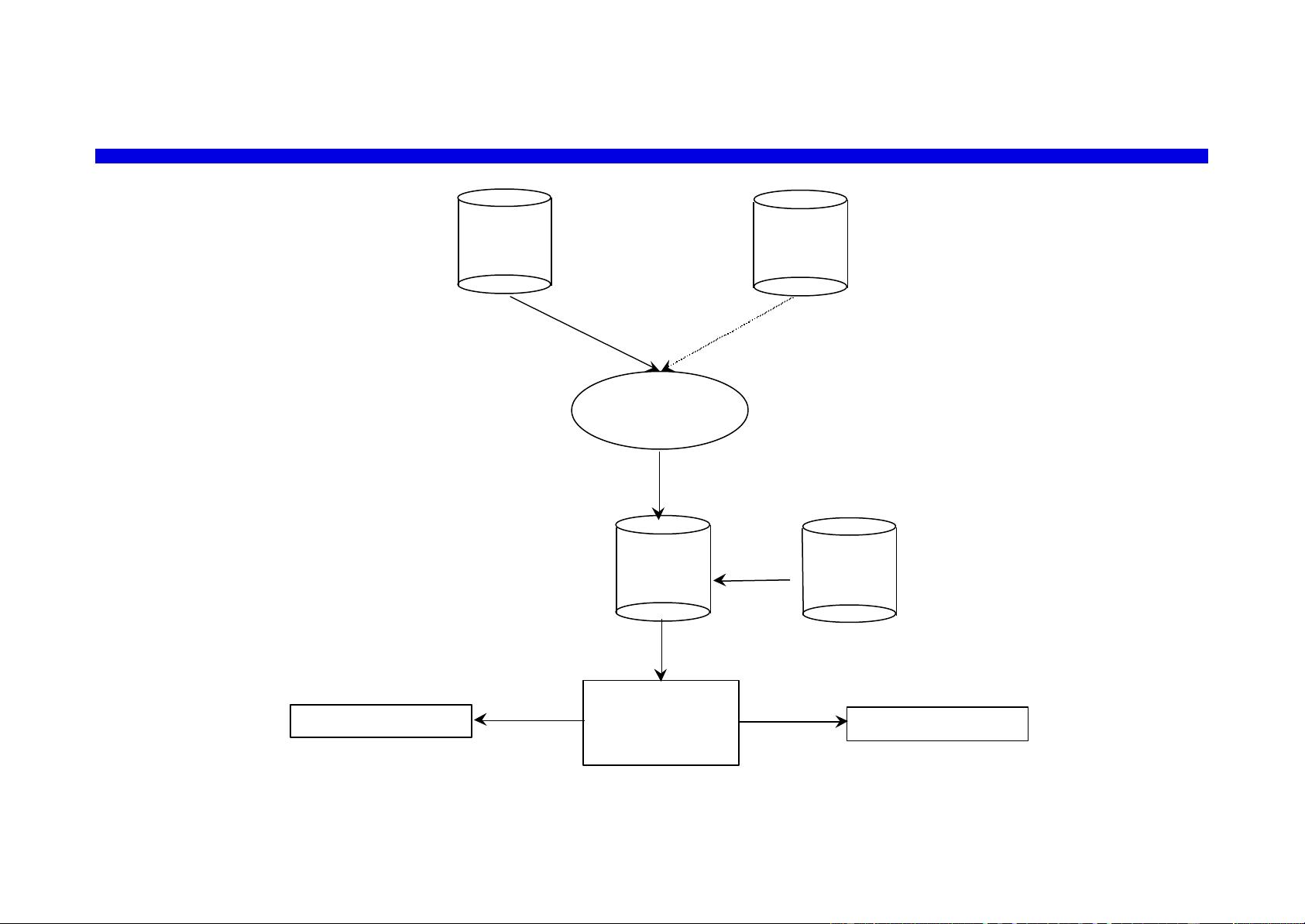

Verilog HDL 是一种广泛使用的硬件描述语言,用于设计和描述数字系统。它不仅是仿真工具,还可以用于综合,即将设计转换成实际的集成电路。本资料旨在帮助学习者掌握Verilog的基础知识、建模结构以及延迟概念在模拟中的影响。

课程目标包括:

1. 学习Verilog的基本构造,如语法和语句。

2. 理解Verilog的建模结构,如何用它来构建模块。

3. 掌握延迟的概念及其在模拟仿真中的作用。

课程大纲涵盖:

1. Verilog概述:介绍Verilog作为硬件描述语言的角色及其在数字系统设计中的应用。

2. Verilog模型的基本结构:深入理解构成Verilog模型的基本元素。

3. Verilog模块的组件:

- 端口(Ports):定义模块间的交互界面。

- 数据类型(Data Types):包括位、字节、整数、向量等,用于表示硬件逻辑的值。

- 赋值和数值(Assigning Values and Numbers):学习如何给变量赋值以及数值的表示方式。

- 运算符(Operators):涵盖逻辑、算术、比较等各种运算符的使用。

4. 行为建模(Behavioral Modeling):

- 连续赋值(Continuous Assignments):实现即时的逻辑关系。

- 原型块(Procedural Blocks):如always块,用于定义时序逻辑。

5. 结构建模(Structural Modeling):将设计分解为基本逻辑单元,如门和触发器,并组合成更复杂的电路。

6. Verilog环境总结:了解开发、仿真和综合所需的软件工具和环境。

Verilog的历史始于1984年,由Gateway Design Automation创建。1989年,Cadence公司收购了Gateway并推出了Verilog-XL模拟器。1990年,Cadence正式公开Verilog。随后,Open Verilog International (OVI)成立以控制语言规范。1993年,OVI发布了版本2.0,并被IEEE采纳为标准,即Verilog 1364。

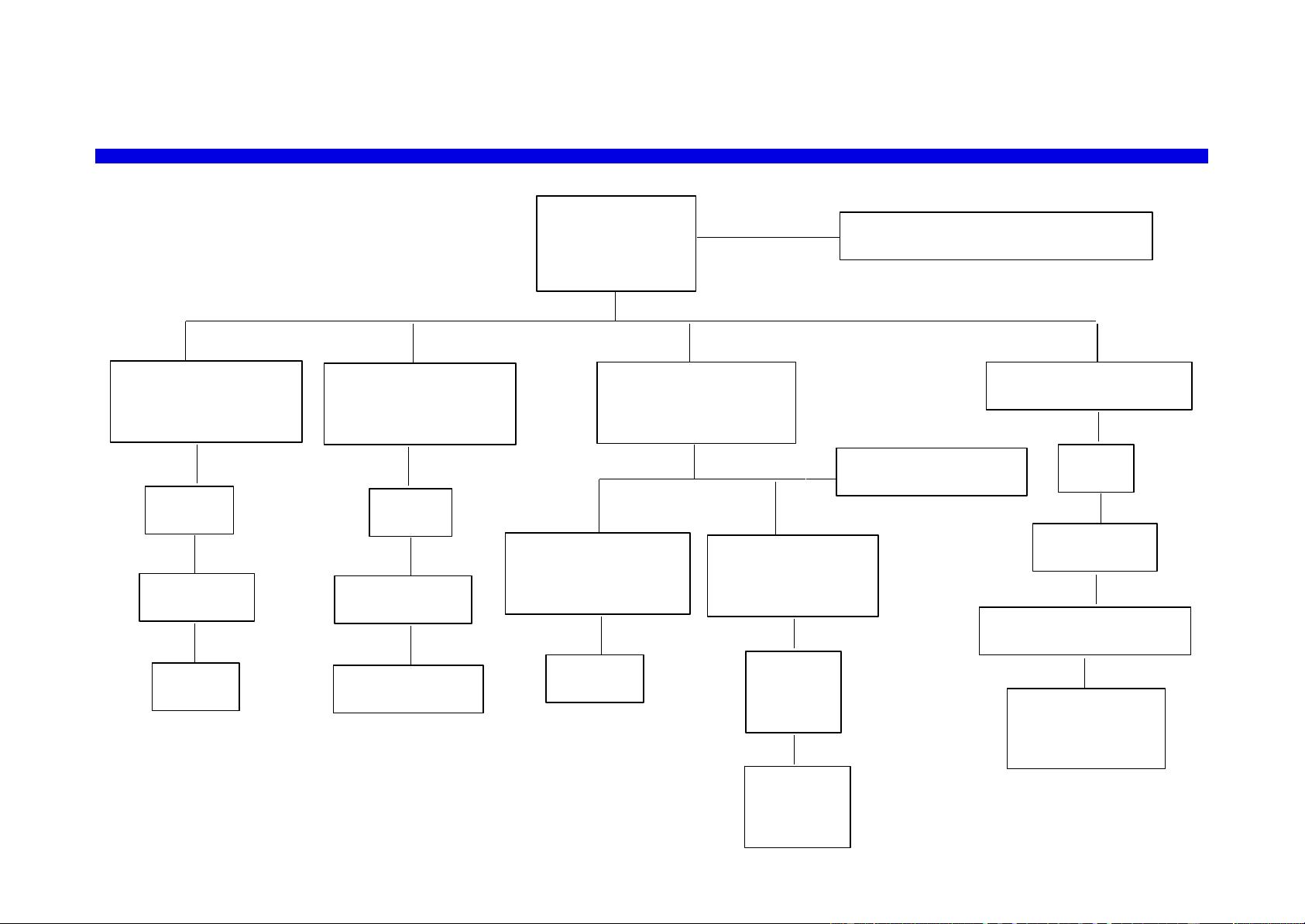

Verilog的结构类似于C语言,采用模块化的编程方法,使得设计可以分层次进行,便于管理和复用。通过学习Verilog,设计者能够描述数字逻辑的各个层面,从高层次的行为到低层次的门级实现,从而实现完整的硬件系统设计。

1000 浏览量

1198 浏览量

930 浏览量

115 浏览量

2009-02-09 上传

157 浏览量

112 浏览量

2022-09-22 上传

wang_chuan99

- 粉丝: 0

最新资源

- ReactJS实现的COVID-19追踪器:实时数据与趋势分析

- spring boot+mybatis开发的全栈个人博客系统

- 掌握LED灯自动闪烁实验教程与源代码分享

- 易语言高级表格库2.8#0版eGrid.fne更新与特性

- CSS-Spinner:纯CSS实现的12款优雅加载动画

- Go语言实现的fullcycle2持续集成教程

- Python代码库:辐射传热过程的实现与模拟

- 利用jQuery实现表格排序功能的方法

- 单相异步电动机FCMDL模型开发与MATLAB实现

- 易语言表格支持库2.8#0版发布:兼容性修正与功能增强

- pgRouting方向API实现:Node.js与Express的完整应用

- PCHunter_32X64_v1.57:增强版安全辅助工具发布

- 易语言客户管理模块功能与应用

- 实现无限滚动页面:使用Ajax和Infinite Ajax Scroll库

- JavaScript实现的供应链任务管理系统

- 探索六种DCT图像融合技术在Matlab开发中的应用