七段译码器EDA实验报告:1181002038_张璐矾

需积分: 0 90 浏览量

更新于2024-08-04

收藏 288KB DOCX 举报

本篇实验报告是关于电子设计自动化(EDA)实验中的多路数据选择器,具体为七段译码器设计。实验对象是计算机科学与技术二班学生张璐矾,学号1181002038,于2020年10月16日进行实验,由指导老师邱德惠指导。

实验内容聚焦于七段译码器的设计与实现,该器件的核心功能是将输入的8421BCD码转换为相应的七段显示代码,通过FPGA(Field-Programmable Gate Array,可编程逻辑阵列)器件构建译码电路,将这些代码驱动到七个发光二极管(LED)上,形成数字或字符的显示。实验涉及的主要步骤包括理解实验原理、设计电路结构、编写Verilog代码、编译和仿真波形、查看RTL( Register Transfer Level)代码以及对引脚功能的绑定和分析。

实验原理部分,通过拨码开关产生8421BCD码,这是一种十进制编码方式,每个二进制位对应不同的四位代码。FPGA负责根据接收到的BCD码生成对应的七段显示码,例如0对应0000,1对应0001等。设计过程中,输入信号d_in是四个二进制位的BCD码,输出则是各个段的驱动信号a-g以及小数点dp,其中dp在这个实验中固定为0,ds则用于控制所有七段数码管,仅显示一个数码管。

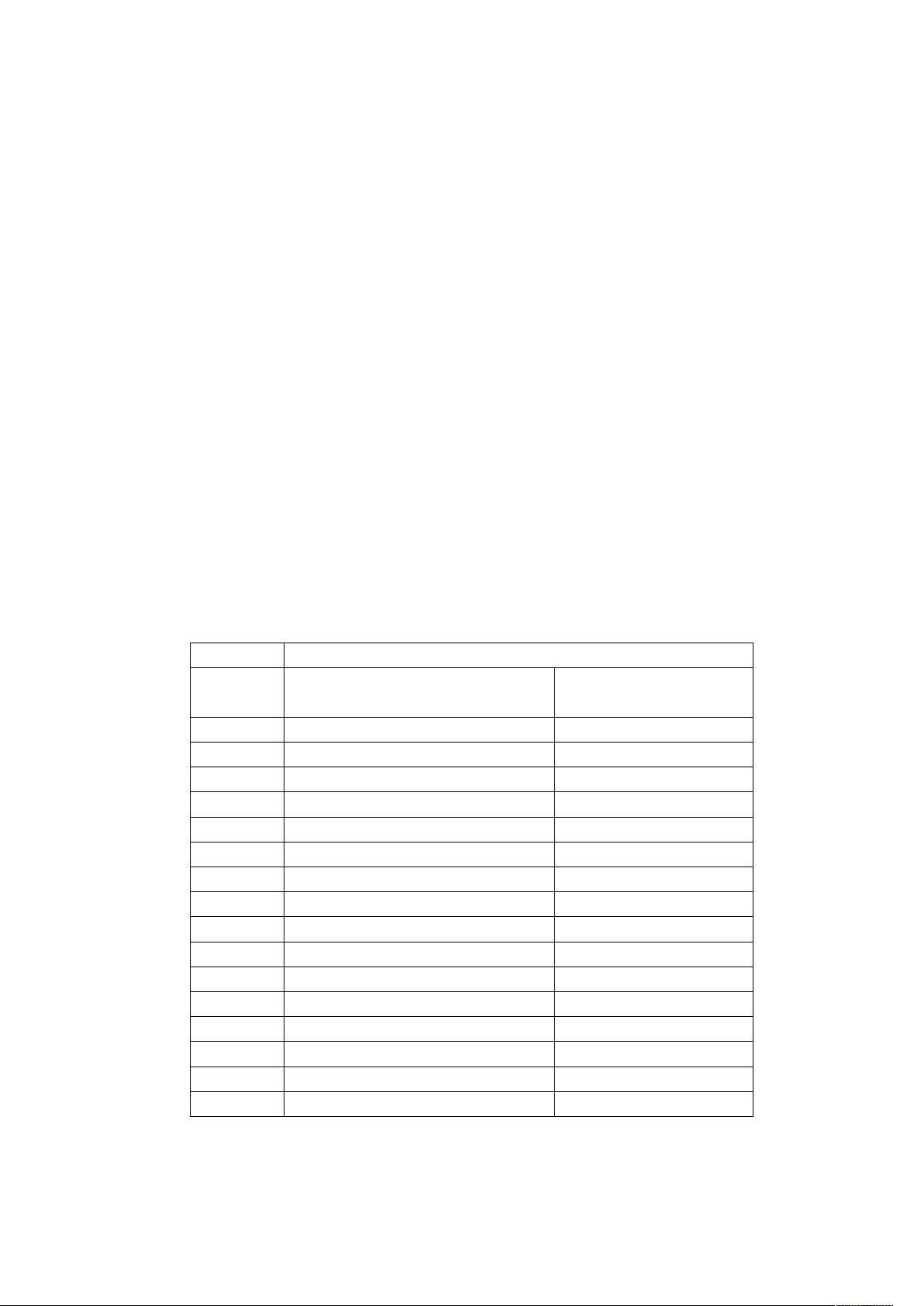

真值表展示了不同输入BCD码与对应七段显示码之间的映射关系。代码部分采用Verilog语言,定义了一个名为SevenSegment的模块,接收d_in作为输入,并将它映射到七段显示输出seg数组中。通过case语句实现对不同BCD码的处理,然后分别赋值给a-g各段驱动信号。

此外,还涉及到硬件描述语言(HDL)的使用,如Verilog中的reg变量表示寄存器,用于存储中间状态;assign语句用于连接信号,将seg数组的相应位置值赋给输出端口。在整个设计流程中,仿真结果验证了译码器的正确工作,并通过分析和优化确保了译码器的性能和可靠性。

总结来说,这篇实验报告详细记录了七段译码器的实现过程,涵盖了从原理理解、逻辑设计、代码编写到实际应用的各个环节,体现了电子设计自动化技术在数字逻辑设计中的应用,为学习者提供了实践EDA工具和技术的良好案例。

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传