FPGA验证入门:从SystemVerilog到UVM实践

下载需积分: 10 | PDF格式 | 860KB |

更新于2024-07-16

| 124 浏览量 | 举报

"该文档是针对FPGA验证的入门教程,详细讲述了uvm验证方法,适合初学者。主要内容包括SystemVerilog语言、UVM、Questasim软件的使用以及批处理脚本,旨在帮助读者理解FPGA验证的基本流程和概念。文档还提供了相关的学习资源推荐。"

在FPGA验证领域,掌握必要的基础知识和技术是非常重要的。这篇文档由西电张冰实验室编写,作者在文中分享了其在FPGA验证领域的学习和经验,主要涵盖了以下几个关键知识点:

1. **SystemVerilog语言**:SystemVerilog是一种强大的硬件描述语言,用于系统级设计和验证。它提供了高级的数据类型、类、接口和并发结构,使得编写复杂的验证环境成为可能。文档中可能只是简单介绍了基础语法和特性,深入学习需要参考如《SystemVerilog与功能验证》等书籍。

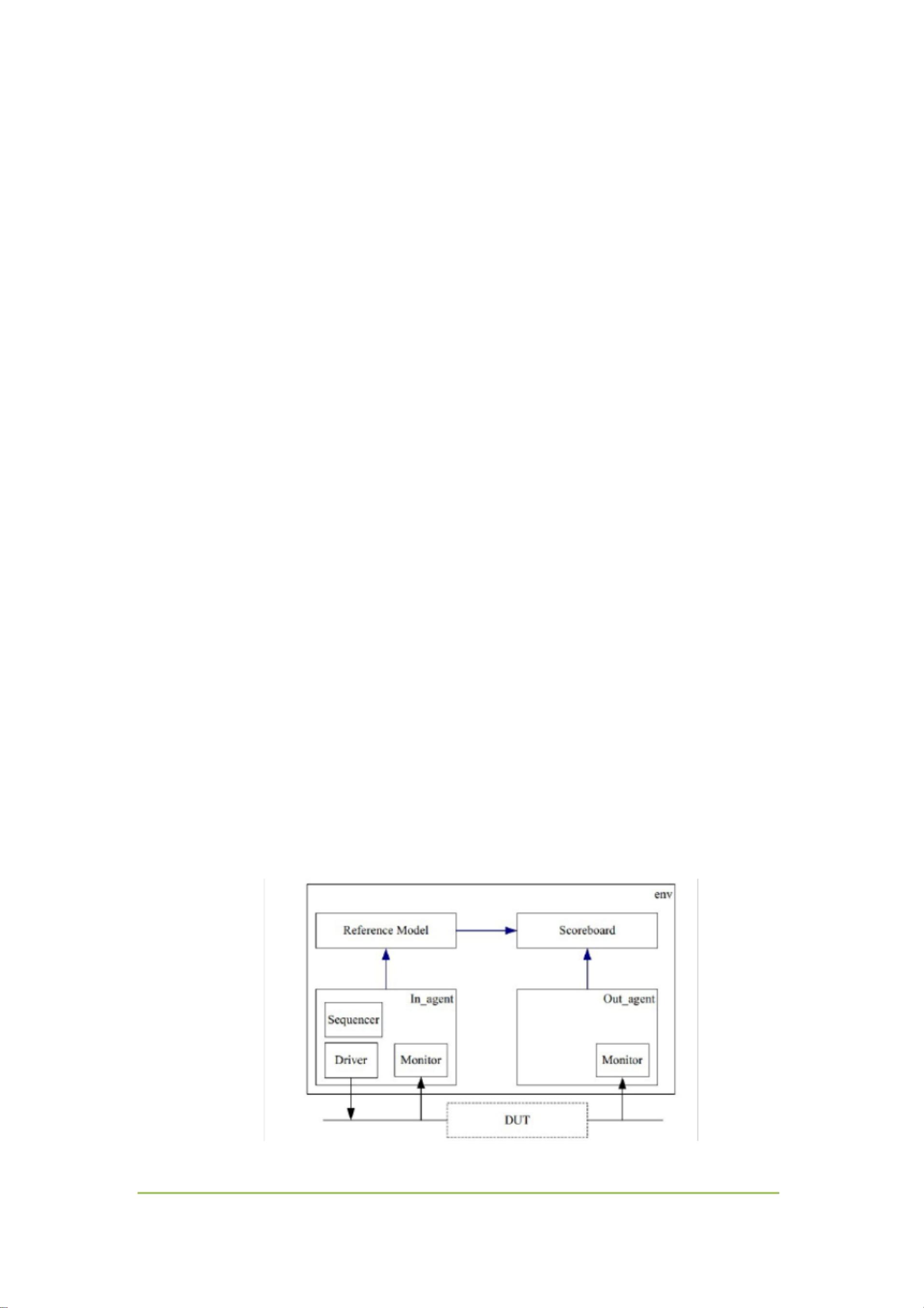

2. **UVM(通用验证方法学)**:UVM是基于SystemVerilog的验证框架,它提供了一套标准的组件库和验证方法,用于创建可复用和可扩展的验证环境。UVM的核心思想是模块化、可配置和可重用性。《UVM1.1应用指南及源码分析》和《UVM_CookBook_2013》是深入学习UVM的好资源。

3. **Questasim软件**:Questasim是 Mentor Graphics 公司的一种高级仿真器,用于硬件设计的模拟和验证。它支持SystemVerilog和其他硬件描述语言,允许开发者在设计周期的早期进行功能验证。文档中会介绍如何使用Questasim进行仿真和调试,但深入掌握可能需要查阅QuestaSim的帮助文档。

4. **批处理脚本**:在FPGA验证过程中,批处理脚本常用于自动化测试平台的构建、编译和运行,提高工作效率。这部分内容可能会介绍如何编写和使用批处理脚本来管理验证流程。

文档适合那些刚刚接触FPGA验证和IC验证的学生,通过阅读,他们可以对FPGA验证的基本流程和工具有一个初步的理解,然后结合其他资料和实践,逐步深入学习。此外,作者还感谢了导师和同行的帮助,体现了学术界的合作精神。

这份文档是FPGA验证学习者的一个良好起点,提供了一个基本的框架和学习路径,后续需要通过更多的实践和学习来不断深化对验证技术的理解。

相关推荐

weixin_45937507

- 粉丝: 0

最新资源

- 山东大学单片机实验教程之LCD 1602显示实验详解

- Dockerized Debian/Ubuntu deb包构建器:一站式解决方案

- 数字五笔:电脑上的手机笔划输入法

- 轻松实现自定义标签输入,Bootstrap-tagsinput组件教程

- Android页面跳转与数据传递的入门示例

- 又拍图片下载器:批量下载相册图片的利器

- 探索《Learning Python》第五版英文原版精髓

- Spring Cloud应用演示:掌握云计算开发

- 如何撰写奖学金申请书的完整指南

- 全面学成管理系统源码:涵盖多技术领域

- LiipContainerWrapperBundle废弃指南:细粒度控制DI注入

- CHM电子书反编译工具:一键还原内容

- 理解PopupWindows回调接口的实现案例

- Osprey网络可视化系统:开源软件平台介绍

- React组件:在谷歌地图上渲染自定义UI

- LiipUrlAutoConverterBundle不再维护:自动转换URL和邮件链接