Xilinx LogiCORE IP Guide: JESD204v6.0 Transceiver for Vivado Des...

需积分: 21 103 浏览量

更新于2024-07-09

收藏 2.04MB PDF 举报

JESD204v6.0是一款针对高速串行数据通信设计的协议,由Xilinx LogiCORE IP产品指南(PG066)详细阐述,适用于Vivado Design Suite。该文档主要关注于JESD204标准,这是一种广泛应用于音频、视频等高带宽接口的标准,如音频接口总线(Audio Interface Bus)。

概述(Chapter 1: Overview)

这部分介绍了传输器和接收器的基本概念。传输器部分详细描述了信号的编码和解码过程,以及如何实现高效的比特流发送。接收器部分则涵盖了采样、时钟恢复、数据解码等关键步骤,确保数据在长距离传输中的准确性。

产品规格(Chapter 2: Product Specification)

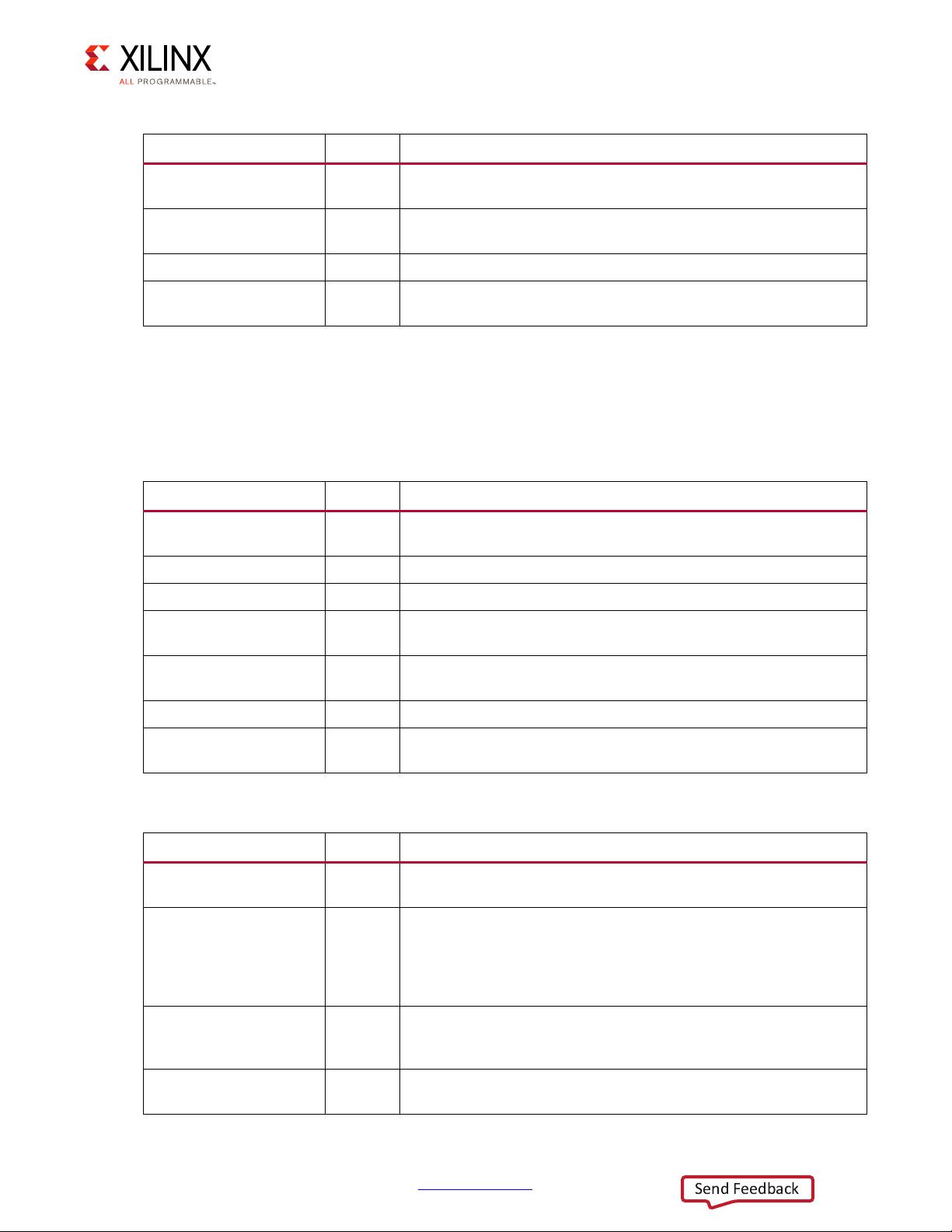

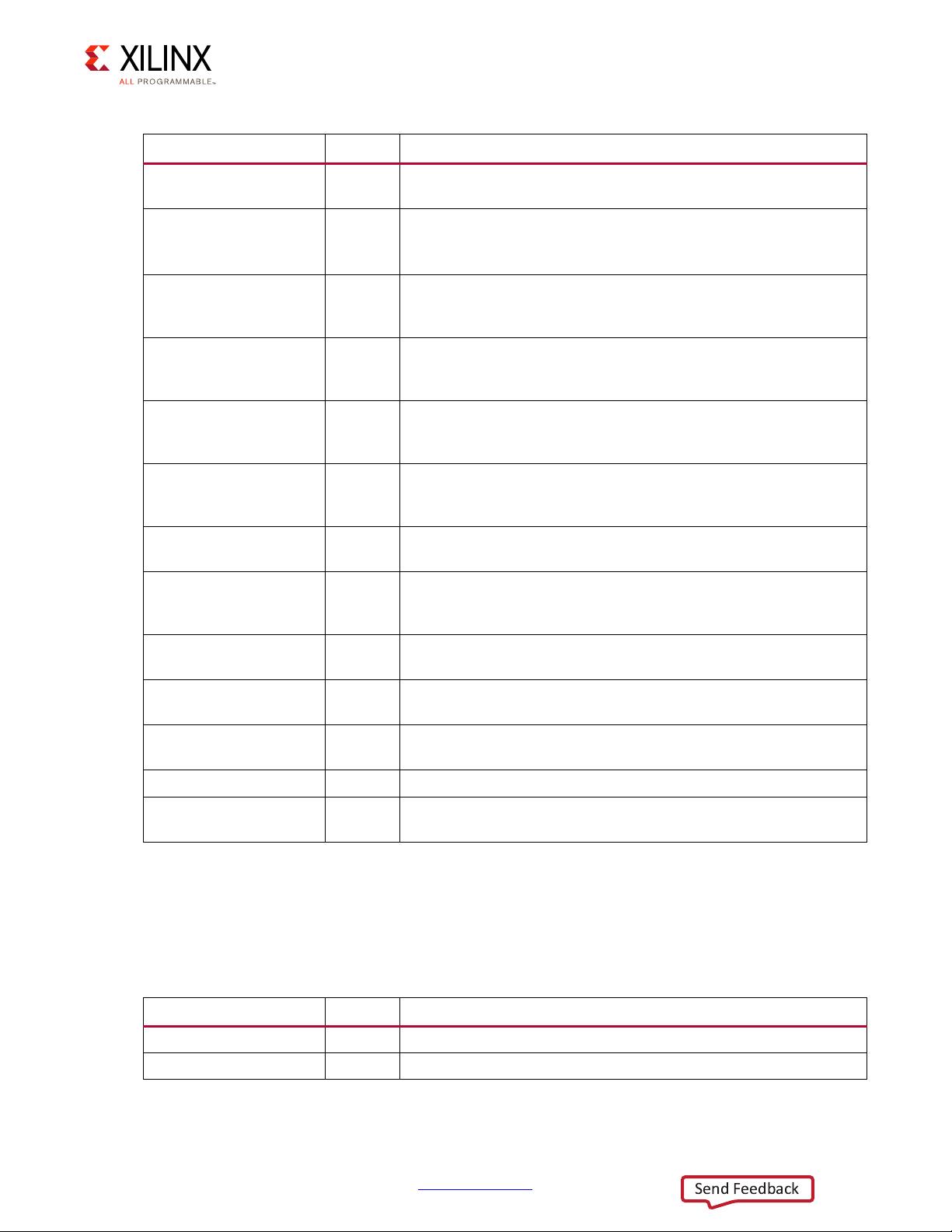

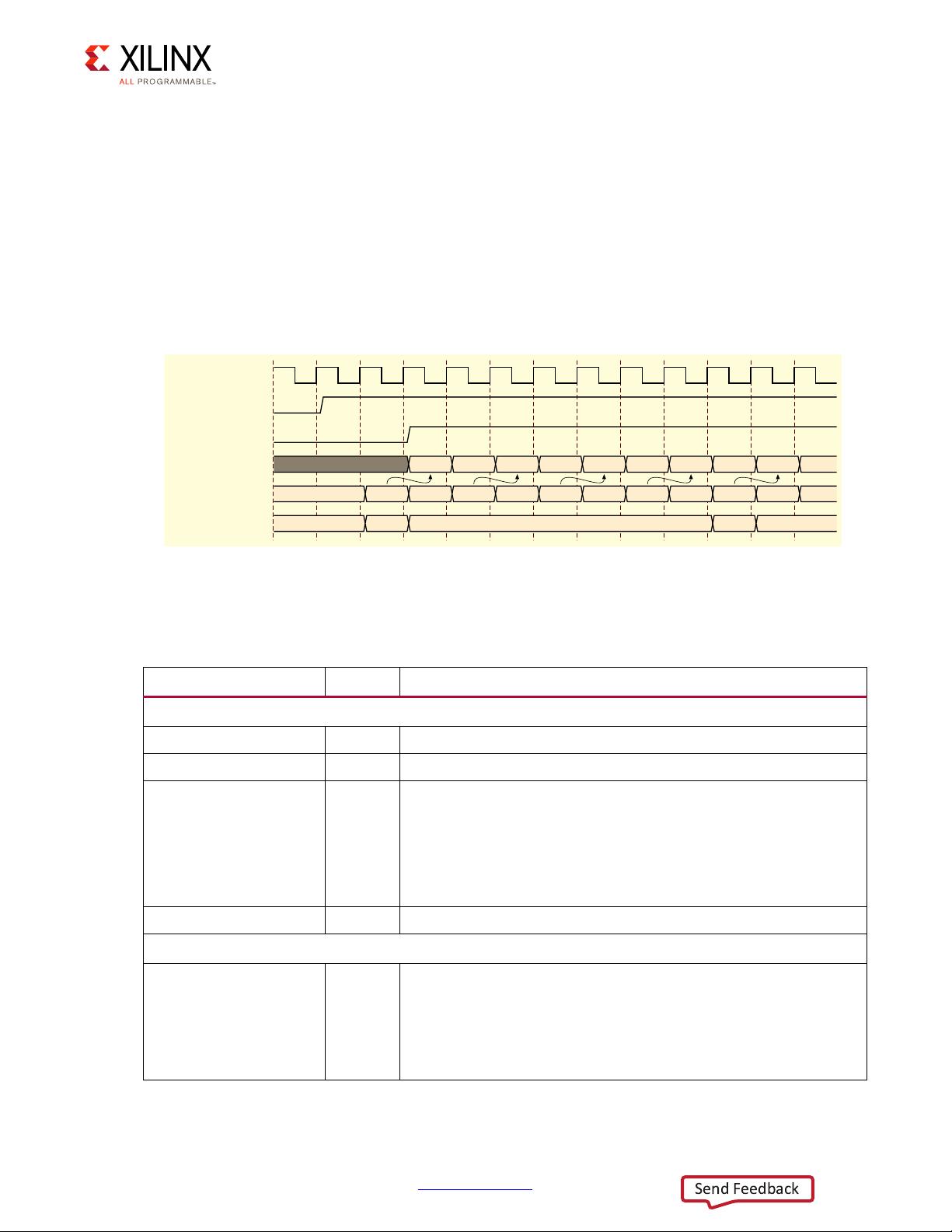

Standards章节列出了JESD204v6.0遵循的具体标准,包括比特率、同步要求等。Resource Utilization部分详述了该IP核心在硬件资源上的占用情况,如逻辑门、时钟资源、内存等。Port Descriptions列出了核心与外部系统交互的主要接口,如AXI4-Stream Data Interface用于数据传输,AXI4-Lite Management Interface则用于配置和控制。

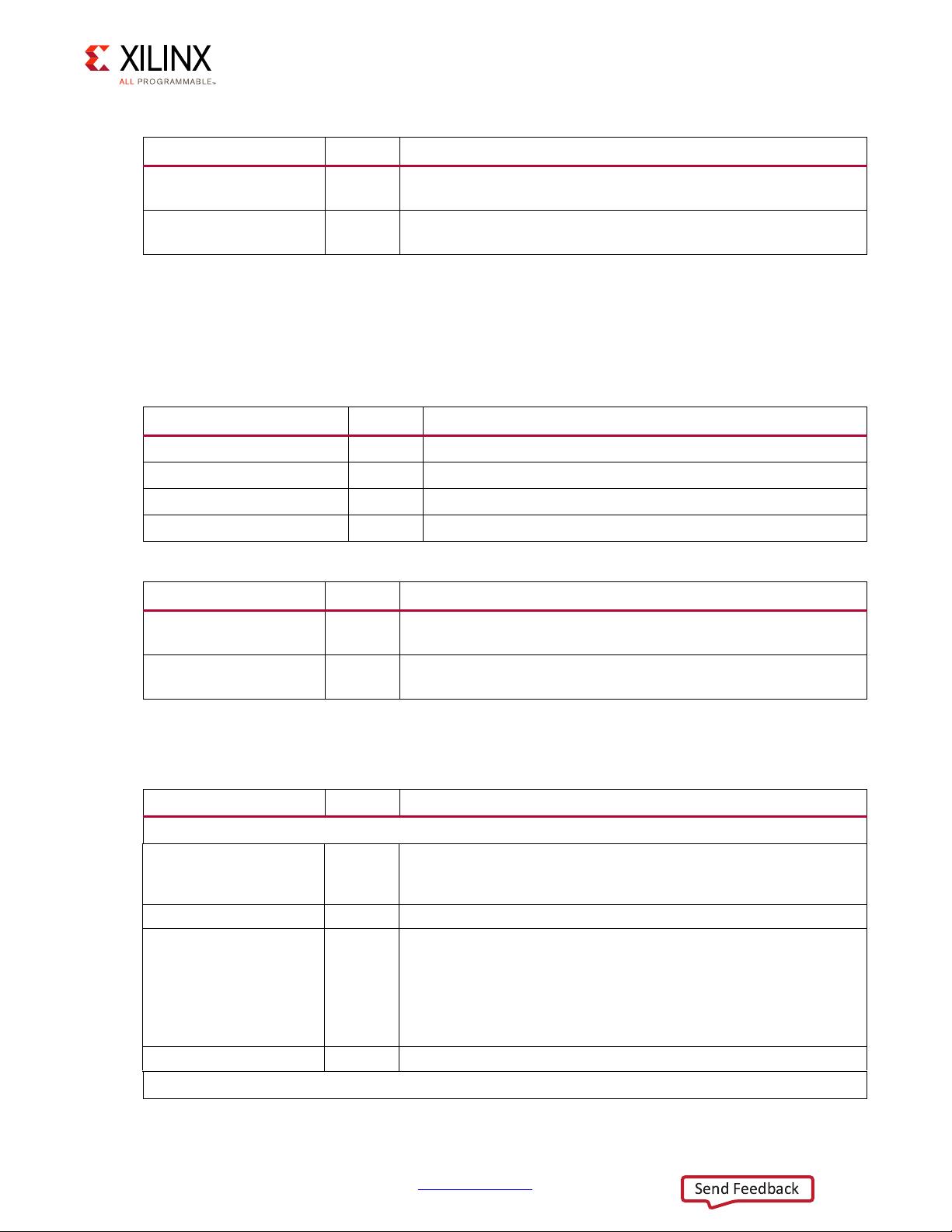

设计流程(Chapter 4: Design Flow Steps)

设计流程从定制和生成核心开始,用户需了解如何调整参数以满足特定应用需求。Constraining the Core部分着重于设置设计约束以优化资源分配。此外,还包括了模拟(Simulation)、综合(Synthesis)和实施(Implementation)等步骤,确保设计能够顺利转化为可编程硬件。

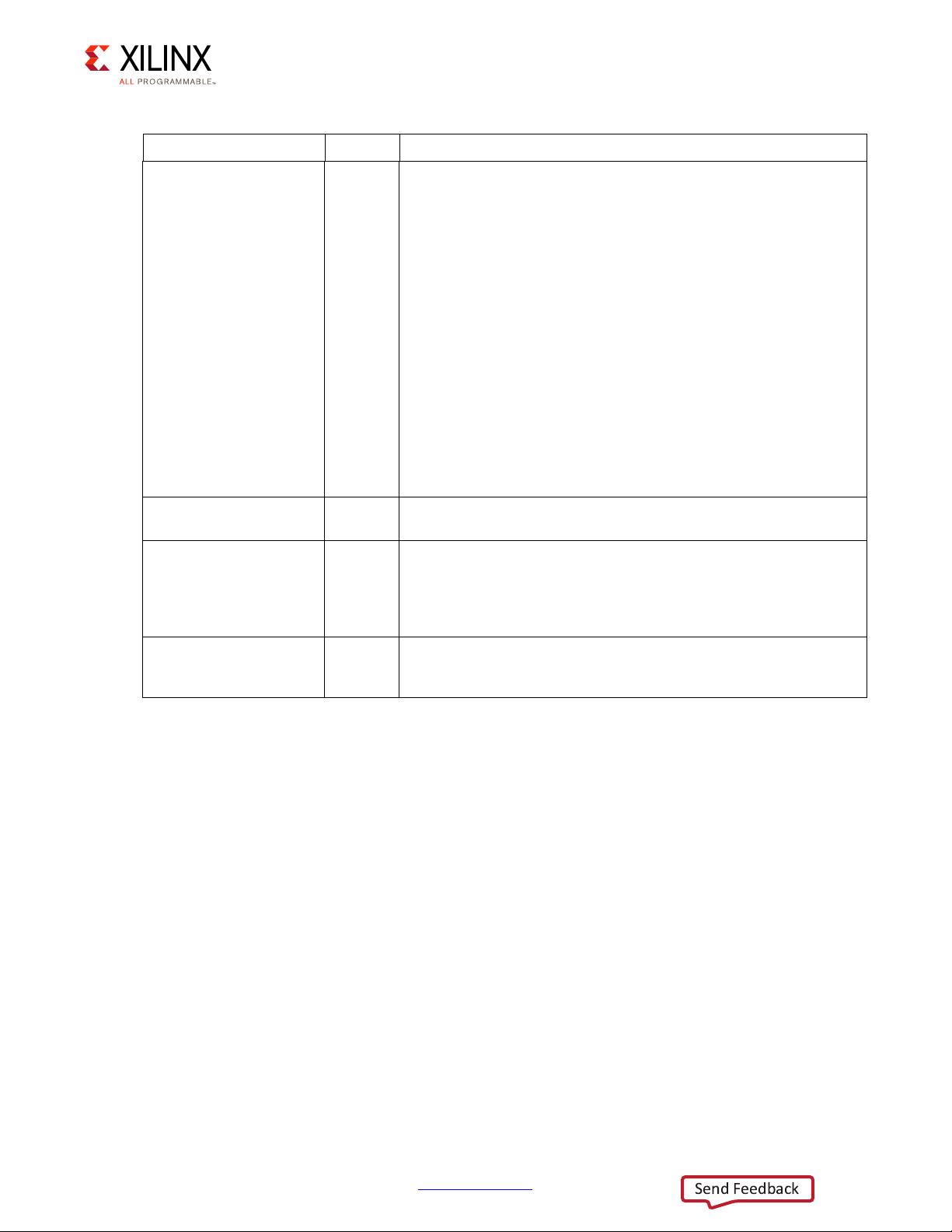

详细设计示例(Chapter 5: Detailed Example Design)

本章提供了一个通用的设计元素集合,展示了如何将JESD204v6.0核心整合到实际项目中,通过实例化和配置,实现完整的系统级设计。

测试平台(Chapter 6: Test Bench)

最后,附录A提供了一个详细的测试bench指南,用于验证核心的正确性和性能,包括单元测试、功能测试和时序测试等,确保JESD204v6.0的可靠性和稳定性。

JESD204v6.0 LogiCORE IP是Vivado Design Suite中用于构建高性能串行通信链路的重要工具,设计师在使用时需理解其工作原理,遵循设计指南,根据应用需求进行定制,并通过测试确保系统的正确运行。这款IP支持Subclass 1和Subclass 2操作模式,适用于多种音频、视频处理场景,同时也允许在发送和接收之间共享传输器资源,提高了硬件效率。

2018-08-06 上传

2019-06-10 上传

2020-03-20 上传

2019-05-18 上传

2019-11-15 上传

2020-02-08 上传

2019-06-06 上传

2023-07-06 上传

2023-07-06 上传

遥远的停止线前

- 粉丝: 17

- 资源: 9

最新资源

- ali-cdn-url:获取阿里云cdn请求地址

- Python3实战Spark大数据分析及调度-第11章 Azkaban实战篇.zip

- 第一个Visual C++应用程序的源码 关于鼠标坐标适时显示

- svelteblox:消费cueblox api的公共网站

- NokiaLCD:诺基亚 5110 LCD 的 AVR 库

- 基于matlab的图像椒盐噪声的平滑效果⽐较

- Latex Documentclass Plan Nacional I+D+i:国家研发计划的LaTeX模板-开源

- Handwritten-Digits-Classification:一种新颖的模型

- VC++ MFC编程实例-新年好

- 6-12-嵌入式省赛.zip

- FriendsFinder:https://enigmatic-taiga-02028.herokuapp.com

- Topic-Constrained-Bodies

- afghanistan-2014-analysis:为我们的阿富汗选举分析托管代码

- hello-world:这是我的第一个仓库

- Webdriver-io-project

- BostonHaskell2015:[Talk] 用 EDSL 构建讨论