FPGA与AD1836实现的I2S接口设计及协议解析

168 浏览量

更新于2024-09-04

收藏 128KB PDF 举报

"EDA/PLD中的基于FPGA和AD1836的I2S接口设计"

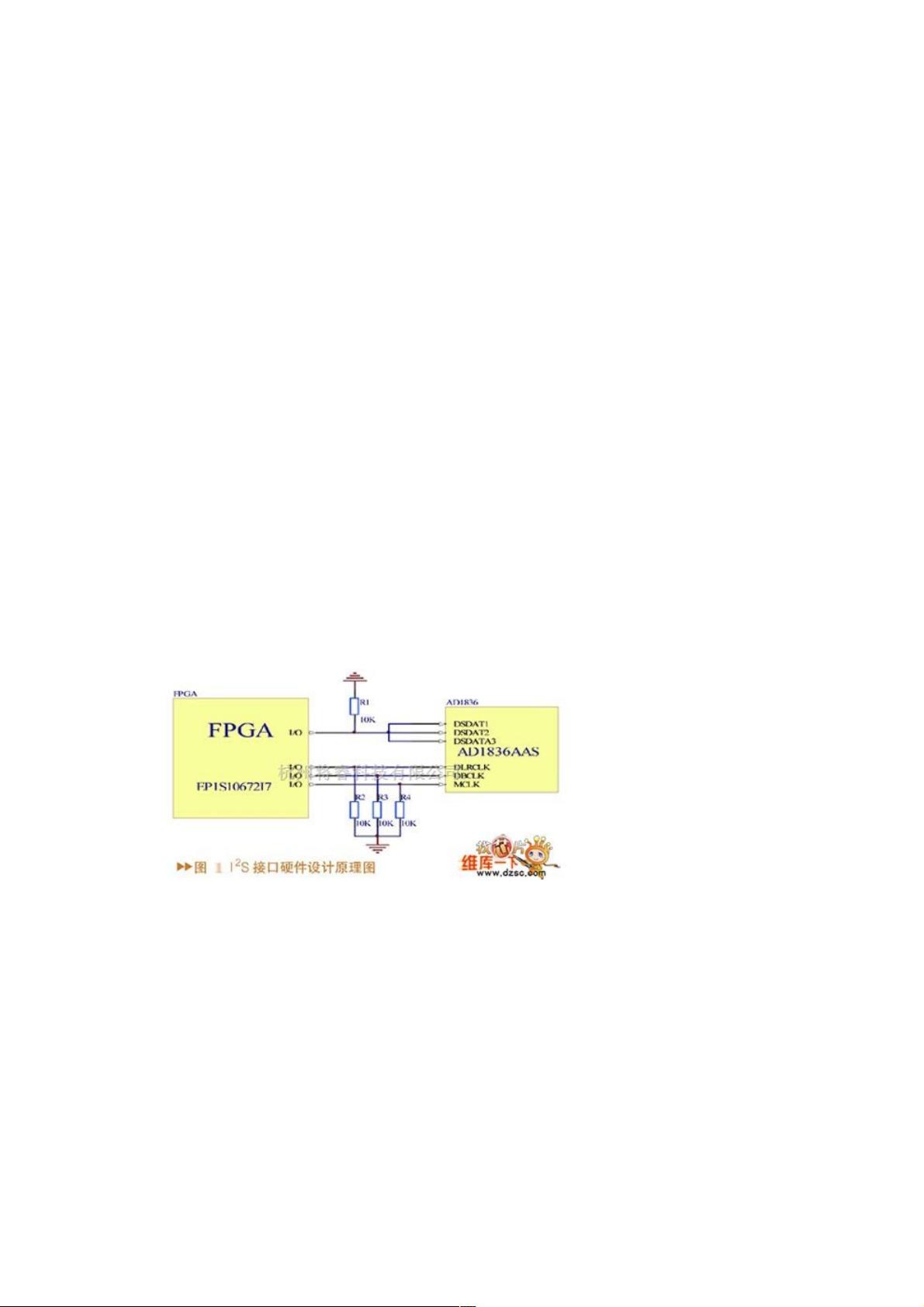

在电子设计自动化(EDA)和可编程逻辑器件(PLD)领域,基于FPGA(Field-Programmable Gate Array)的I2S接口设计是一种常见的应用场景,尤其在数字音频系统中。本文将探讨如何利用FPGA与AD1836 DAC(数字模拟转换器)配合,实现I2S接口,以实现高效的数字音频数据传输。

I2S总线协议是音频系统中的核心组成部分,它定义了设备间传输数字音频数据的标准方式。I2S协议包括三个主要的信号线:

1. **串行时钟BCLK**:位时钟决定了数据传输的速度,它的频率是采样率乘以采样位数的两倍。每个BCLK的脉冲对应音频数据流中的一位。

2. **帧时钟LRCLK**:也称为左右声道选择时钟,用于切换左右声道的数据传输。LRCLK的电平(1或0)指示当前传输的是右声道还是左声道数据,其频率与采样率相同。

3. **串行数据SDATA**:这是实际传输音频样本的线,数据以二进制补码形式表示,按照高位在前低位在后的顺序在BCLK的下降沿更新,并在上升沿被采样。

除了这三个基本信号,有时还会有一个**主时钟MCLK**,它是系统时钟,通常是采样频率的256倍或384倍,确保精确的时钟同步。MCLK提供了高精度的参考时钟源,对整个音频系统的性能至关重要。

在FPGA中实现I2S接口,需要设计合适的逻辑电路来生成并控制这些时钟信号,同时处理SDATA的发送和接收。以Altera的EP1S10672I7为例,这款FPGA具有丰富的逻辑资源和灵活的I/O配置,能够生成所需的BCLK和LRCLK,以及处理SDATA的数据流。

在具体设计中,FPGA需要根据系统需求生成BCLK和LRCLK,这通常通过内部的时钟管理模块实现,可以设置适当的分频系数来得到正确的时钟频率。同时,FPGA还需要包含适当的接收和发送逻辑,确保在BCLK的上升沿稳定地读取和输出数据,并根据LRCLK的翻转来切换左右声道。

与AD1836这样的D/A转换器接口时,FPGA需要正确地驱动I2S信号,确保D/A转换器能接收到正确的数字音频数据流。AD1836是一款高性能的立体声ADC,适用于音频应用,它通常需要与I2S接口配合工作,将数字音频信号转化为模拟信号输出。

在硬件设计中,还需要考虑电源管理、信号完整性以及EMI(电磁干扰)等问题,确保整个系统在物理层面上的可靠运行。例如,FPGA的I/O电压为3.3V,需要与AD1836的接口电压匹配,同时确保信号的传输无误码。

总结来说,基于FPGA的I2S接口设计涉及到I2S协议的理解、时钟生成、数据传输以及与外部设备如AD1836的接口匹配。通过巧妙的逻辑设计和精心的信号处理,可以构建一个高效、低延迟的数字音频处理系统,满足各种音频应用的需求。

532 浏览量

126 浏览量

157 浏览量

149 浏览量

202 浏览量

124 浏览量

145 浏览量