Xilinx Vivado部分重配置教程

需积分: 10 16 浏览量

更新于2024-07-18

1

收藏 5.87MB PDF 举报

"XILIN 重配置文档是Xilinx公司提供的中文版本用户指南UG947,主要关注Vivado设计套件中的部分重配置功能。这份文档适用于2017.1版本,包含了对2017年4月5日更新的内容。文档通过一系列实验,详细介绍了如何在Xilinx的7系列和UltraScale FPGA上进行部分重配置流程,同时也涵盖了Vivado调试、PR项目流程以及部分重配置控制器IP的使用。"

本文档详细阐述了在Xilinx FPGA设计中实施部分重配置的过程,这是现代FPGA设计中一个重要的高级特性。部分重配置允许在FPGA运行时更新或改变其一部分逻辑,而不影响其他正在工作的逻辑,这在很多应用中非常有用,比如动态适应工作负载变化、减少产品版本迭代的成本以及实时错误修复。

文档首先提供了一个概述,介绍了部分重配置的基本概念以及进行这些操作所需的硬件和软件环境。接下来,通过四个实验逐步引导用户熟悉部分重配置流程:

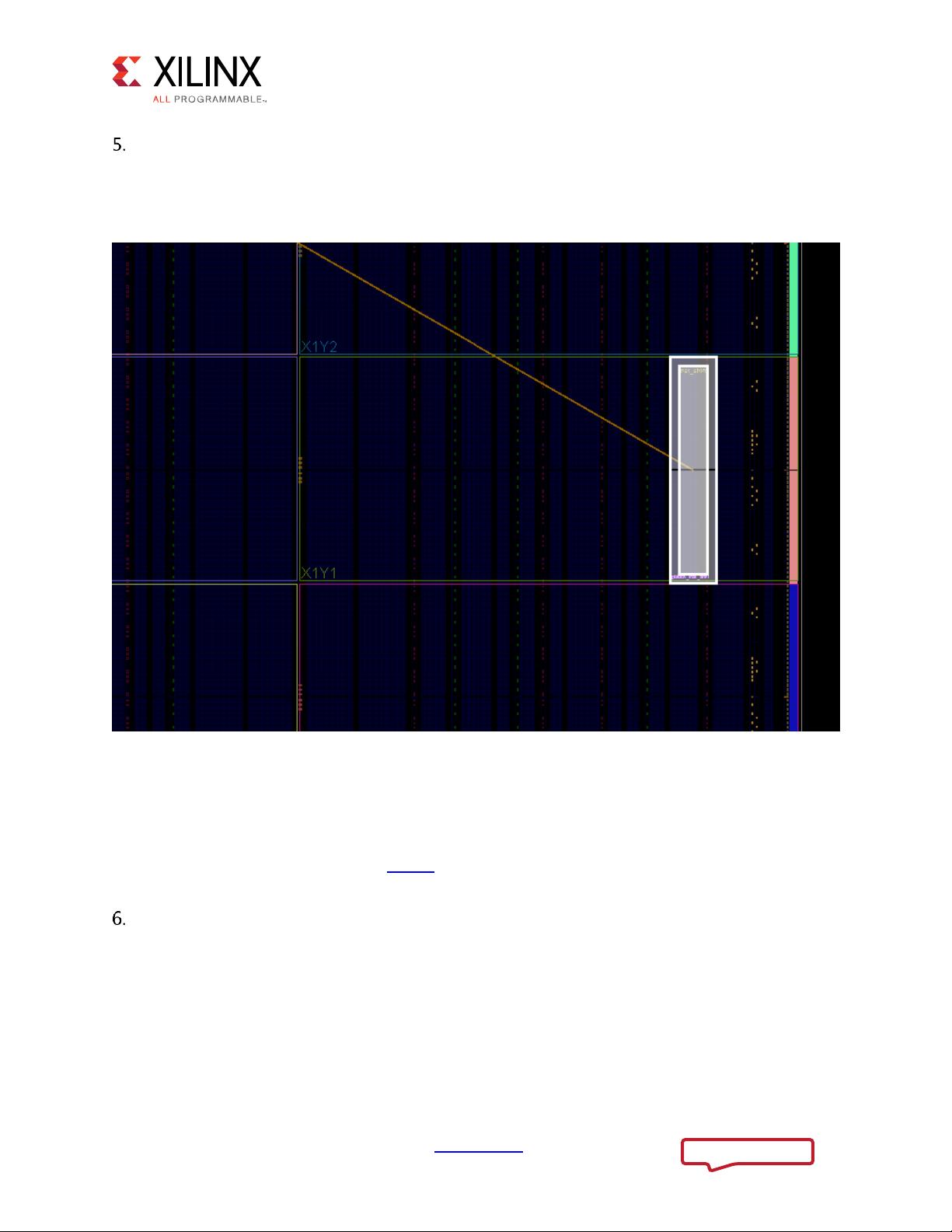

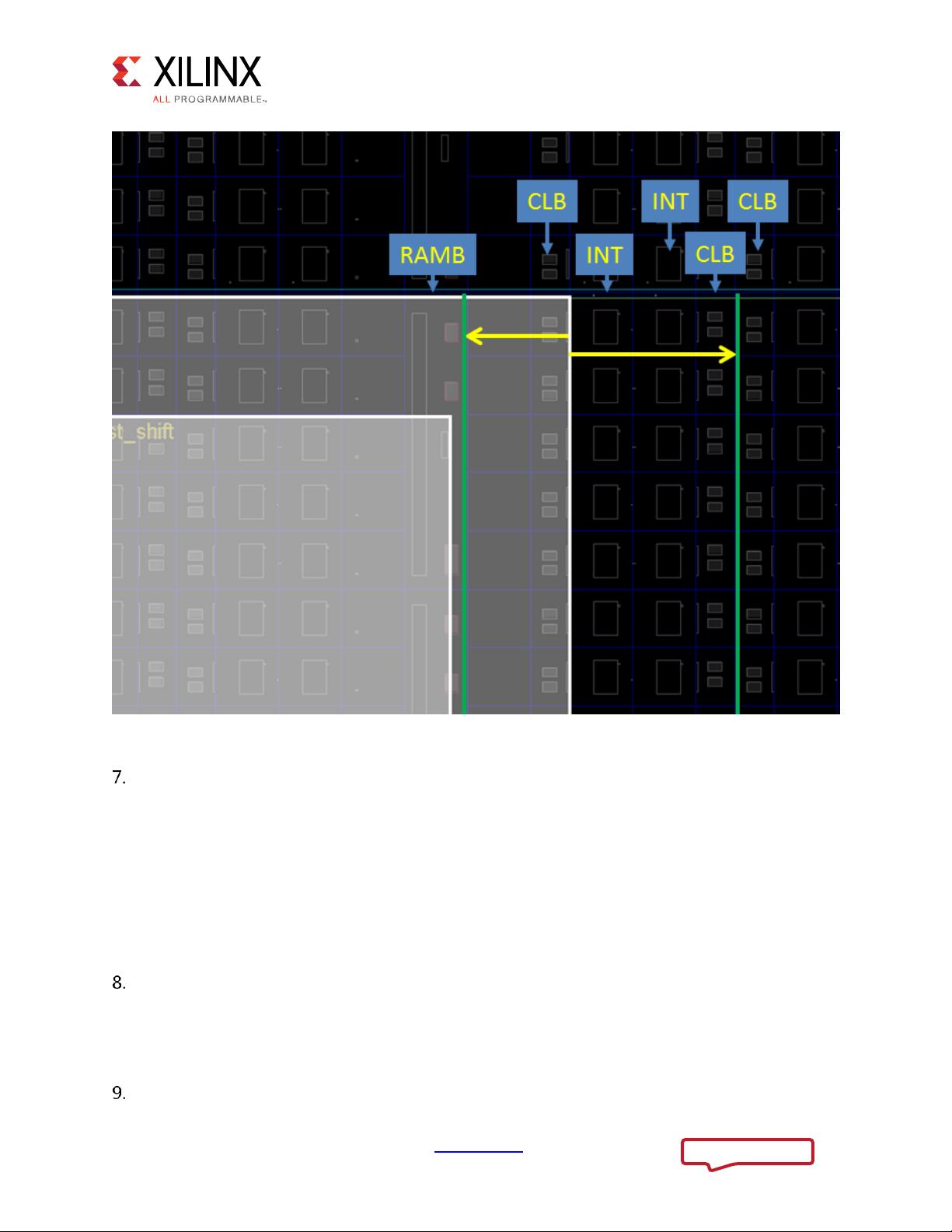

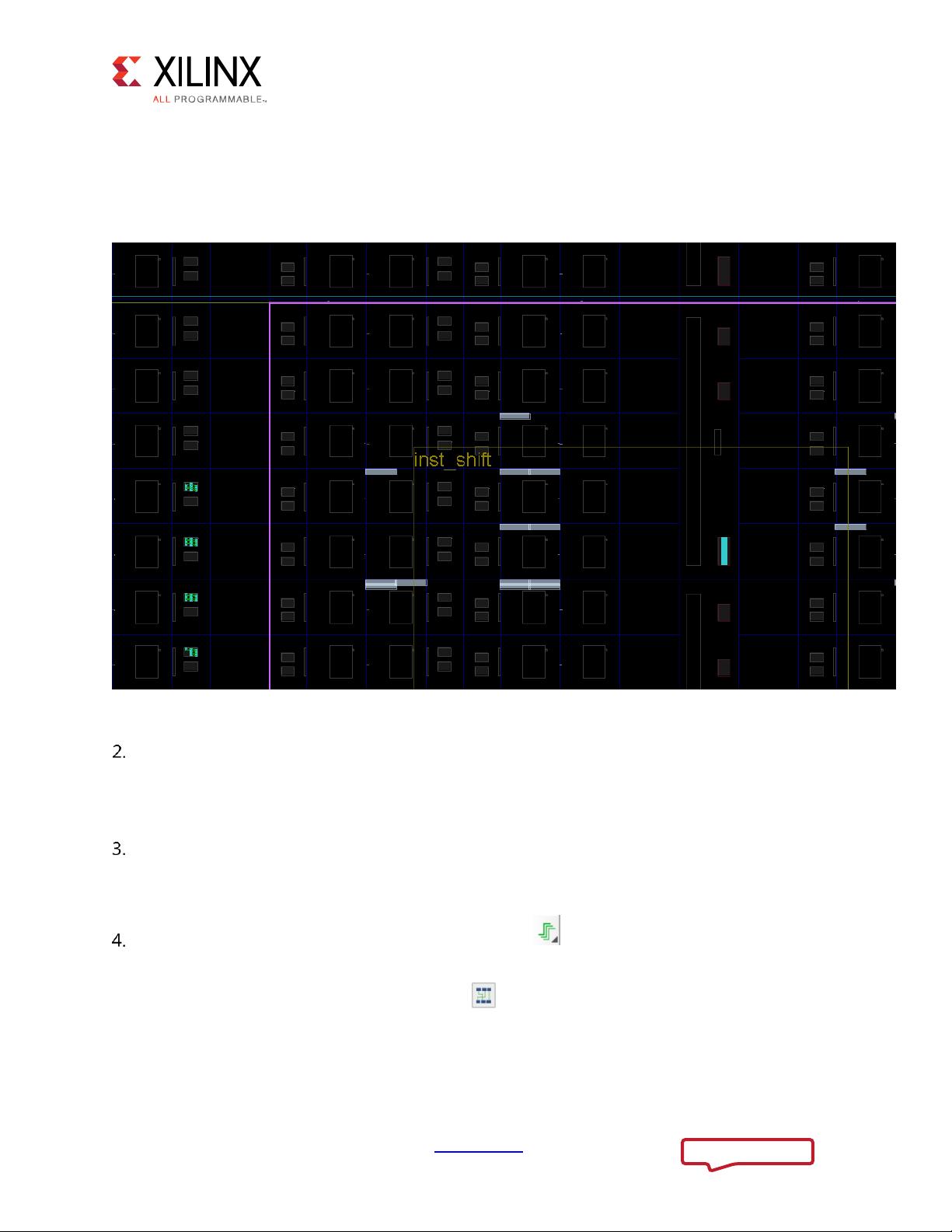

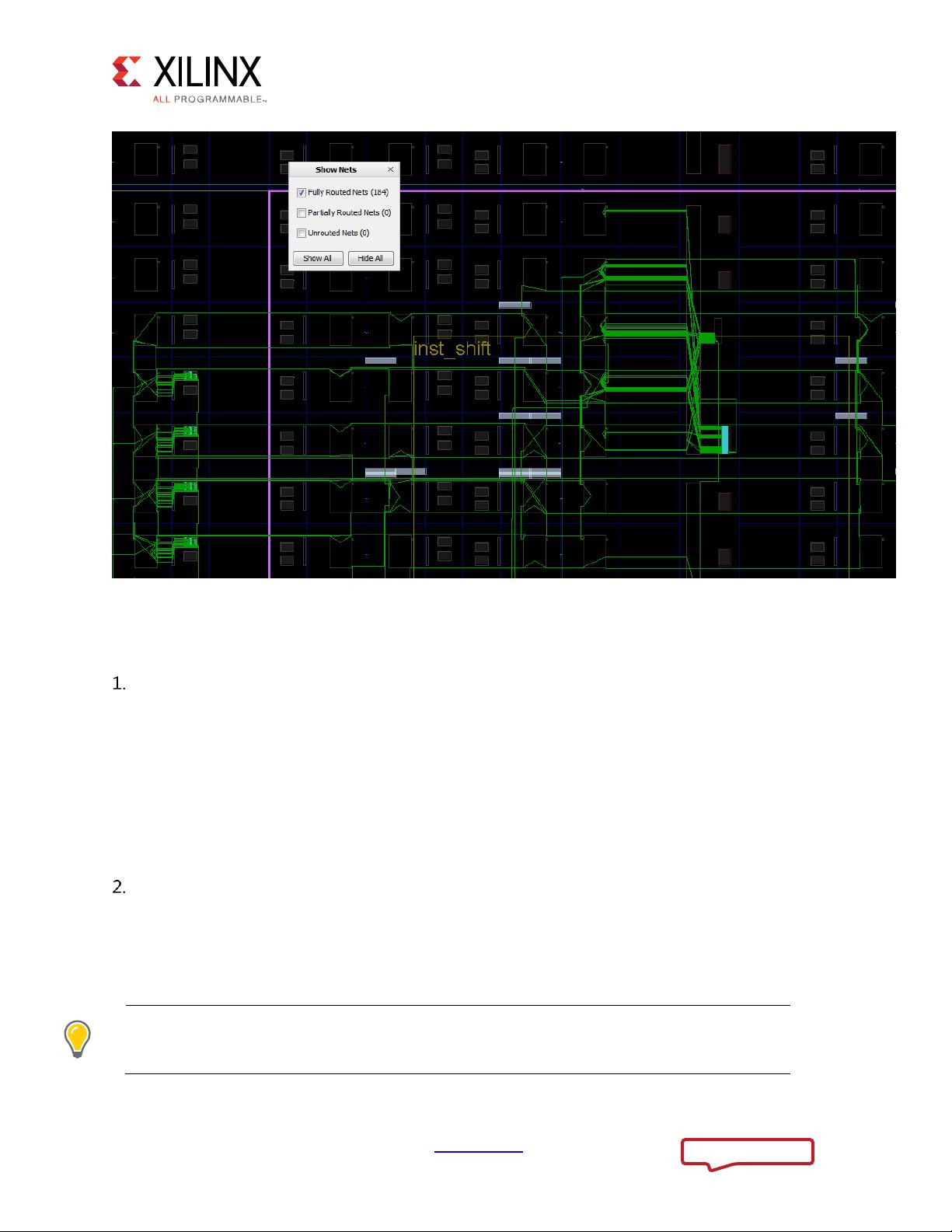

1. 实验1专注于7系列FPGA的基础部分重配置流程,包括解压设计文件、检查和运行脚本、合成、组装、实现、布局布线以及生成和应用位流。

2. 实验2则针对UltraScale FPGA,步骤与实验1类似,但考虑到 UltraScale 架构的特性,可能包含更复杂的配置流程和优化。

3. 实验3深入到部分重配置项目流程,讲解如何建立和管理设计结构,以及如何在设计中迭代部分重配置。

4. 实验4涵盖Vivado调试工具的使用,以及如何在调试过程中集成部分重配置,这对于复杂系统的设计验证至关重要。

5. 实验5专门讨论7系列器件的部分重配置控制器IP,包括定制IP、编译设计、设置板级支持包以及验证IP功能。

每个实验都提供了详细的步骤,确保用户能够逐步理解并实践部分重配置技术。文档还鼓励用户通过提供的反馈机制提出问题和建议,以帮助不断改进和更新文档内容。

总体来说,"XILIN 重配置文档"是学习和掌握Xilinx FPGA部分重配置技术的重要参考资料,对于进行复杂、灵活的FPGA设计的工程师和研究人员而言,具有很高的价值。通过这个文档,读者可以深入了解部分重配置的原理和实践,从而在实际项目中有效利用这一功能。

2021-09-29 上传

2014-10-17 上传

2019-12-16 上传

2019-04-28 上传

2019-09-20 上传

yyysfgf

- 粉丝: 0

- 资源: 4

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能