FPGA实现DDS:相位累加器与正弦查找表设计

7 浏览量

更新于2024-08-31

收藏 664KB PDF 举报

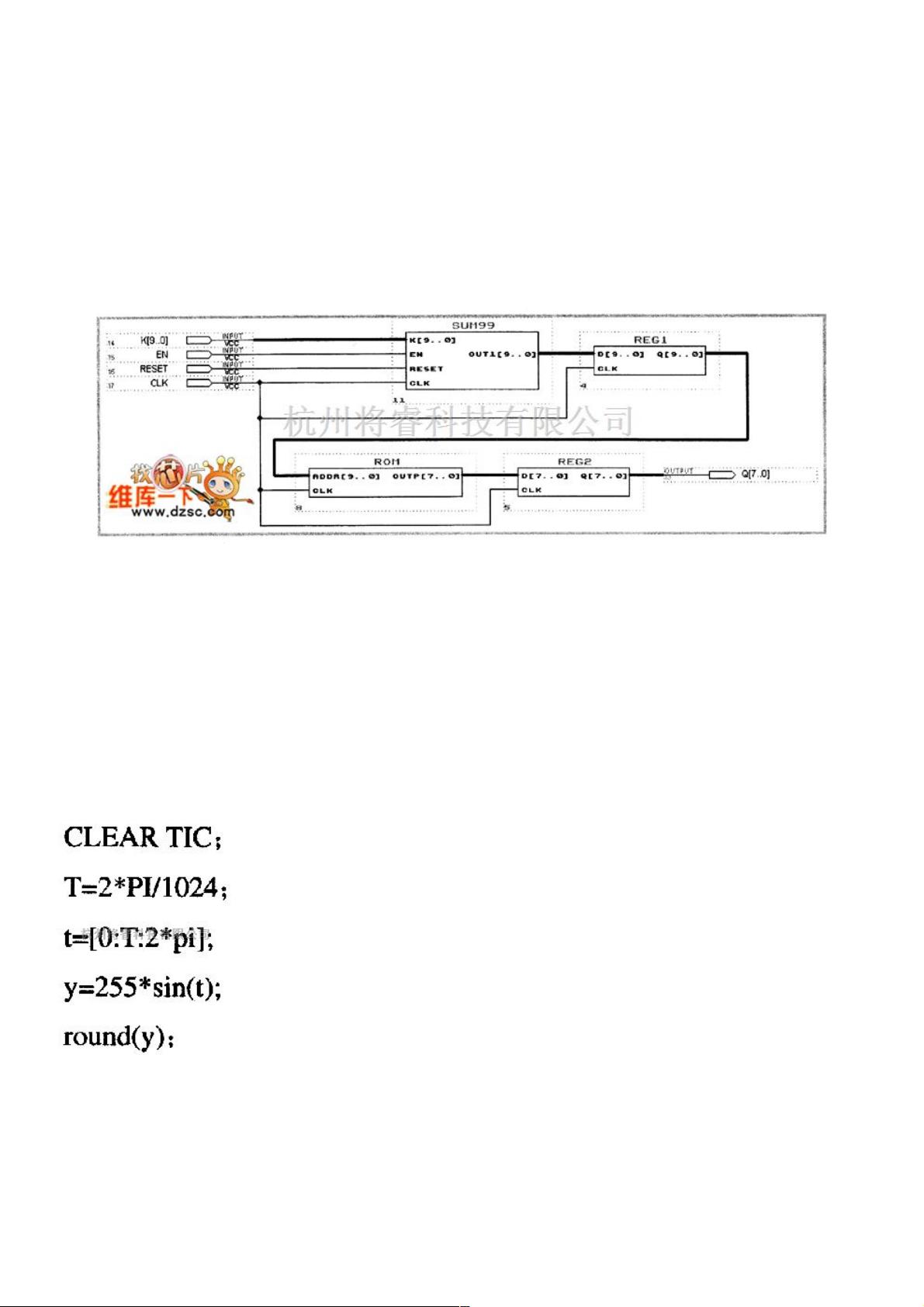

"EDA/PLD中的DDS的FPGA实现设计主要涵盖了相位累加器、相位寄存器、正弦查找表ROM和输出数据寄存器等关键模块的构建,以及如何在FPGA上实现DDS的核心功能。设计中,DDS模块通过单一时钟信号同步各个部分的运算,确保系统的稳定性和精度。"

在数字信号处理领域,DDS(直接数字频率合成)是一种高效的方法,用于生成高精度的模拟波形。在FPGA(现场可编程门阵列)中实现DDS可以灵活地调整频率,且具有高速和低延迟的优点。该设计主要围绕四个核心组件展开:

1. **相位累加器SUM99**:这是DDS的心脏,通常是一个高速加法器。在本设计中,它是一个10位的累加器,使用频率控制字Κ(K)作为增量,每次时钟脉冲到来时,相位累加器都会增加这个值。当相位累加器的和达到其最大值(即溢出)时,它会重置为零,从而形成周期性变化的相位。

2. **相位寄存器REG1**:这是一个简单的10位寄存器,用于存储相位累加器的当前输出。每当新的时钟信号到来,寄存器会更新其状态,输出当前的相位值。

3. **正弦查找表ROM**:这部分是DDS的关键,它存储了预先计算好的正弦函数采样点。通过地址线(与相位寄存器的输出相关联)访问ROM,可以获取对应的正弦值。由于实际应用中可能需要更高的精度,正弦查找表通常需要较大的存储空间,例如本设计中的1024个采样点,对应10位地址。每个地址对应9位的输出数据,以提供足够的分辨率。

4. **输出数据寄存器REG2**:ROM的输出在被送至外部之前,会被暂存在这里,确保在下一个时钟周期稳定后再输出,提高输出信号的质量。

在设计过程中,正弦查找表的创建通常通过数学软件如MATLAB或编程语言如C来完成。采样点的选择和转换成二进制数据后,这些数据会被编程到FPGA中的查找表内存中。在实际运行时,DDS模块根据时钟信号,依次读取并输出ROM中的正弦样本值,生成连续的模拟波形。

这种EDA/PLD中的DDS实现设计展示了如何利用FPGA的并行处理能力,快速生成所需频率的正弦波形。通过精心设计和优化,可以在满足性能需求的同时,有效地利用硬件资源。

164 浏览量

114 浏览量

2020-11-11 上传

141 浏览量

124 浏览量

135 浏览量

130 浏览量

161 浏览量

683 浏览量

weixin_38627590

- 粉丝: 13

- 资源: 919

最新资源

- 节点层

- ROS-for-Covid-Application

- Java打砖块儿游戏代码

- 连锁特许经营知识培训(5)DOC

- optee-rs:专为optee设计的防锈漆

- streamify-app

- 初级java笔试题-Interview:让我们学习那些白板

- 罗莱专卖店经营成功案例分析培训DOC

- 易语言源码易语言例程更新自身防误报.rar

- 霍夫曼编码:Python中的School项目

- java笔试题算法-topictiling:TopicTiling是一种基于LDA的文本切分方法

- Công Cụ Đặt Hàng Đặt Hàng Đà Nẵng-crx插件

- mjwedding:WordPress主题婚礼

- 易语言源码易语言使系统控制菜单失效源码.rar

- url:解析,构建和处理URL

- 营业厅课程培训——营业厅现场管理