Altera FPGA仿真实现:ModelSim, Synplify, Quartus全流程

108 浏览量

更新于2024-08-31

收藏 983KB PDF 举报

"该资源介绍了如何使用ModelSim+Synplify+Quartus的组合来实现Altera FPGA的仿真实现流程,包括功能仿真、综合、布局布线和后仿真等关键步骤。"

在Altera FPGA的设计流程中,通常会采用一系列专业工具协同工作以完成从设计到验证的全过程。本资源主要涉及了以下四个关键知识点:

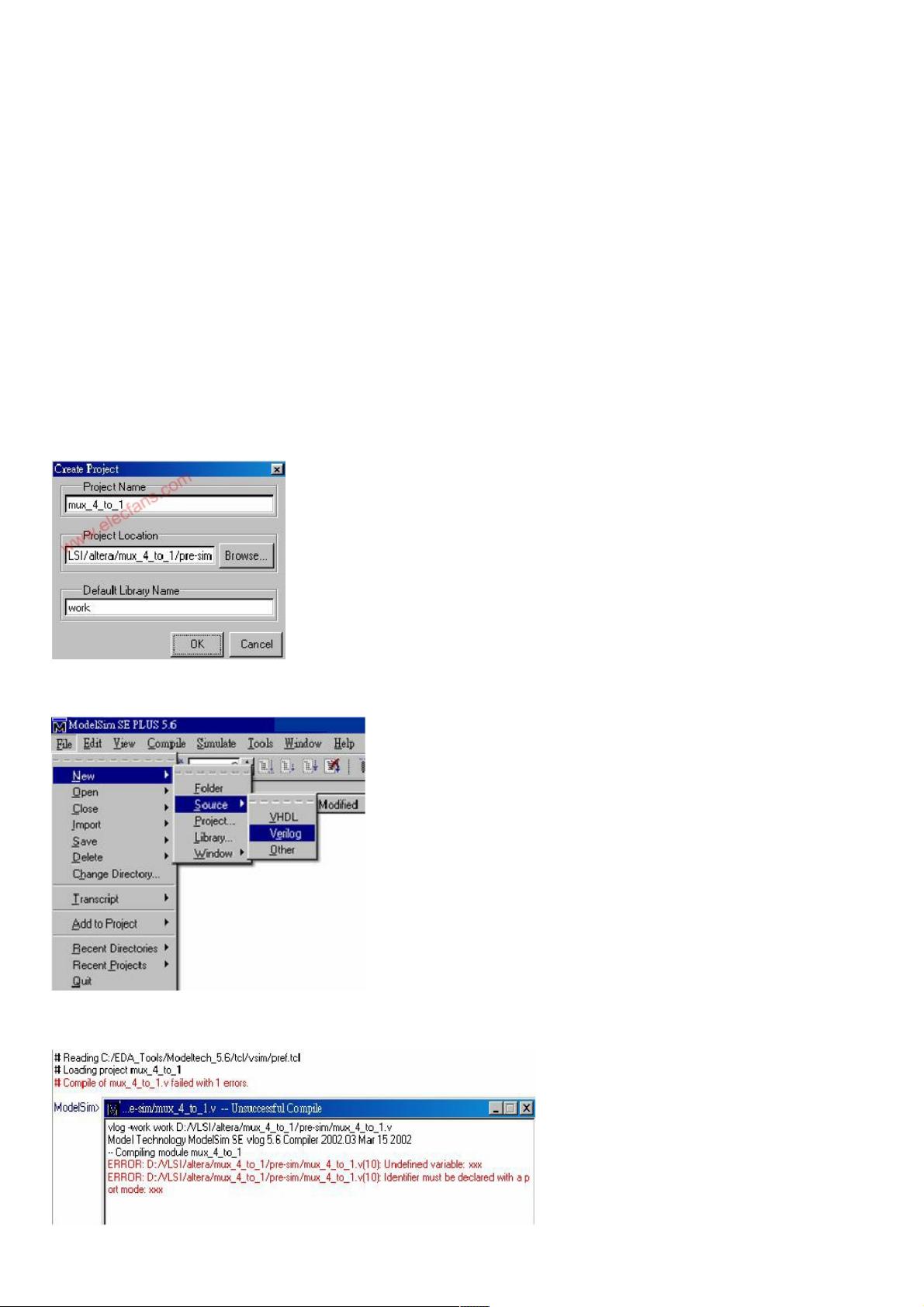

1. **功能仿真 (Function Simulation)**: 使用ModelSimSE作为仿真器进行设计验证。在设计阶段,首先创建一个多路选择器的Verilog代码,然后在ModelSimSE中建立项目,添加设计文件并进行编译。接着,编写测试平台(Testbench)以模拟输入和预期输出,通过运行仿真来观察设计在不同条件下的行为,确保设计功能的正确性。

2. **综合 (Synthesis)**: 用Synplify Pro工具对Verilog代码进行综合。这个过程将高级语言描述的逻辑转化为门级网表(Netlist),生成的.vqm文件包含了硬件实现的逻辑表示。Synplify Pro优化设计,减少逻辑资源的使用,提高速度或功耗性能。

3. **布局布线 (Place and Route)**: 将Synplify Pro生成的.vqm文件导入到Quartus II中,Quartus II会自动进行布局布线。布局是将设计中的逻辑单元分配到FPGA的具体位置,布线则是连接这些逻辑单元,形成实际的物理连接。最终,Quartus II会生成一个包含了具体实现信息的.verilog文件(如xxx.vo)。

4. **后仿真 (Post-Simulation)**: 在布局布线后,再次使用ModelSimSE进行仿真,称为后仿真。这次仿真验证的是经过综合和布局布线后的设计,可以更准确地反映出实际硬件的行为。这一步至关重要,因为布局布线可能会影响设计的性能,如时序和功耗。通过比较前仿真和后仿真的结果,可以确认设计在硬件实现后是否满足预期要求。

在整个流程中,**仿真器** (如ModelSimSE) 主要用于验证逻辑设计,确保设计在概念上的正确性;**综合工具** (如Synplify Pro) 负责将高级语言代码转化为硬件可实现的逻辑;而**集成开发环境** (如Quartus II) 则提供了从综合到实现的完整解决方案,包括自动布局布线。通过这样的流程,设计师能够确保FPGA设计不仅在理论上可行,而且在实际硬件上也能正常工作。

2021-10-02 上传

2020-10-18 上传

2022-01-31 上传

2012-04-06 上传

2010-12-14 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-05-14 上传

weixin_38673812

- 粉丝: 4

- 资源: 904

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南