ARM嵌入式最小系统软硬件架构优化研究

下载需积分: 9 | PDF格式 | 335KB |

更新于2024-09-06

| 117 浏览量 | 举报

本文主要探讨了ARM嵌入式最小系统的软硬件架构改进研究。随着嵌入式技术的快速发展,设计满足特定需求的嵌入式最小系统变得尤为重要。ARM处理器由于其广泛的应用和通用的外围电路特性,成为嵌入式设计中的首选。

首先,引言部分强调了当前嵌入式系统开发中存在的一种倾向,即过度关注处理器与外设的连接以及应用代码开发,而忽视了对基础架构的研究。文章着重指出,对ARM嵌入式最小系统的研究,尤其是软硬件架构,对于整个系统开发的效率和稳定性具有关键作用。

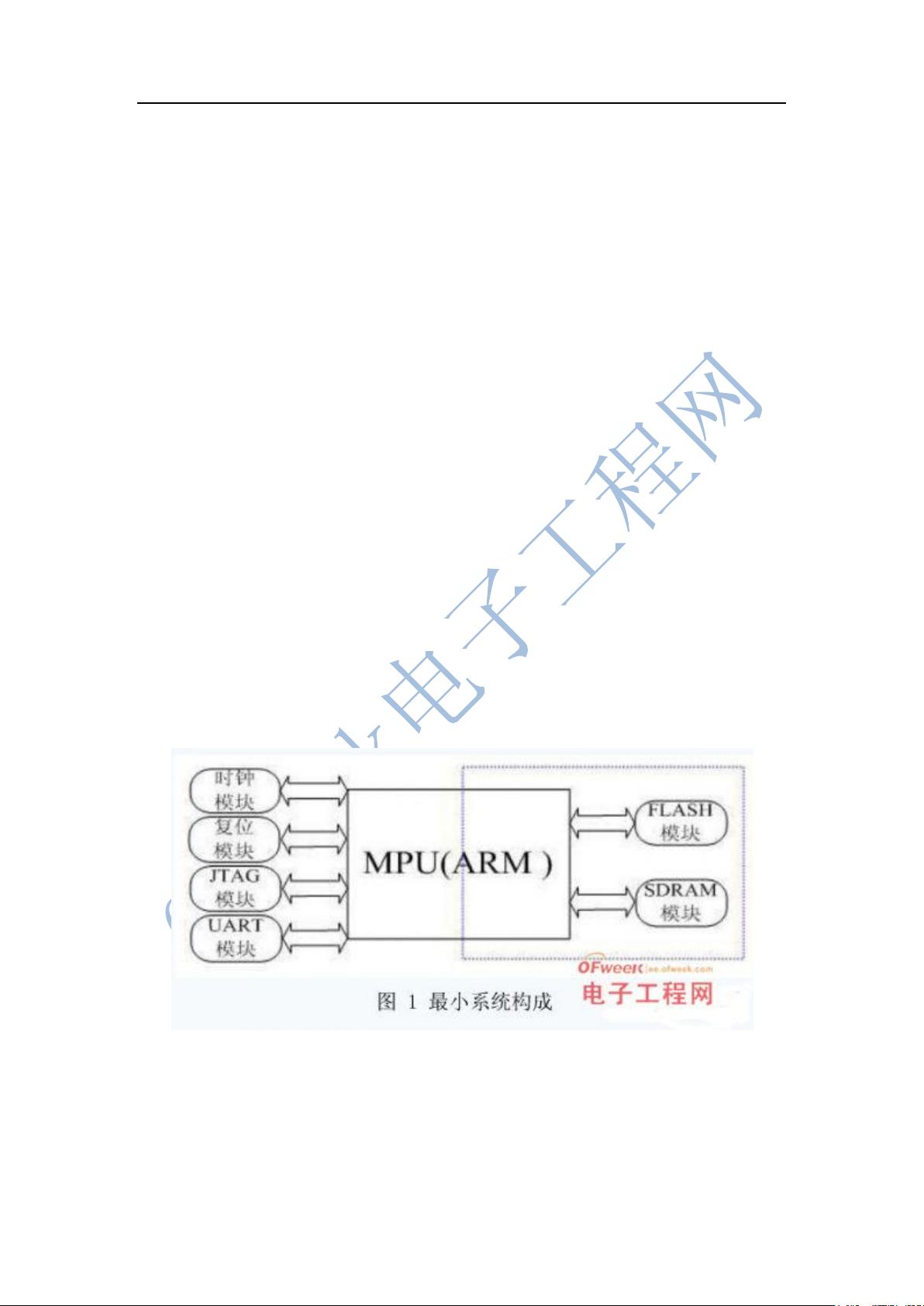

嵌入式最小系统的核心目标是实现最小化的模块配置,以支持基本功能的运行。在基于ARM的最小系统中,主要包括ARM微处理器、Flash存储器(用于存放启动代码、操作系统和应用程序)、SDRAM作为动态存储空间、JTAG模块用于程序下载和调试、UART模块用于终端显示和复位模块来重启系统。这些组件协同工作,确保系统的基本功能得以实现。

硬件设计中的关键技术环节是ARM处理器与外存储器(如NorFlash和NandFlash)的接口。NorFlash以其较快的读取速度和较高的写入速度适用于代码存储,而NandFlash则因容量大、成本低更适合大规模数据存储。选择合适的接口方式能显著提升系统的存储性能和可靠性。

本文接下来会深入研究这些接口技术的具体实现,包括可能采用的接口协议(如SPI、I2C或AHB/AHB Lite),以及优化存储器访问速度和降低功耗的方法。此外,还会讨论如何通过硬件层面的改进,如引入硬件加速器或者使用低功耗模式,进一步优化嵌入式系统的整体性能。

软件方面,文章将详细剖析嵌入式最小系统的启动架构,包括引导加载程序的执行流程、内存管理、以及如何确保操作系统和其他应用程序的正确初始化。这部分内容会涉及如何设计高效的启动流程,如何利用中断处理机制,以及如何优化代码的执行效率。

总结来说,本文通过对ARM嵌入式最小系统软硬件架构的深入研究,旨在提供一种更为高效、稳定和灵活的设计方法,以适应不断变化的嵌入式应用需求。通过优化硬件接口和软件启动机制,本文的工作有望推动嵌入式系统的整体性能提升和技术进步。

相关推荐

weixin_38743481

- 粉丝: 698

最新资源

- 支付宝订单监控免签工具:实时监控与信息通知

- 一键永久删除QQ空间说说的绿色软件

- Appleseeds训练营第4周JavaScript练习

- 免费HTML转CHM工具:将网页文档化简成章

- 奇热剧集站SEO优化模板下载

- Python xlrd库:实用指南与Excel文件读取

- Genegraph:通过GraphQL API使用Apache Jena展示RDF基因数据

- CRRedist2008与CRRedist2005压缩包文件对比分析

- SDB交流伺服驱动系统选型指南与性能解析

- Android平台简易PDF阅读器的实现与应用

- Mybatis实现数据库物理分页的插件源码解析

- Docker Swarm实例解析与操作指南

- iOS平台GTMBase64文件的使用及解密

- 实现jQuery自定义右键菜单的代码示例

- PDF处理必备:掌握pdfbox与fontbox jar包

- Java推箱子游戏完整源代码分享