Hi3519AV100 DDR4x16飞越信号完整性报告:DQ写突发眼图分析

需积分: 10 147 浏览量

更新于2024-07-10

收藏 7.79MB PDF 举报

本报告是关于Hi3519AV100 DDR4x16 Flyby Signal Integrity (信号完整性)的测试总结,日期为2018年8月21日。测试依据的是DDR4 2666Mbps AC100标准,并强调所有数据仅限于HiSilicon测试样本,供参考,不代替客户自身的测试。

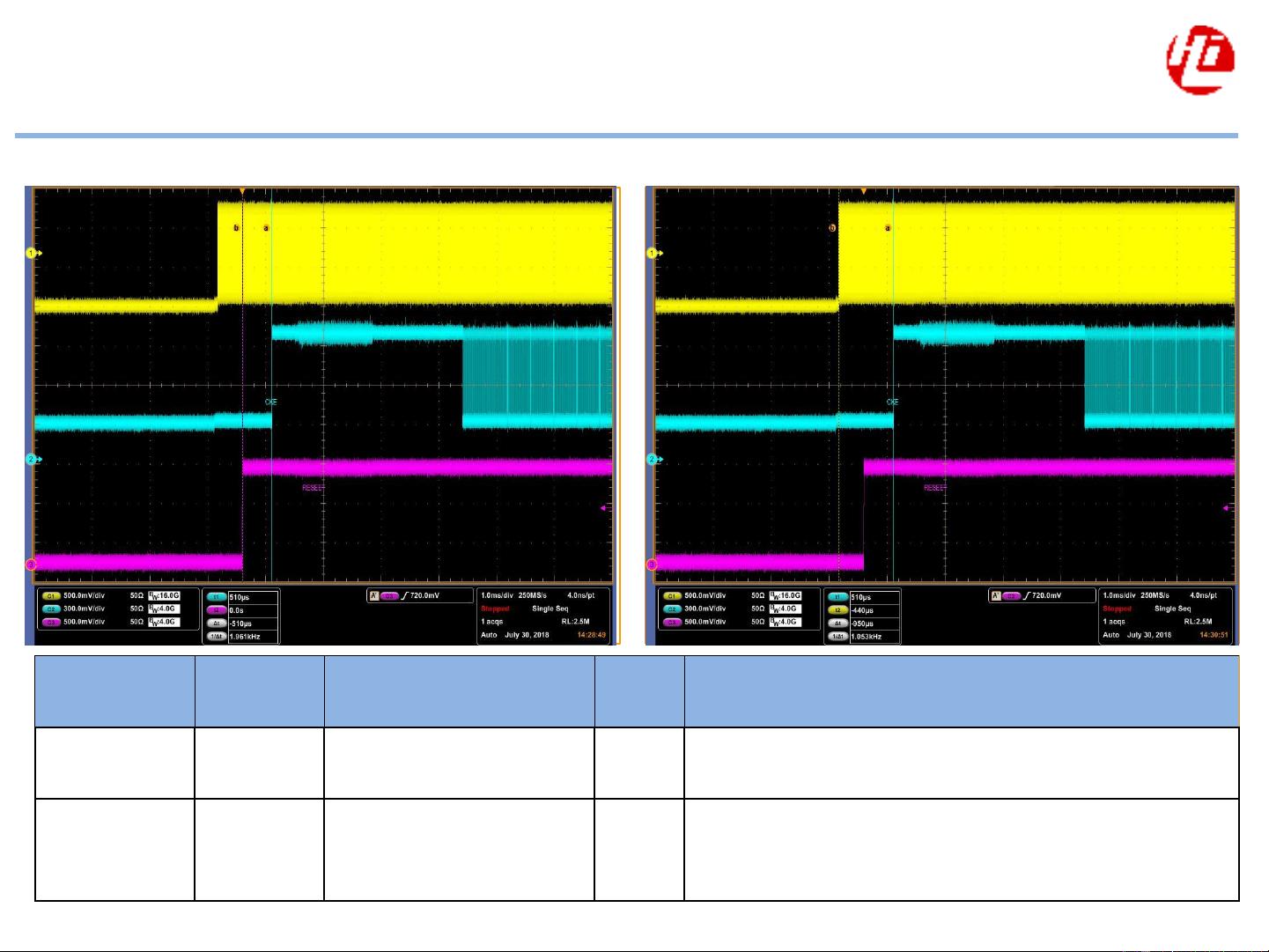

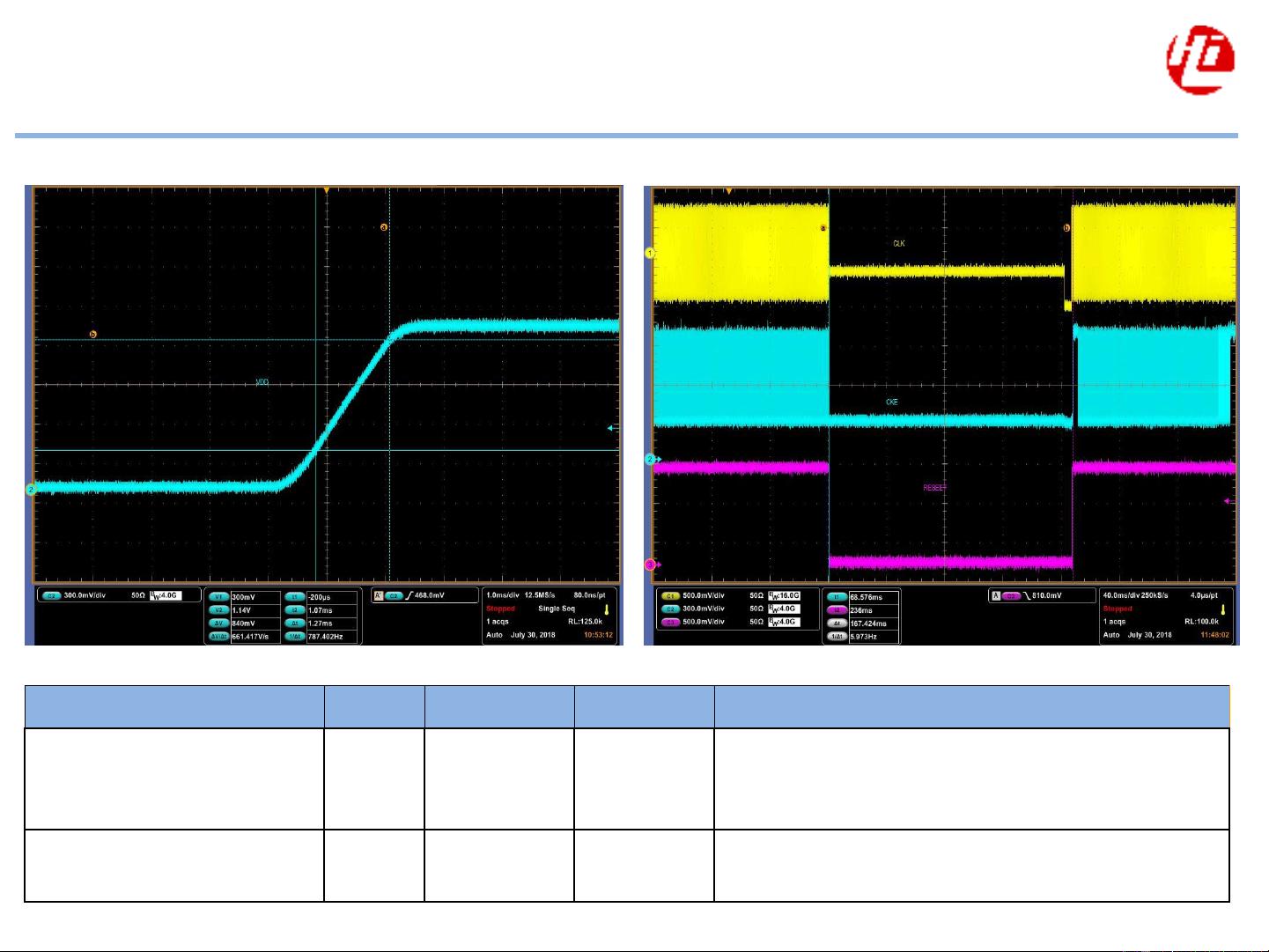

Hi3519AV100是一款芯片组,与Hi3519AV100DMEBLITEVER.A主板配合,使用三星K4A8G165WB-BITD型号的16位DRAM。测试使用了DAS72004C Tektronix数字示波器,环境条件保持在常温下,DRAM工作频率为1332MHz,电压设置为VPP/Vdd/Vref-CA/Vcore分别为2.5V/1.2V/0.6V/0.8V。此外,报告提供了详细的电阻值,如DRAM_RON为48ohm,SOC_RON在不同时钟周期有所不同。

报告的重点部分是信号完整性测试结果,包括DQWriteBurst眼图测试。测试中观察到DQS/DQ边沿存在台阶和回沟现象,导致tWPSTFail,这可能是由于测试点位置不合理,放大了信号线反射误差,以及测试设备带宽和负载电容对信号边沿产生的影响,使波形失真。然而,通过SI仿真,发现芯片内部Pad上的DQS/DQ信号正常,无明显缺陷,而且DQTraining总窗口的余量充足,经过长时间高低温环境实验,未发现异常。

针对这些情况,综合评估认为,虽然DQWriteBurst眼图测试中出现了异常,但这是由于测试条件导致的,而非芯片本身的问题,因此没有实际风险。接下来,报告还提到了Address/Command指标的测试结果,这部分内容同样关注信号的准确性和一致性,但具体细节和结论并未在这部分给出,可能需要结合其他相关测试结果进行分析。

这份报告提供了一个关于Hi3519AV100 DDR4x16 Flyby Signal Integrity的详尽评估,帮助用户了解在特定条件下,芯片的信号性能表现和潜在问题,以便做出相应的设计和优化决策。

2021-05-07 上传

2021-11-27 上传

2020-05-27 上传

2020-10-30 上传

2021-05-07 上传

2020-05-27 上传

2020-06-24 上传

2020-05-27 上传

陈玉辉-沈阳

- 粉丝: 1

- 资源: 22

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍