Quartus FFT IP Core 使用指南:BurstData模式下256点FFT运算

"该资源是关于在Quartus软件中使用FFT IP Core的教程,特别提到了在处理fft运算时的一些关键步骤和注意事项。"

在Quartus集成开发环境中,FFT IP Core是一种方便的硬件加速模块,用于执行快速傅里叶变换(FFT)计算。这个IP核对于需要高效处理 FFT 运算的 FPGA 应用来说非常有用。然而,正确使用这个IP Core并不总是直观的,尤其是在设置仿真时间和处理输入信号方面。

首先,确保为仿真设定足够的时间以获得正确的结果。由于FFT操作通常涉及多个数据帧的处理,因此至少需要设定3-4帧的仿真时间,以便IP Core能够完成其计算。这可以通过增加仿真时间步长或在仿真脚本中设置来实现。

其次,理解和正确管理FFT IP Core的输入信号至关重要。有三个关键的输入信号需要关注:

1. sink_sop:标记每个帧的首个数据。

2. sink_eop:标记每个帧的最后一个数据。

3. sink_valid:当帧中的数据有效时,该信号应置为高电平。

这两个信号可以通过状态机或计数器来生成,以满足IP Core对输入序列的期望格式。状态机可以更灵活地处理各种输入序列,而计数器则适用于简单且固定的数据帧结构。

在使用FFT IP Core时,有多种工作模式可供选择。其中,"burstdata"模式是最节省资源的,但它可能需要更长的处理时间。在这个例子中,作者选择了burstdata模式来演示256点的FFT运算,并使用Quartus II 8.0 SP1以及ModelSim SE Plus 6.4作为仿真工具。

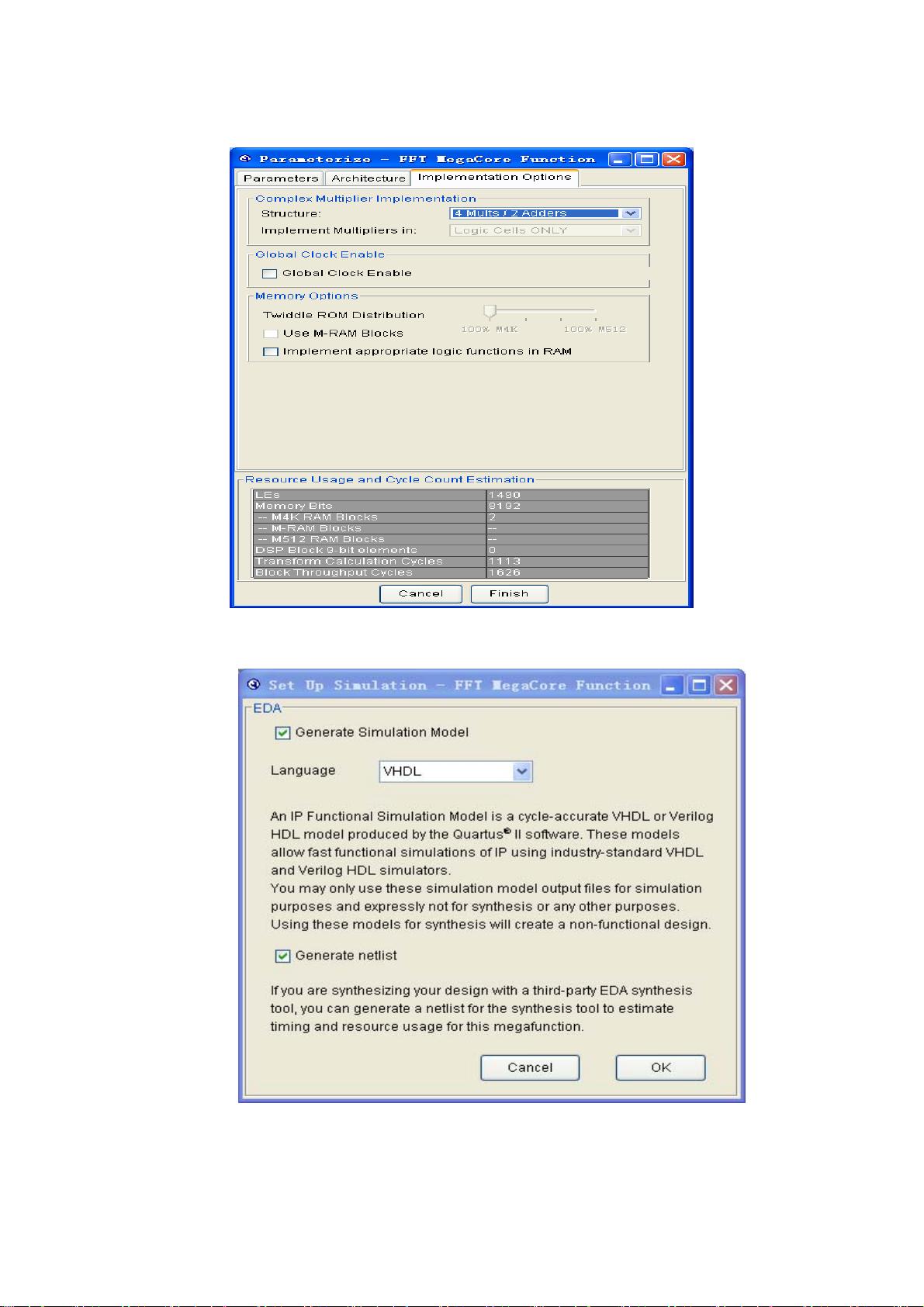

设置FFT IP Core的过程包括:

1. 新建工程,选择合适的器件,例如Cyclone系列的EP1C3T144C8。

2. 使用Merge Wizard Plug-in Manager配置FFT参数,如器件选择、变换长度、FFT引擎架构、数据流方式等。

3. 设定仿真选项,包括是否生成网列表,这对于非正式的验证阶段可能不必要。

4. 编写控制逻辑,如状态机(ctrl_fft.vhd),以生成sink_sop、sink_eop和sink_valid等信号。

通过以上步骤,用户可以成功地在Quartus环境中集成和使用FFT IP Core进行高效的FFT运算。需要注意的是,每个项目可能有不同的需求,因此在实际应用中可能需要根据具体的系统需求进行调整和优化。

470 浏览量

2904 浏览量

207 浏览量

2021-10-12 上传

220 浏览量

293 浏览量

2023-09-22 上传

292 浏览量

397 浏览量

呈叙墨客

- 粉丝: 57

最新资源

- 网狐工具:核心DLL和程序文件解析

- PortfolioCVphp - 展示JavaScript技能的个人作品集

- 手机归属地查询网站完整项目:HTML+PHP源码及数据集

- 昆仑通态MCGS通用版S7400父设备驱动包下载

- 手机QQ登录工具的压缩包内容解析

- Git基础学习仓库:掌握版本控制要点

- 3322动态域名更新器使用教程与下载

- iOS源码开发:温度转换应用简易教程

- 定制化用户登录页面模板设计指南

- SMAC电机在包装生产线应用的技术案例分析

- Silverlight 5实现COM组件调用无需OOB技术

- C#实现多功能画图板:画直线、矩形、圆等

- 深入探讨C#语言在WPF项目开发中的应用

- 新版2012109通用权限系统源码发布:多角色用户支持

- 计算机科学与工程系网站开发技术源码合集

- Java实现简易导出Excel工具的开发教程