FPGA实现误码仪:逐位比较法与移位寄存器法

113 浏览量

更新于2024-09-04

1

收藏 806KB PDF 举报

"基于FPGA的误码仪设计利用了EPF10KRC208-4 FPGA和Quartus Ⅱ软件,具备便携、精准测量等特点。设计核心采用逐位比较法和移位寄存器法,通过仿真分析方案可行性和方法优缺点。"

本文探讨的是在信息技术快速发展背景下,如何利用FPGA(Field-Programmable Gate Array)技术设计一种高效的误码仪,以评估通信系统在复杂战场环境中的性能。误码仪是通信系统中关键的测试设备,能够检测并统计传输数据中的错误,确保信息传输的可靠性。

设计中选用的FPGA型号为EPF10KRC208-4,这是一款具有强大可编程能力和丰富资源的芯片。配合Altera公司的开发软件Quartus Ⅱ,可以实现逻辑分析、功率分析、时序优化等多种功能,简化设计流程,提高设计效率。

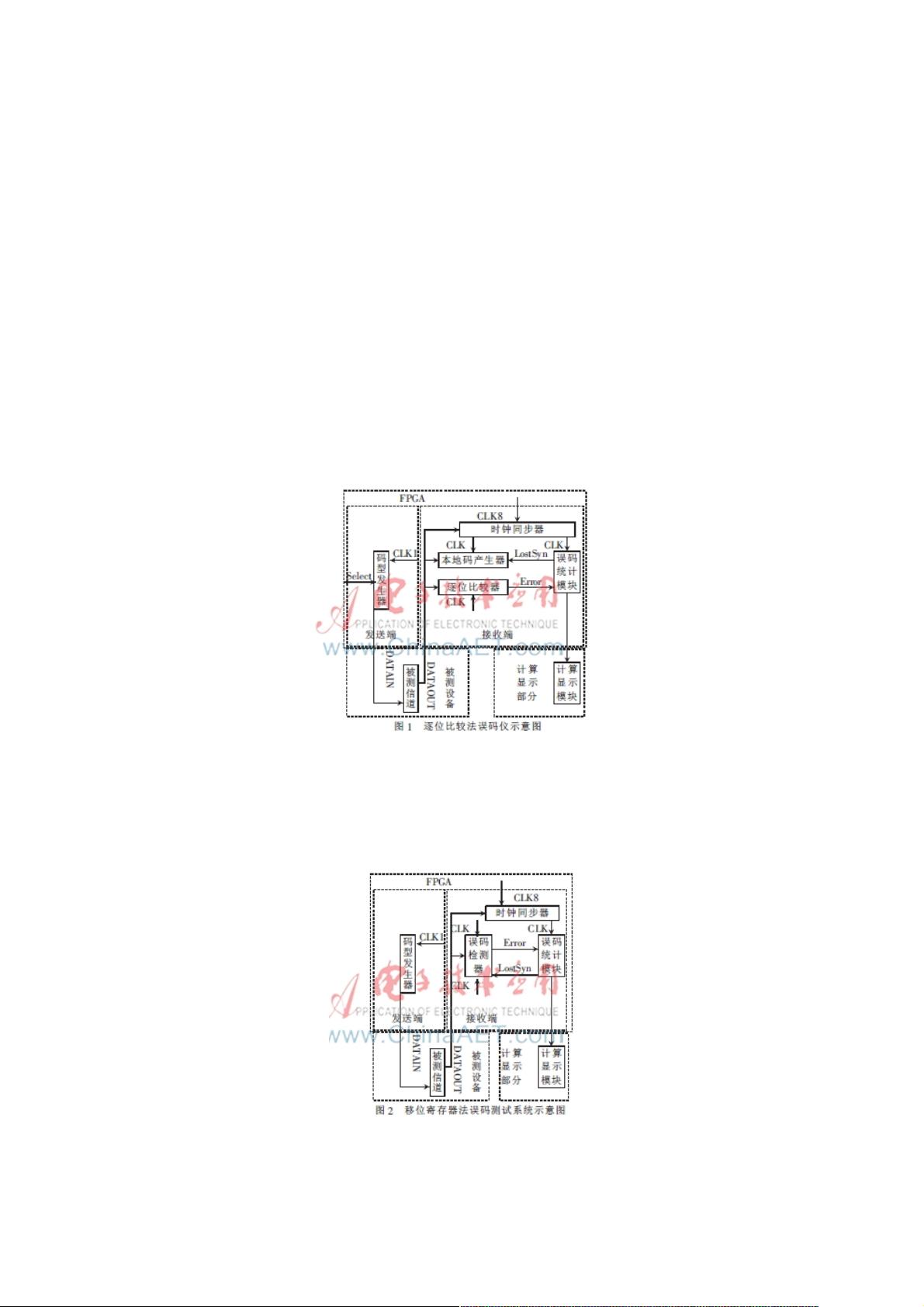

设计的核心部分包括两种误码检测方法:逐位比较法和移位寄存器法。逐位比较法误码仪由发送和接收两部分构成,发送端生成测试码,接收端则通过时钟同步器、本地码产生器、逐位比较器和误码统计模块来比较和分析接收到的数据。这种方法简单易行,但可能对干扰较为敏感。

移位寄存器法则有所不同,发送端同样生成测试码,但接收端仅需时钟同步器、误码检测器和误码统计模块。这种方法通过m序列进行误码检测,无需本地码产生器,提高了抗干扰能力,但可能需要更复杂的同步机制以避免数据丢失。

在仿真过程中,两种方法均被设置在多种误码情况下运行,以全面评估其性能。通过对仿真结果的分析,可以得出每种方法的优缺点,为实际应用提供依据。逐位比较法的优势在于结构直观,而移位寄存器法则在抗干扰性能上有优势,但设计相对复杂。

总结来说,基于FPGA的误码仪设计提供了灵活且高效的数据检测解决方案,对于通信系统性能评估和优化具有重要意义。通过结合FPGA的可编程性以及现代通信技术,我们可以构建出适应不同需求的误码检测工具,以应对不断演进的通信挑战。

153 浏览量

2021-07-13 上传

168 浏览量

2024-10-19 上传

255 浏览量

513 浏览量

2024-11-24 上传

177 浏览量

weixin_38571878

- 粉丝: 5

- 资源: 935

最新资源

- jdk-11.0.6_windows-x64_bin.exe

- 接近客户的技巧——电话接近客户的技巧

- apsiyon-test-study

- i-sport:本学期的微信小程序期末设计,一种为喜爱运动健身人士所设计的APP

- goit-js-hw-07

- taskboard-ui

- Impellent.Developer.Tools:我自己的开发者工具的集合

- umodel_win32.zip

- 新人衔接教育30天销售实务培训班主任手册

- FORTE11.rar

- elex:对网关列表执行选举速度检查,以找到最快的网址

- win10打印机安装软件,一键配置ip打印

- pta_sim:PTA模拟代码存储库

- archive.cheesits456.dev:我网站的旧版本

- hello-world

- 客户服务与经营